IGBT device with a groove gate type JFET structure

A grooved gate and gate structure technology, which is applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of reducing the turn-off capability of the device, increasing the turn-off loss of the device, and damaging the breakdown voltage of the device. , to reduce the saturated turn-on voltage drop and turn-off loss, reduce the gate resistance, and improve the turn-off capability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

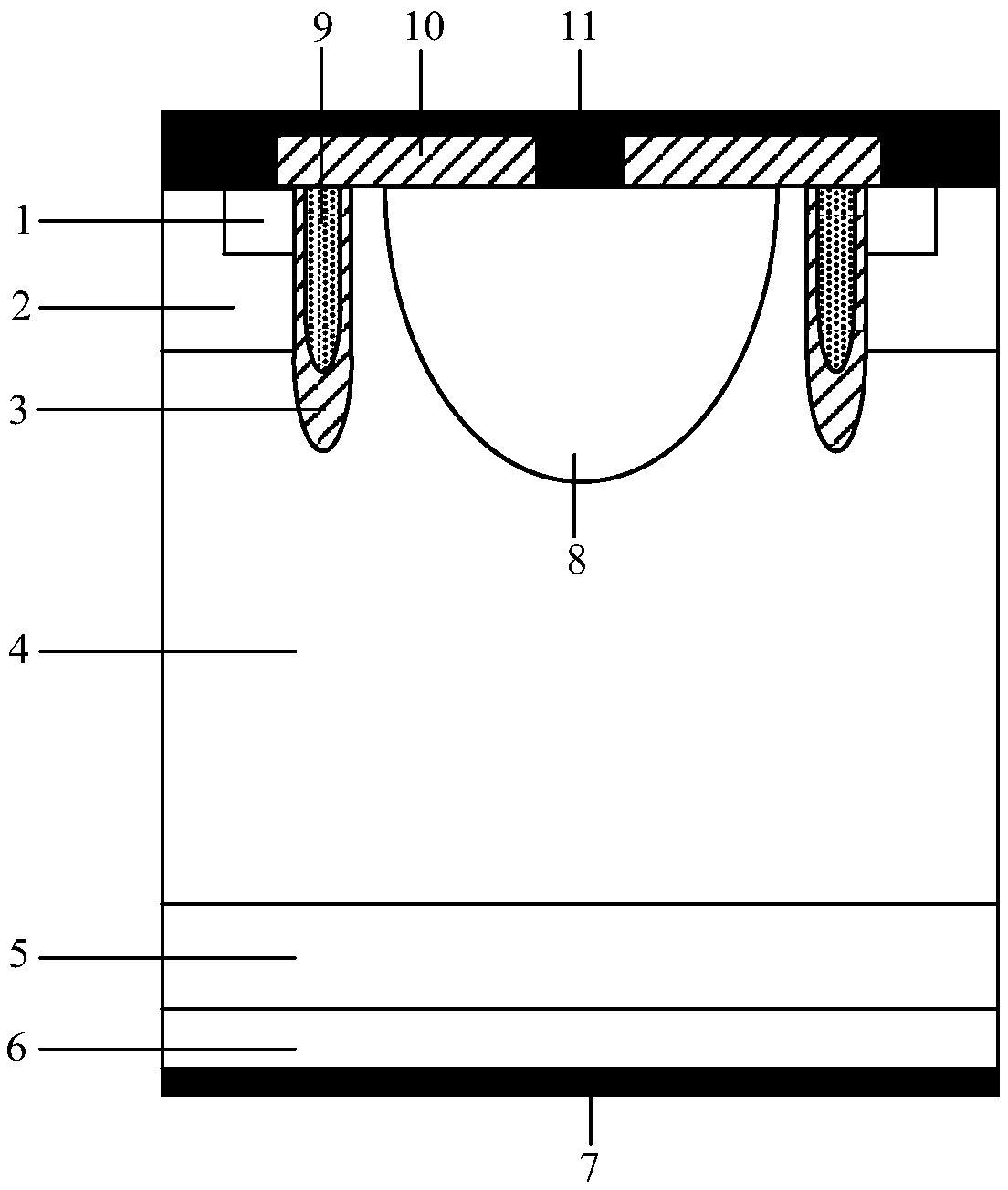

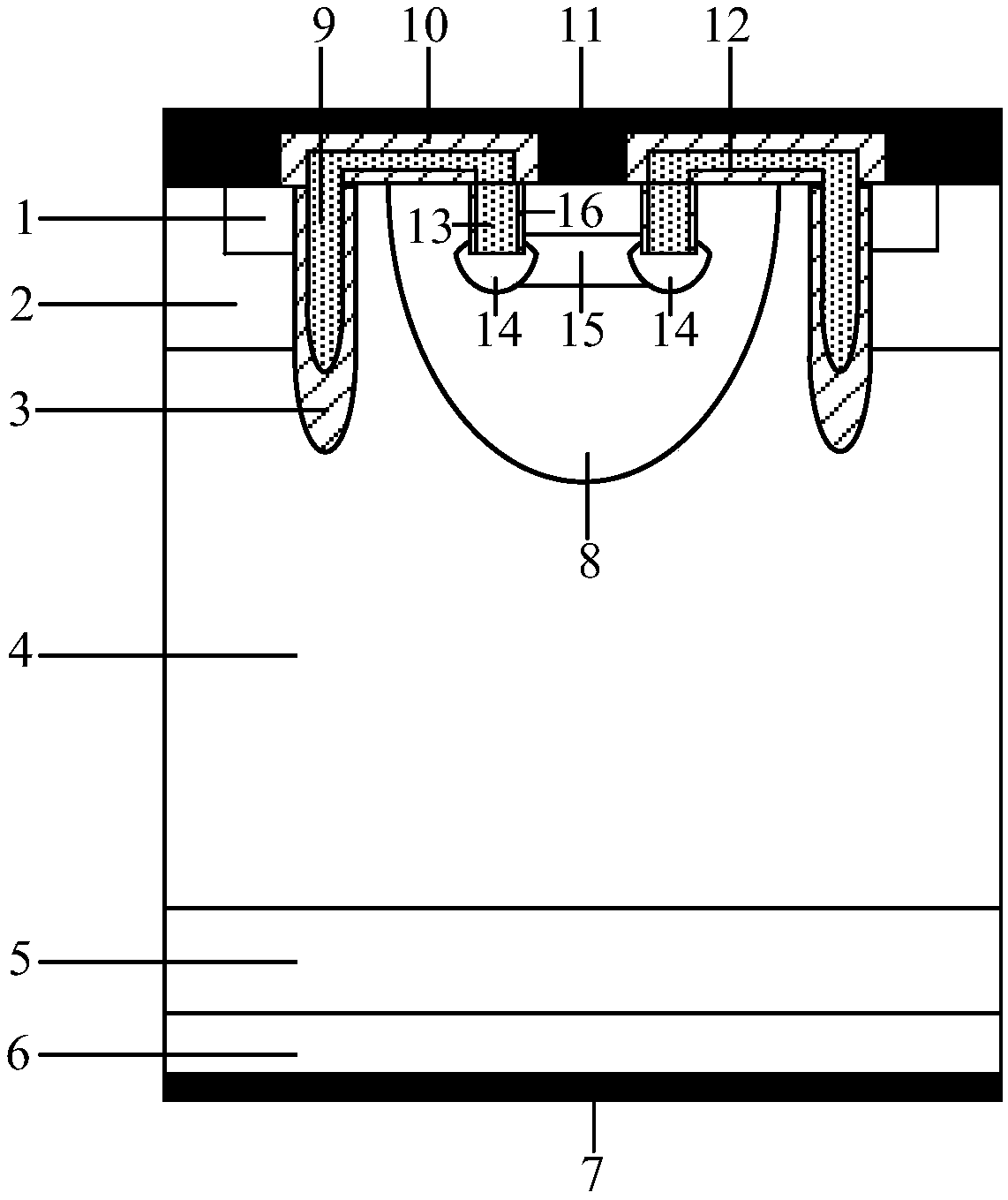

[0029] An IGBT device with a groove gate JFET structure, such as figure 2As shown, its cellular structure includes a metal collector 7, a first conductivity type semiconductor collector region 6, a second conductivity type semiconductor buffer layer 5, a second conductivity type semiconductor drift region 4, and a metal emitter stacked sequentially from bottom to top. pole 11; the top layer of the second conductivity type semiconductor drift region 4 has a first conductivity type semiconductor body region 8, a first conductivity type semiconductor base region 2, a second conductivity type semiconductor emitter region 1 and a first gate structure; The first conductivity type semiconductor body region 8 is located in the middle region of the top layer of the second conductivity type semiconductor drift region 4; the first conductivity type semiconductor base region 2 is respectively located in the regions on both sides of the second conductivity type semiconductor drift region 4...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More