Enhanced transistor based on III oxide passivation and manufacturing method of enhanced transistor

A production method and oxide technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of reducing saturation current and reducing the concentration of two-dimensional electron gas affecting the channel, so as to reduce on-resistance, The effect of optimized processing method and excellent high temperature stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

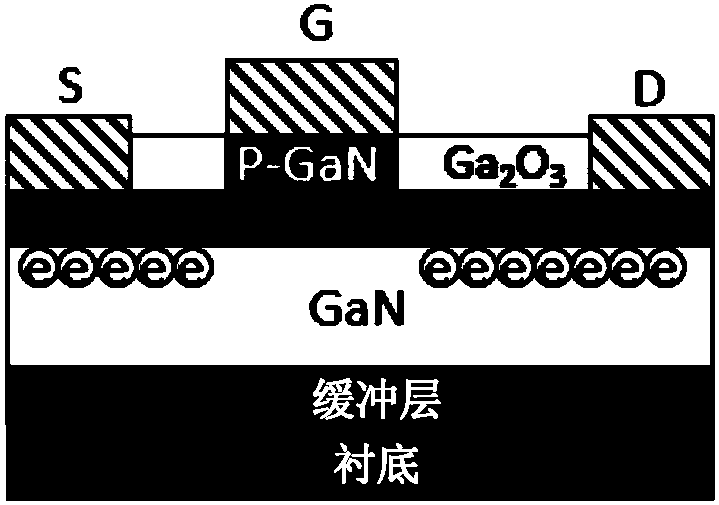

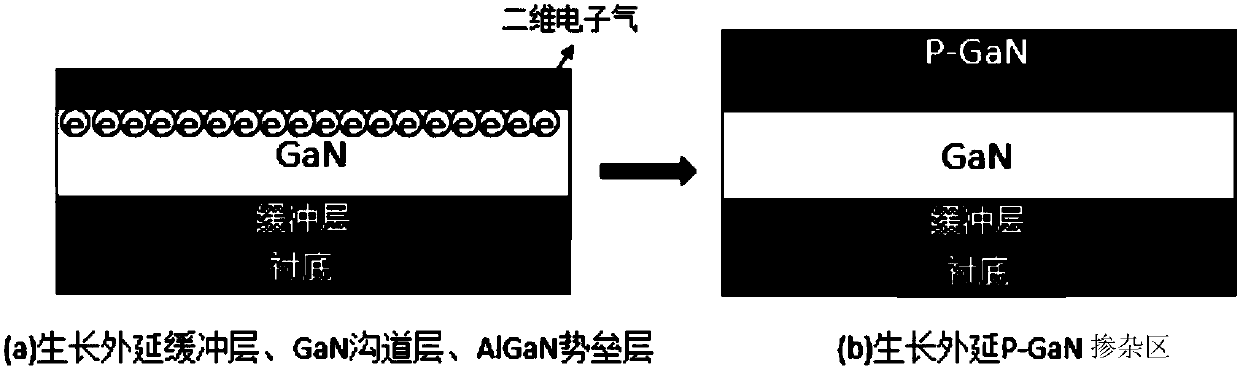

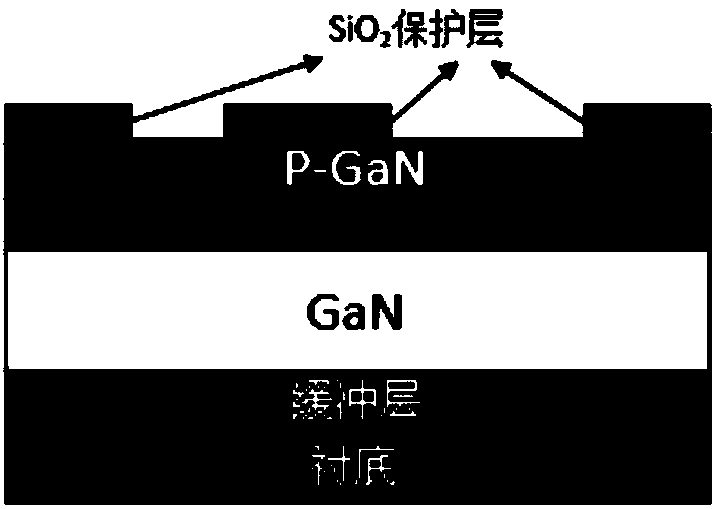

[0054] In view of the deficiencies in the prior art, the inventor of this case has been able to propose the technical solution of the present invention after long-term research and extensive practice, which mainly uses oxidation or other techniques to transform the P-type doped region of the non-gate region into a Ш group oxidation The P-type doped region in the region under the gate is reserved, so as to realize the transistor in the P-type capping layer enhanced mode of operation.

[0055] Specifically, the present invention adopts P-type doped region cap layer / AlGaN barrier layer / GaN channel layer / base (or P-type doped region cap layer / AlGaN barrier layer / AlN / GaN channel layer / base, etc. Similar structure) material structure, the P-type doped region in the non-gate region is changed into a Ш group oxide by oxidation or other methods, the P-type doped region in the region under the gate is retained, and the two-dimensional electron gas of the channel layer is depleted ( 2DEG...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More