Integrated I2C interface verification controller design method based on FPGA

A design method and controller technology, applied in the direction of instruments, electrical digital data processing, etc., can solve the problems of manpower, waste of time resources, lack of independence, structuring, difficult logic structure reuse, etc., to achieve verification adequacy and efficiency The effect of improving, improving configurability, and shortening the construction cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The present invention will be further described below in conjunction with accompanying drawing:

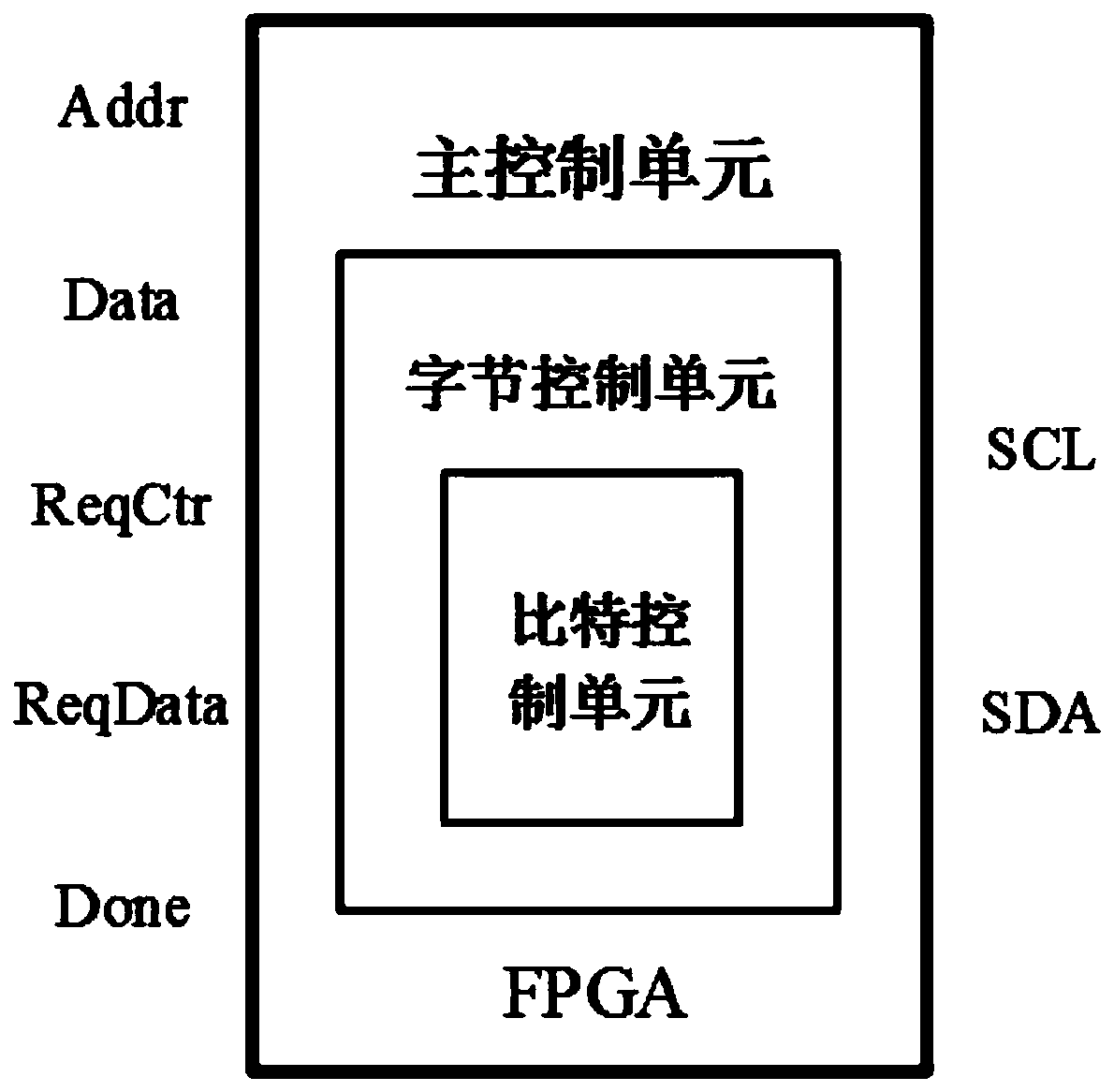

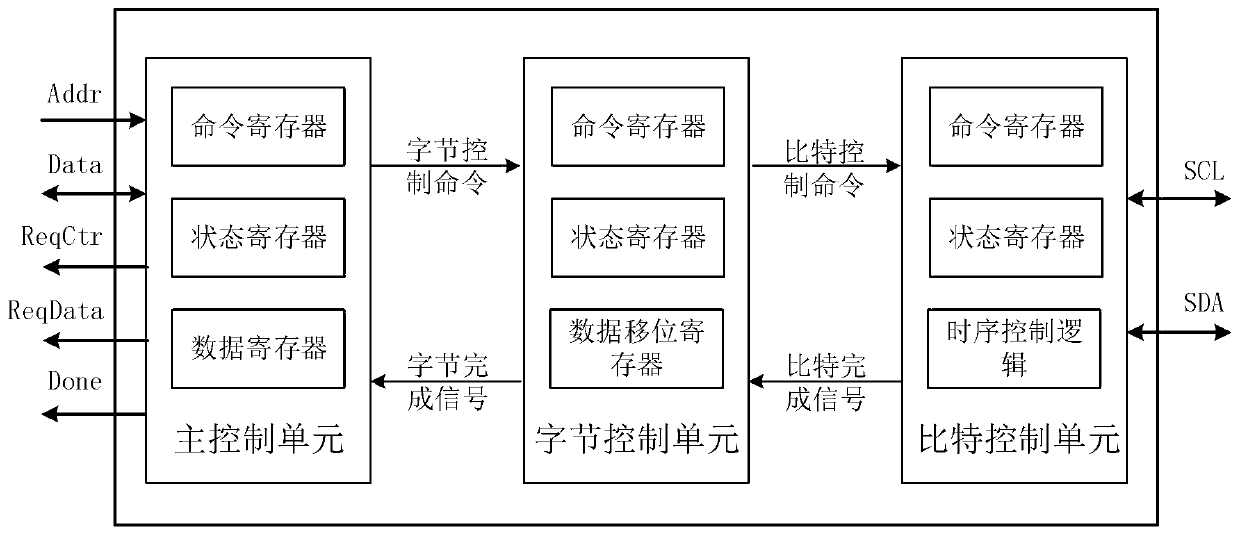

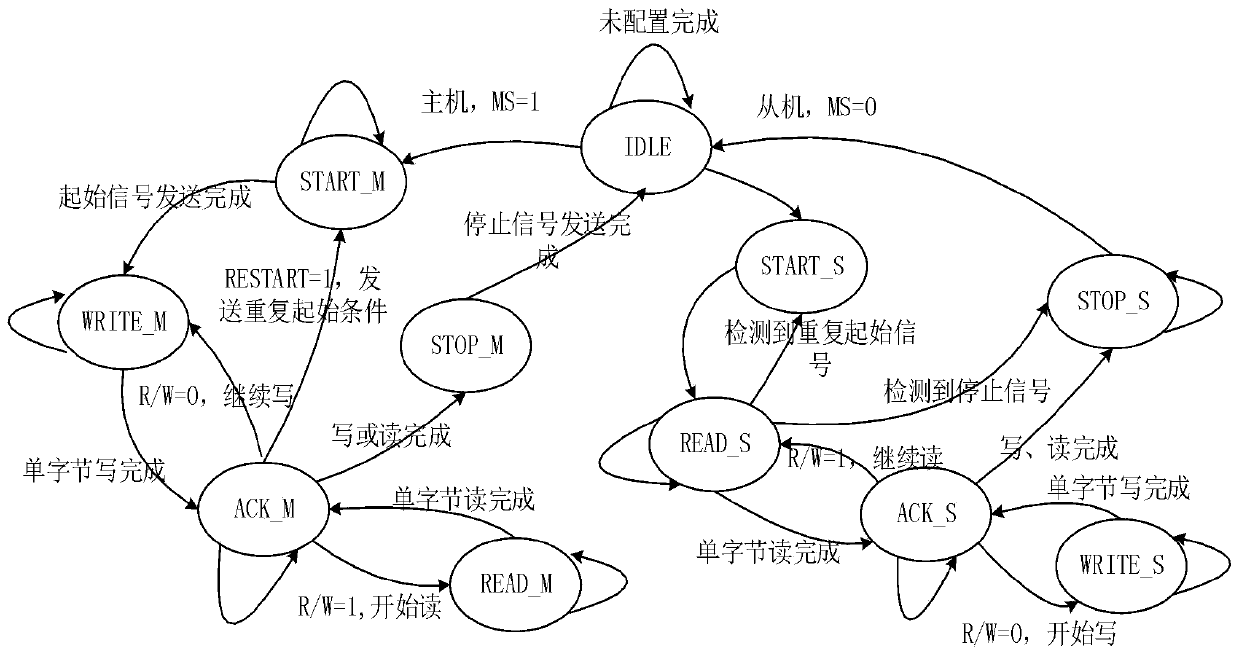

[0034] Such as figure 1 As shown, the FPGA-based integrated I2C interface verification controller design method of the present invention, the verification controller is developed based on FPGA, and adopts the master-slave integrated design architecture; the master-slave integrated design architecture is passed through the I2C The communication process is layered and abstracted, and the I2C communication master and slave are integrated to realize the unified packaging of the external interface of the verification controller and the hierarchical design of the internal structure. Signals that are strongly related to the communication process are exposed outside the verification controller. Based on the principle of minimization, the topmost weakly related signals are packaged as the external interface of the verification controller. In order to reduce design complexity and imp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com