A PLL Based on Preset Frequency and Dynamic Loop Bandwidth

A preset frequency and phase-locked loop technology, applied in the automatic control of power, electrical components, etc., can solve the problems affecting the overall power consumption and occupation of the chip, and achieve the effect of eliminating noise and high resolution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0057] A phase-locked loop based on a preset frequency and a dynamic loop bandwidth can be applied to a fast output frequency locking circuit to reduce the overall overall power consumption of the circuit.

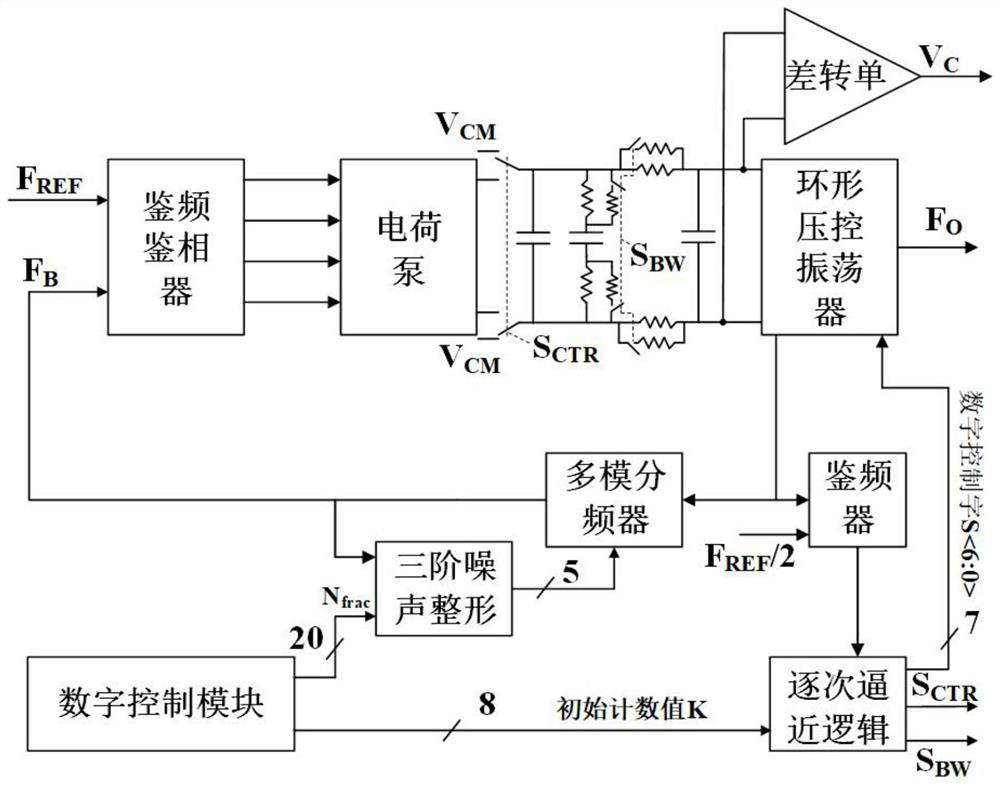

[0058] The block diagram of the present invention is as figure 1 As shown, the fast locking of the phase-locked loop is realized based on the preset frequency and dynamic loop bandwidth technology, which mainly includes a fully differential frequency detector PFD, a fully differential charge pump CP, a ring voltage controlled oscillator Ring VCO, a multi-mode Frequency divider MMD and low pass filter LPF.

[0059] The frequency and phase detector PFD is a fully differential structure, called a fully differential frequency and phase detector, which is implemented by static CMOS to reduce the overall power consumption of the system;

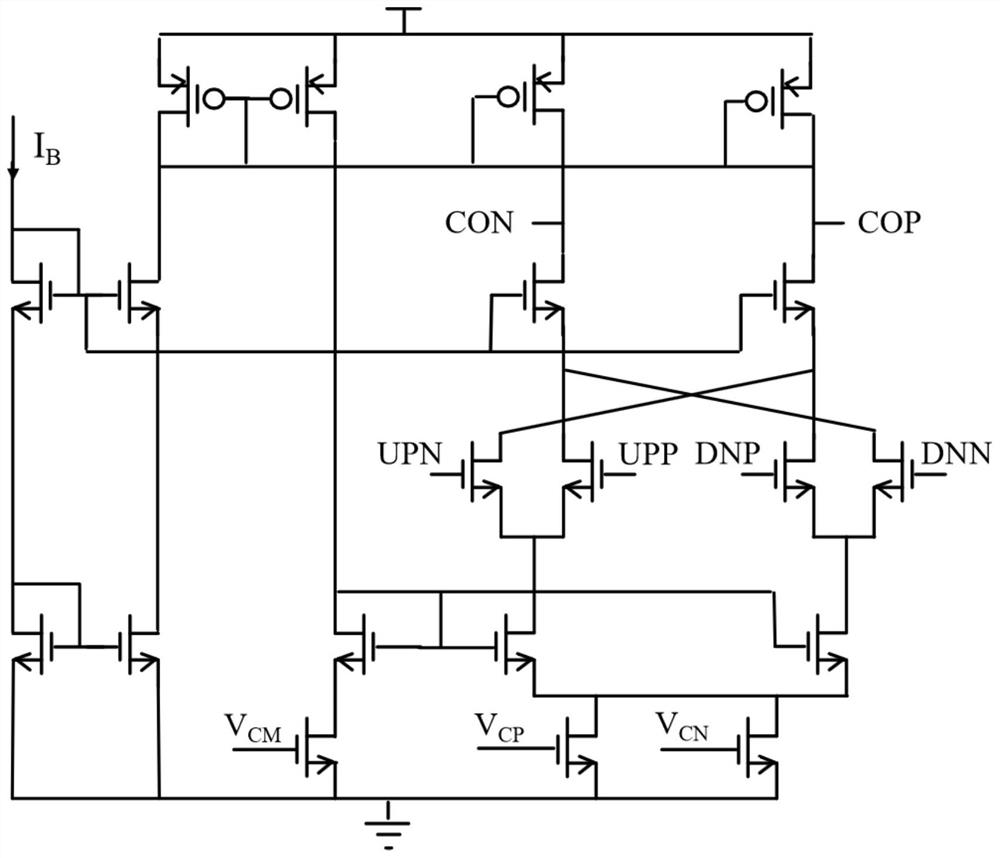

[0060] Among them, the charge pump CP is implemented with a fully differential static CMOS structure, which is called a fully differential ch...

Embodiment 2

[0090] The phase-locked loop establishment process described in this application is made up of frequency tracking and phase locking, first realizes frequency locking and then realizes phase locking, and its total establishment time is as formula (1)

[0091]

[0092] where BW is the loop bandwidth of the PLL.

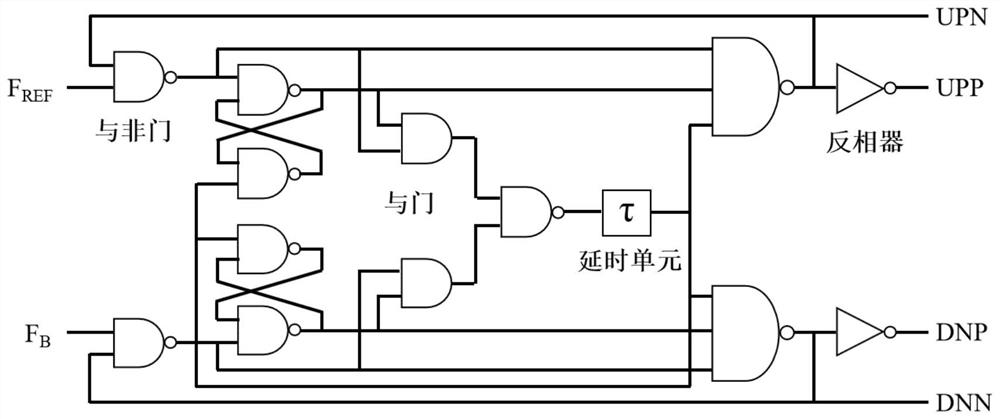

[0093] The structure of the phase frequency detector PFD is as follows figure 2 shown. The combinational logic circuit composed of NAND gate and D flip-flop will instantaneously compare the reference frequency F REF and feedback frequency F B phase to realize the function of charging and discharging. At the same time, in order to eliminate the dead zone characteristics of the charge pump and the noise caused by the dynamic current mismatch of the charge pump, a delay link is introduced to eliminate it, so as to ensure that the value of the delay link is the smallest when the charge pump is fully turned on, and a higher operating efficiency can be obtained. frequ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More