Semiconductor structure and formation method thereof

A semiconductor and regional technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of LDMOS withstand voltage performance to be improved, and achieve the effect of extending length, improving withstand voltage performance, and reducing voltage gradient

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] It can be seen from the background art that after the fin field effect transistor is introduced into the LDMOS, the withstand voltage performance of the LDMOS needs to be improved. Combining with a semiconductor structure, the reason why its withstand voltage performance needs to be improved is analyzed.

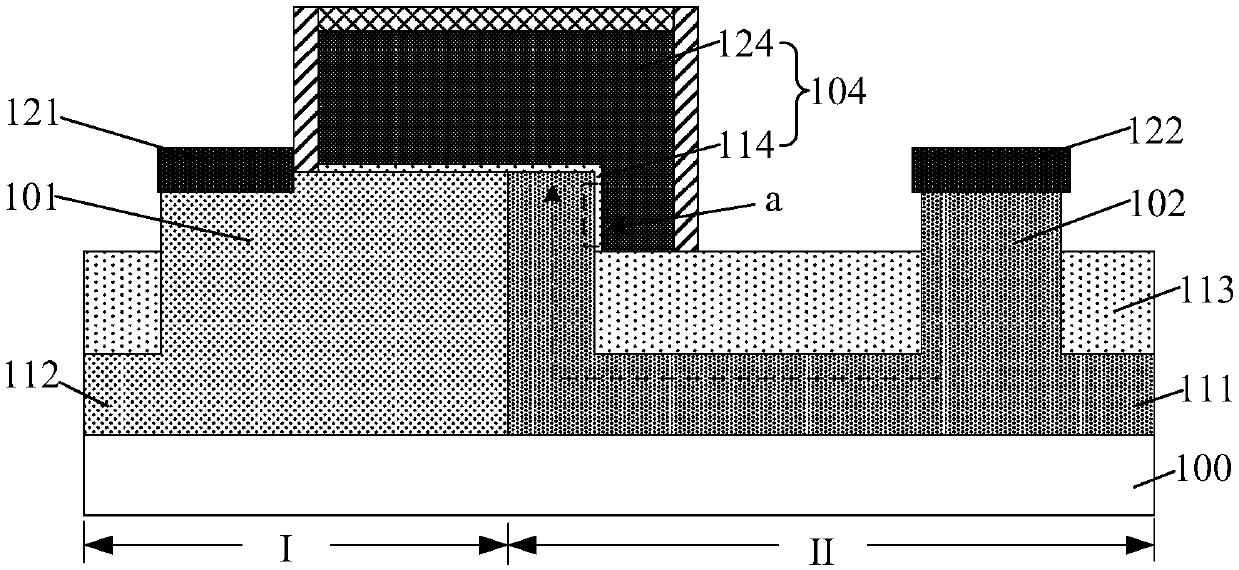

[0017] refer to figure 1 , shows a schematic structural view of a semiconductor structure.

[0018] The semiconductor structure includes: a substrate 100, a fin (not marked) protruding from the substrate 100, and the substrate 100 includes a first region I and a second region II adjacent to each other, located in the second region The fin at the junction of the first region I and the second region II is the first fin 101, the fin located in the second region II is the second fin 102; the well region 112, the fin located in the first region I part and the substrate 100; the drift region 111 is located in the fin part of the second region II and the substrate 100; the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More