Ultraviolet LED chip and manufacturing method thereof

A technology of LED chip and manufacturing method, applied in ion implantation plating, coating, electrical components and other directions, can solve problems such as affecting the light output efficiency of ultraviolet LED chips, and achieve the improvement of current expansion capability, reliability, and voltage reduction. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

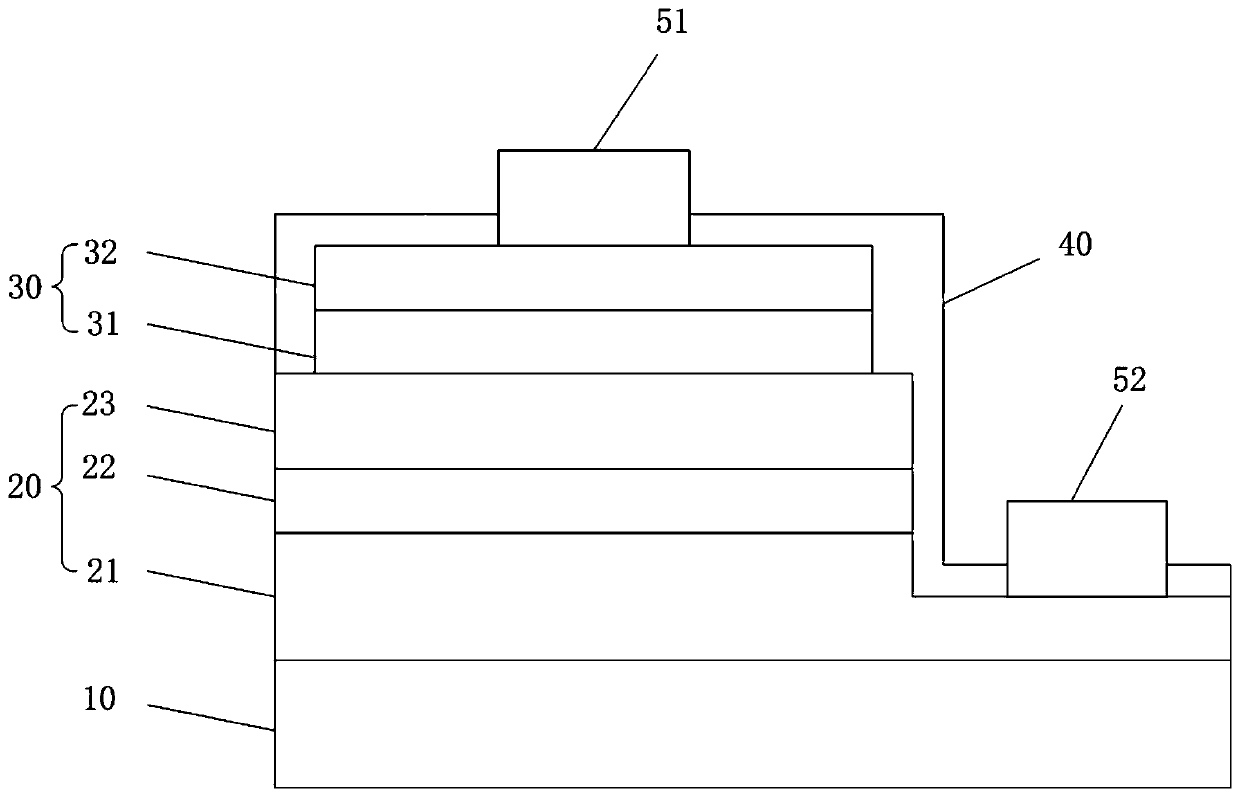

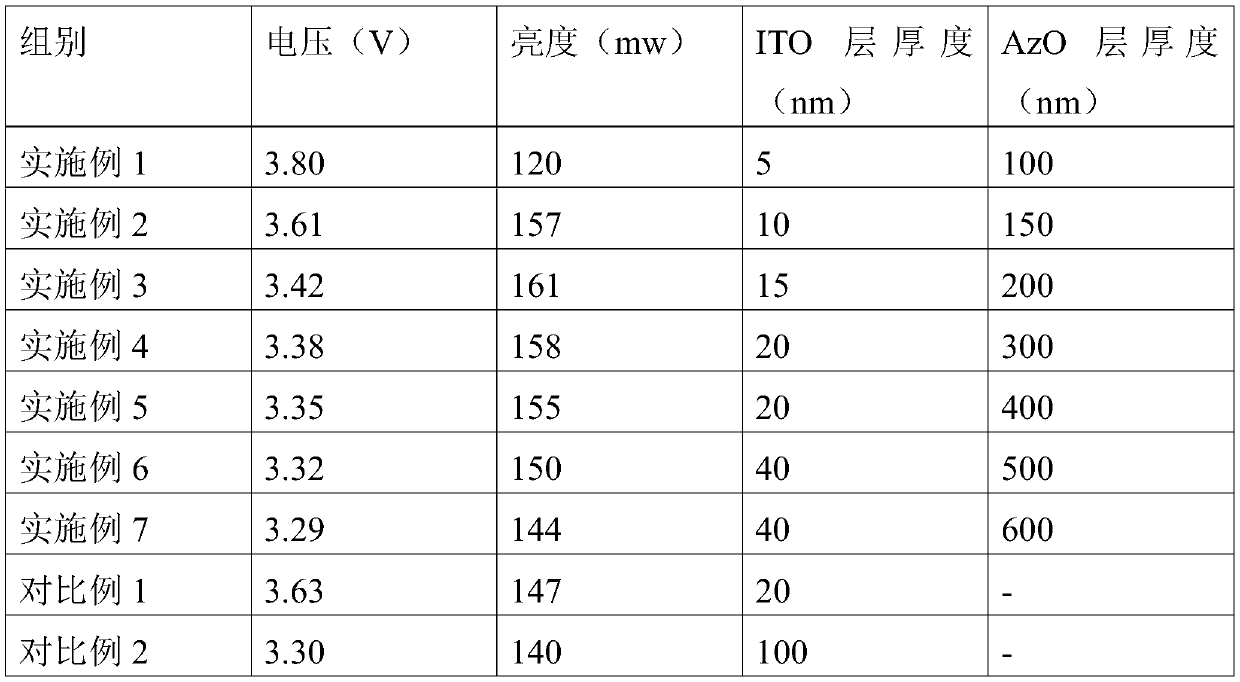

[0062] An ultraviolet LED chip comprises a substrate, an epitaxial layer arranged on the substrate, a transparent conductive layer and an electrode structure arranged on the epitaxial layer, and a protective layer covering the transparent conductive layer and the epitaxial layer.

[0063] The transparent conductive layer includes an ITO layer and an AzO layer, the ITO layer is arranged between the second semiconductor layer and the AzO layer, the thickness of the ITO layer is 5nm, the thickness of the AzO layer is 100nm, and the protective layer Made of boron nitride, 20nm thick.

Embodiment 2

[0065] An ultraviolet LED chip comprises a substrate, an epitaxial layer arranged on the substrate, a transparent conductive layer and an electrode structure arranged on the epitaxial layer, and a protective layer covering the transparent conductive layer and the epitaxial layer.

[0066] The transparent conductive layer includes an ITO layer and an AzO layer, the ITO layer is arranged between the second semiconductor layer and the AzO layer, the thickness of the ITO layer is 10nm, the thickness of the AzO layer is 150nm, and the protective layer Made of boron nitride, 50nm thick.

Embodiment 3

[0068] An ultraviolet LED chip comprises a substrate, an epitaxial layer arranged on the substrate, a transparent conductive layer and an electrode structure arranged on the epitaxial layer, and a protective layer covering the transparent conductive layer and the epitaxial layer.

[0069] The transparent conductive layer comprises an ITO layer and an AzO layer, the ITO layer is arranged between the second semiconductor layer and the AzO layer, the thickness of the ITO layer is 15nm, the thickness of the AzO layer is 200nm, and the protective layer Made of boron nitride, 50nm thick.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More