Microelectronic packages, flip-chip technology and its application, microelectronic devices

A technology of microelectronic package and process, which is applied in the manufacture of electric solid-state devices, semiconductor devices, semiconductor/solid-state devices, etc., can solve problems affecting the electrical performance of chips, single chip curing, model distortion, etc., to reduce the difficulty of matching, Effect of improving bonding strength and encapsulation efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] Embodiments of the present invention will be described in detail below in conjunction with examples, but those skilled in the art will understand that the following examples are only for illustrating the present invention, and should not be considered as limiting the scope of the present invention. Those who do not indicate the specific conditions in the examples are carried out according to the conventional conditions or the conditions suggested by the manufacturer.

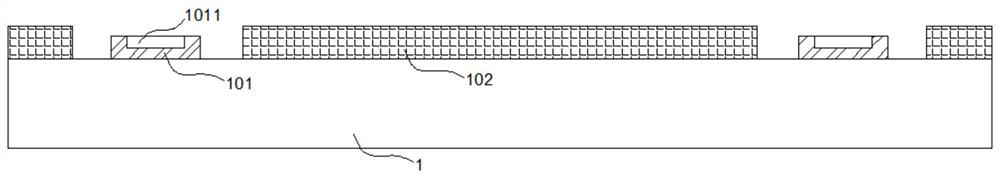

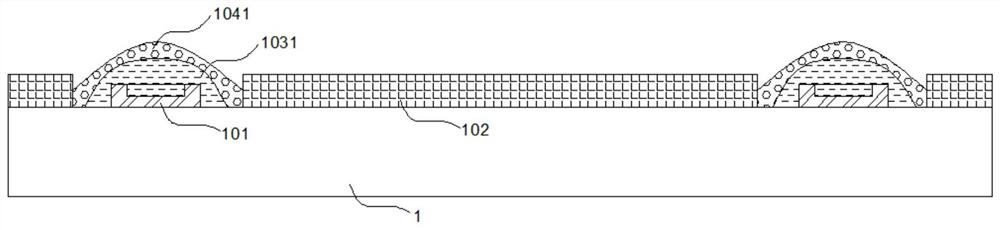

[0043] According to one aspect of the present invention, there is provided a microelectronic package, such as figure 1 As shown, including a substrate 1 and a chip 2, a conductive block 101 is arranged on the substrate 1, a conductive adhesive layer 103 and a non-conductive adhesive layer 104 are arranged on the surface of the conductive block 101 in turn, and a bump 201 is arranged on the chip 2, and the bump 201 presses fit over the conductive block 101.

[0044] The above-mentioned microelectronic pac...

PUM

| Property | Measurement | Unit |

|---|---|---|

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More