Semiconductor power device structure and manufacturing method thereof

A technology of power devices and manufacturing methods, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., to reduce the risk of leakage current, simplify the process flow, and simplify the process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

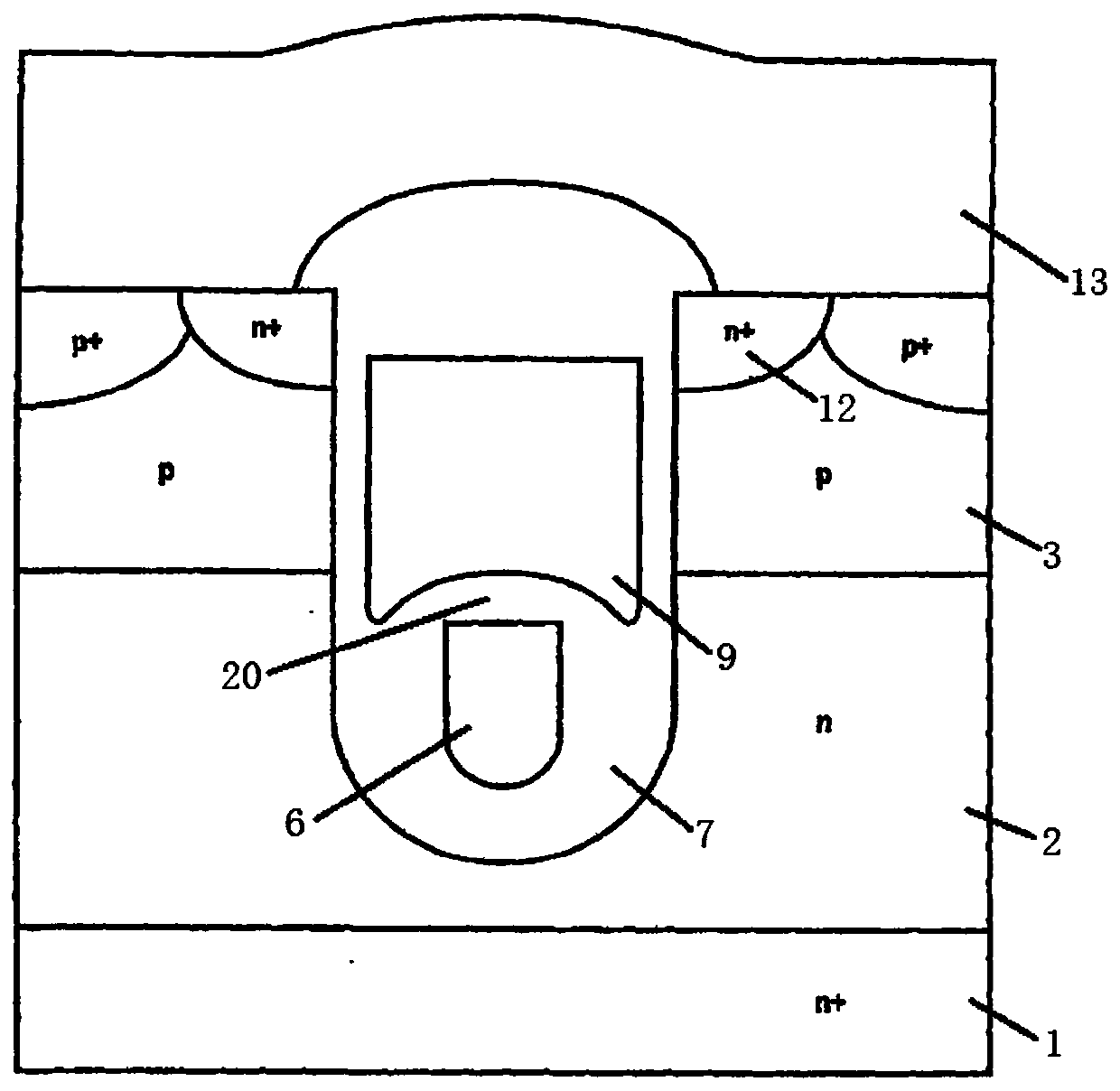

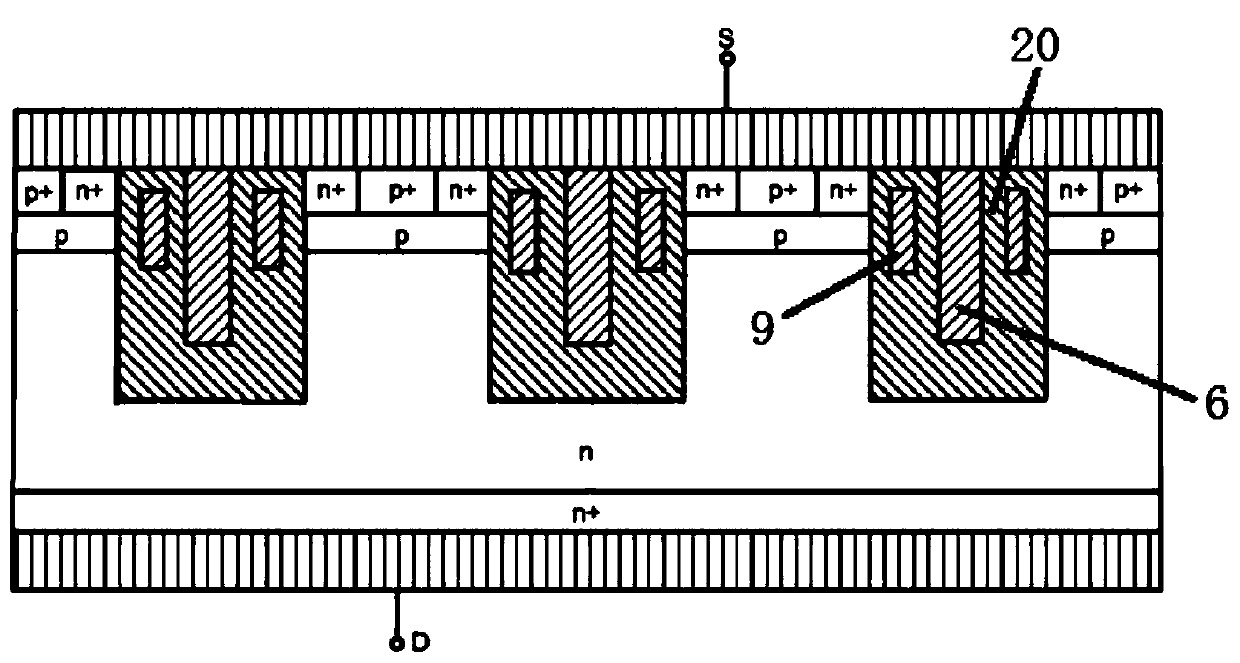

[0056] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0057] Figure 3A to Figure 3Q A method for manufacturing a semiconductor power device structure according to an embodiment of the present invention is shown, including the following steps:

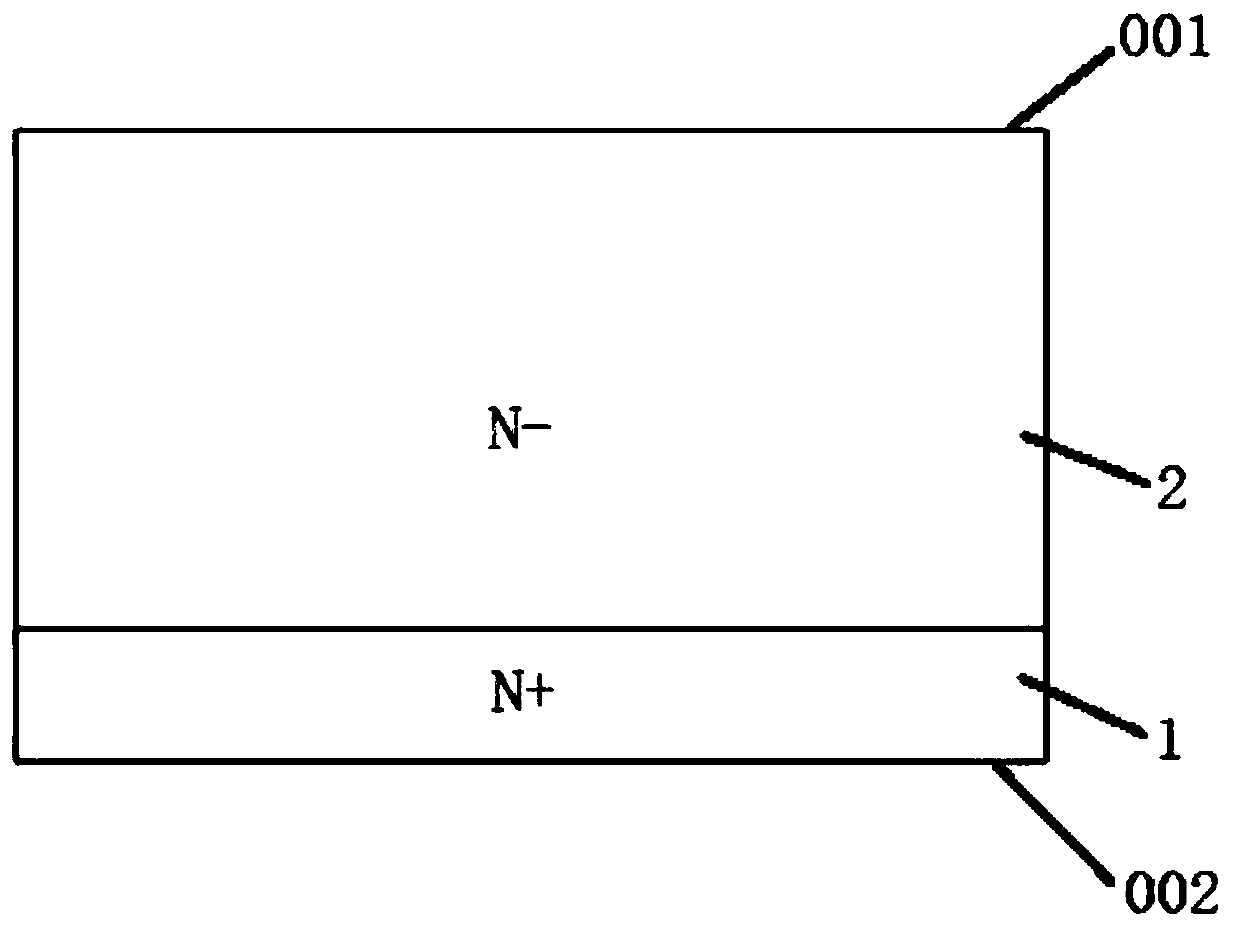

[0058] Step 1, such as Figure 3A As shown, a heavily doped N+ type substrate 1 is selected, and a lightly doped N-type epitaxial layer 2 is formed on the N+ type substrate 1, and the upper surface of the N-type epitaxial layer 2 is the first main surface 001 , and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More