Embedded chip package and manufacturing method thereof

An embedded chip and chip packaging technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as easy peeling, reduced lifespan, and long operation process, so as to simplify the process steps and avoid damage Risk, the effect of reducing production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

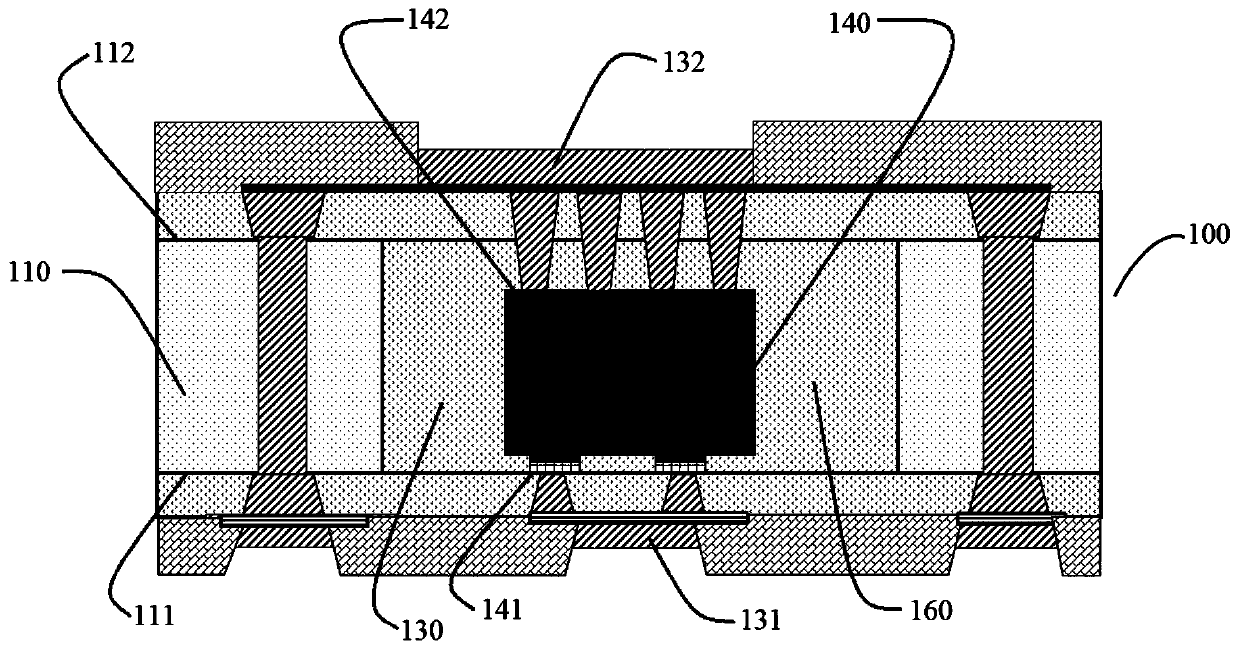

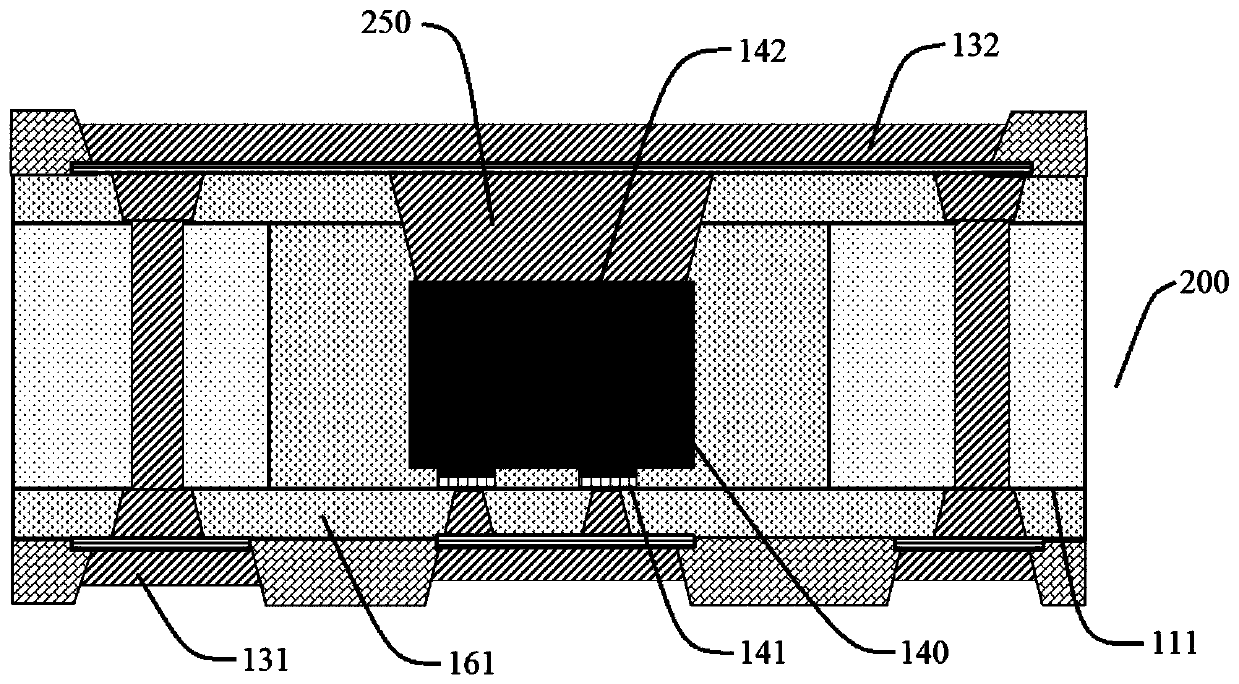

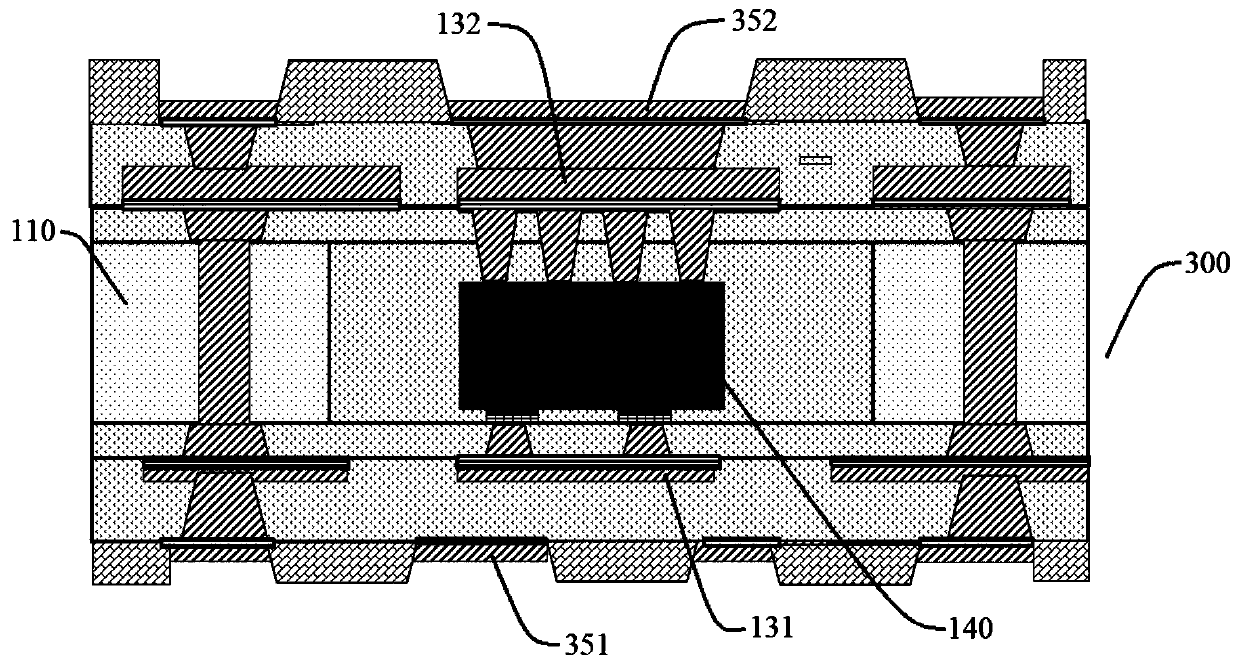

[0049] The invention relates to embedded chip packaging, which is characterized in that the chip and the frame are embedded in the photosensitive polymer dielectric material as the packaging material, an opening is directly formed on the back of the chip and metal such as copper is deposited, and at the same time, it is also passed through the terminal surface of the chip. The photosensitive polymer dielectric material is arranged to produce openings to form metal pillars that conduct the chip terminals, thereby forming a double-sided conduction or heat dissipation structure of the chip.

[0050] The photosensitive polymer dielectric material used in the present invention mainly includes polyimide photosensitive resin and polyphenylene ether photosensitive resin, such as Microsystems HD-4100, Hitachi PVF-02 and the like.

[0051] The metal posts formed on the surface of the chip terminals are used to connect the chip terminals with the first wiring layer. Metal pillars formed ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com