Structure of intrinsic passivation layer of silicon heterojunction solar cell and manufacturing method of structure

A solar cell and silicon heterojunction technology, applied in the field of solar cells, can solve the problems of mutual constraints of high passivation performance and low series resistance, high passivation performance and low parasitic absorption can not be achieved at the same time, to improve the overall photoelectric characteristics, High short-circuit current, life-enhancing effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

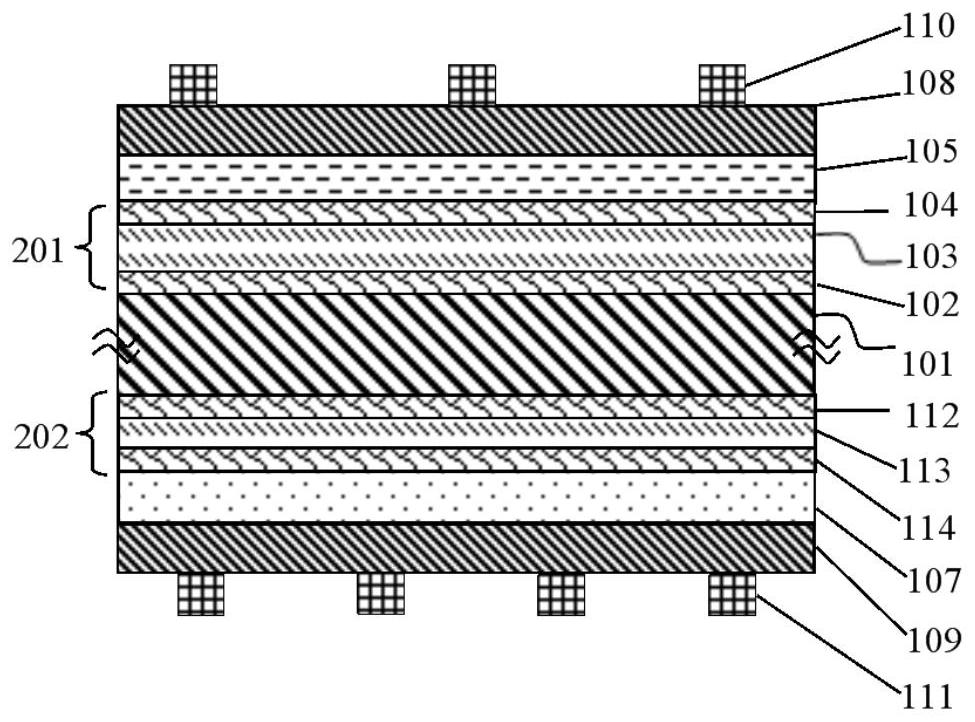

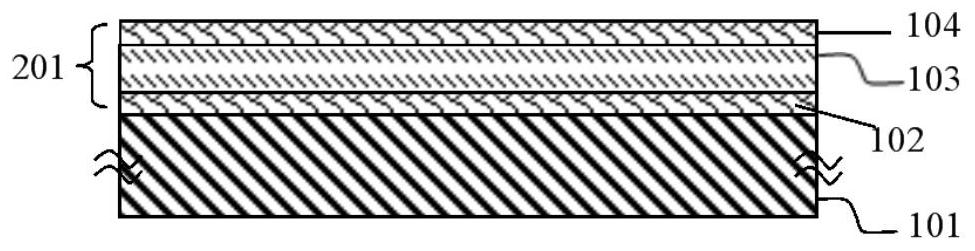

[0046] refer to figure 1 , figure 2 , Figure 4 , using the plasma-enhanced chemical vapor method to deposit the intrinsic silicon-based thin film passivation layer 201 with a specific structure and the structure and manufacturing method of the SHJ solar cell, the implementation method has the following steps:

[0047] (1) Prepare the n-type crystalline silicon substrate: adopt conventional texturing and cleaning steps to obtain a textured crystalline silicon substrate with a clean surface;

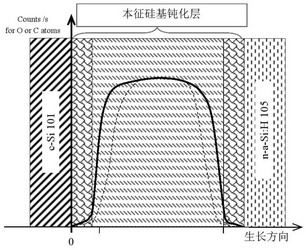

[0048] (2) Deposit intrinsic silicon-based film passivation layer on the first light-receiving surface: utilize plasma-enhanced chemical vapor phase method to deposit each layer of silicon film, such as figure 1 As shown, first, a layer of i-a-Si:H with a thickness of about 4 nm is deposited on the upper surface of the solar cell; then, a layer of wide bandgap silicon oxide i-SiO with a thickness of about 8 nm is grown x (x=1, 2, 3...) layer; Next, grow a layer of i-a-Si with a thickn...

Embodiment 2

[0059] refer to figure 2 and image 3 As shown, the first light-receiving surface intrinsic silicon-based passivation layer 201 and the second light-receiving surface intrinsic silicon-based passivation layer 202 with a specific structure are deposited by the hot filament chemical vapor method, and the SHJ solar cell structure with high double-faciality And the production method, the implementation method is as follows:

[0060] (1) Prepare the n-type crystalline silicon substrate: adopt conventional texturing and cleaning steps to obtain a textured crystalline silicon substrate with a clean surface;

[0061] (2) Depositing the intrinsic silicon-based passivation layer 201 on the first light-receiving surface by the hot filament chemical vapor method: as image 3 As shown, first, a layer of i-a-Si:H with a thickness of about 1 nm is deposited on the surface of the first light-receiving surface of the silicon wafer; then, a layer of wide-bandgap silicon oxide i-SiC with a th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More