Multi-die FPGAs implementing clock trees using active silicon connection layers

A connection layer, multi-die technology, used in CAD circuit design, special data processing applications, climate sustainability, etc., can solve problems such as large structural limitations, asynchronous clocks, single signal interconnection, etc. Design Convergence, Improved Performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

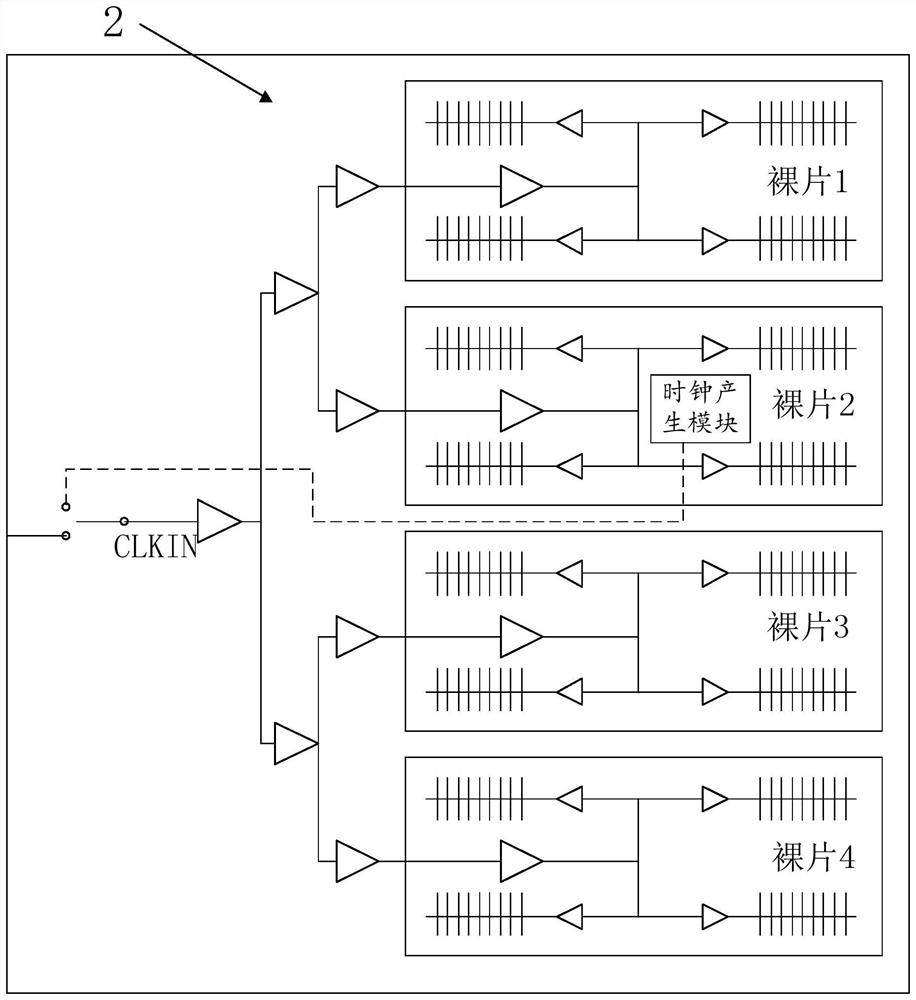

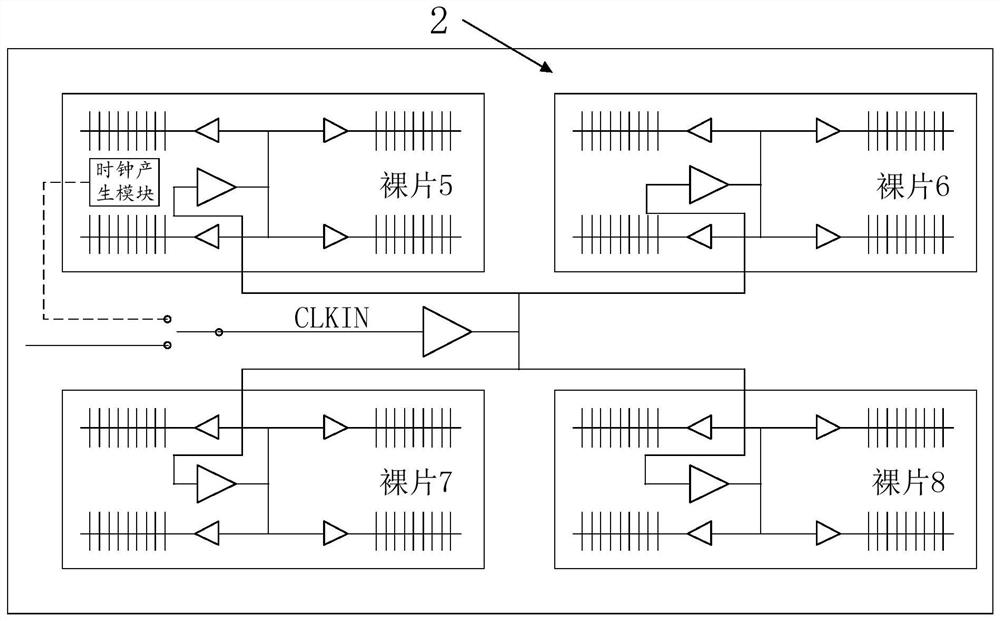

[0028] The specific embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

[0045] Each silicon stack connection module also has an interconnection resource module distributed around the silicon stack connection module, because

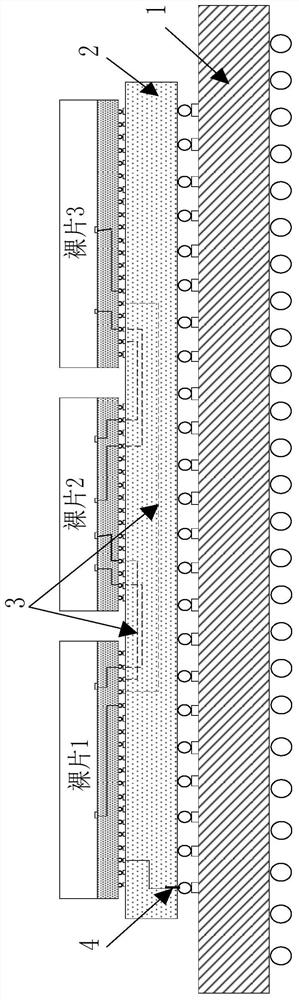

[0047] With this structure, the die signal of the FPGA die has been connected to the connection point terminal 6 by the silicon stack connection point 5 .

[0049] In addition, the inter-die wiring 3 arranged in the silicon connection layer 2 may also intersect along the first direction and the second direction

[0050] The above are only preferred embodiments of the present application, and the present invention is not limited to the above embodiments. It is understandable that this

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More