Test structure, wafer and manufacturing method of test structure

A technology of testing structure and manufacturing method, applied in semiconductor/solid-state device testing/measurement, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., to achieve the effect of improving yield and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

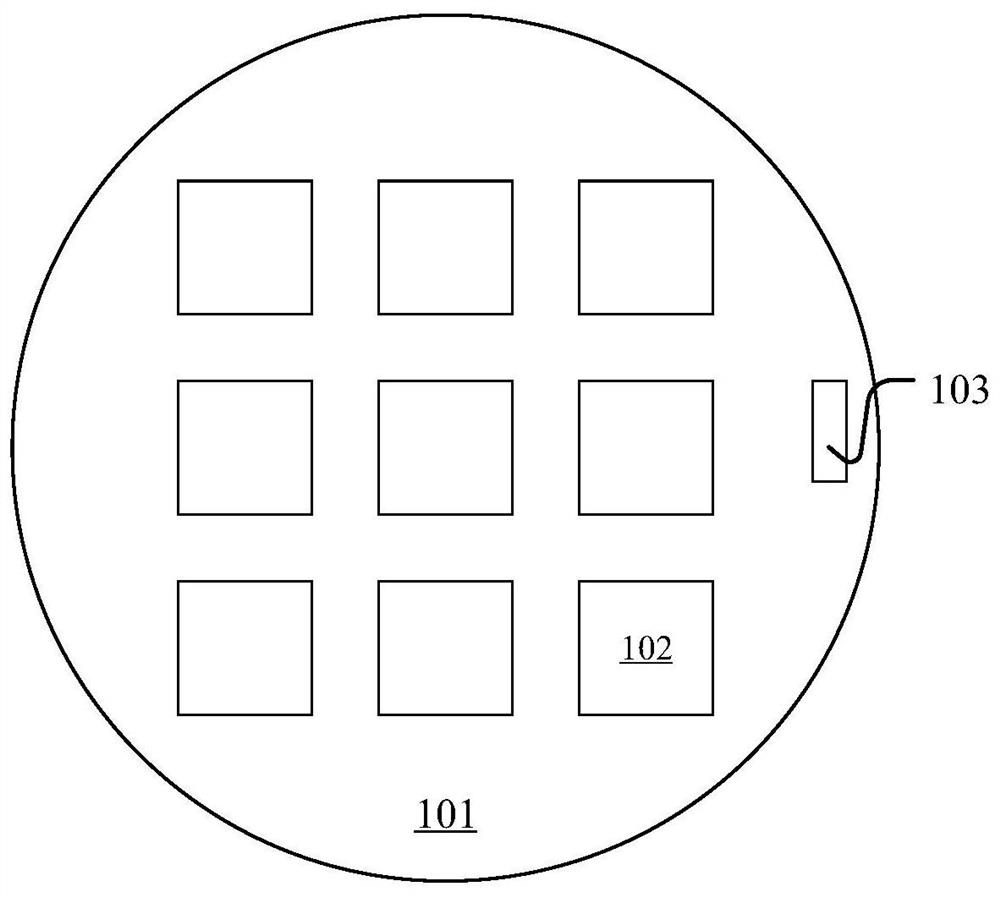

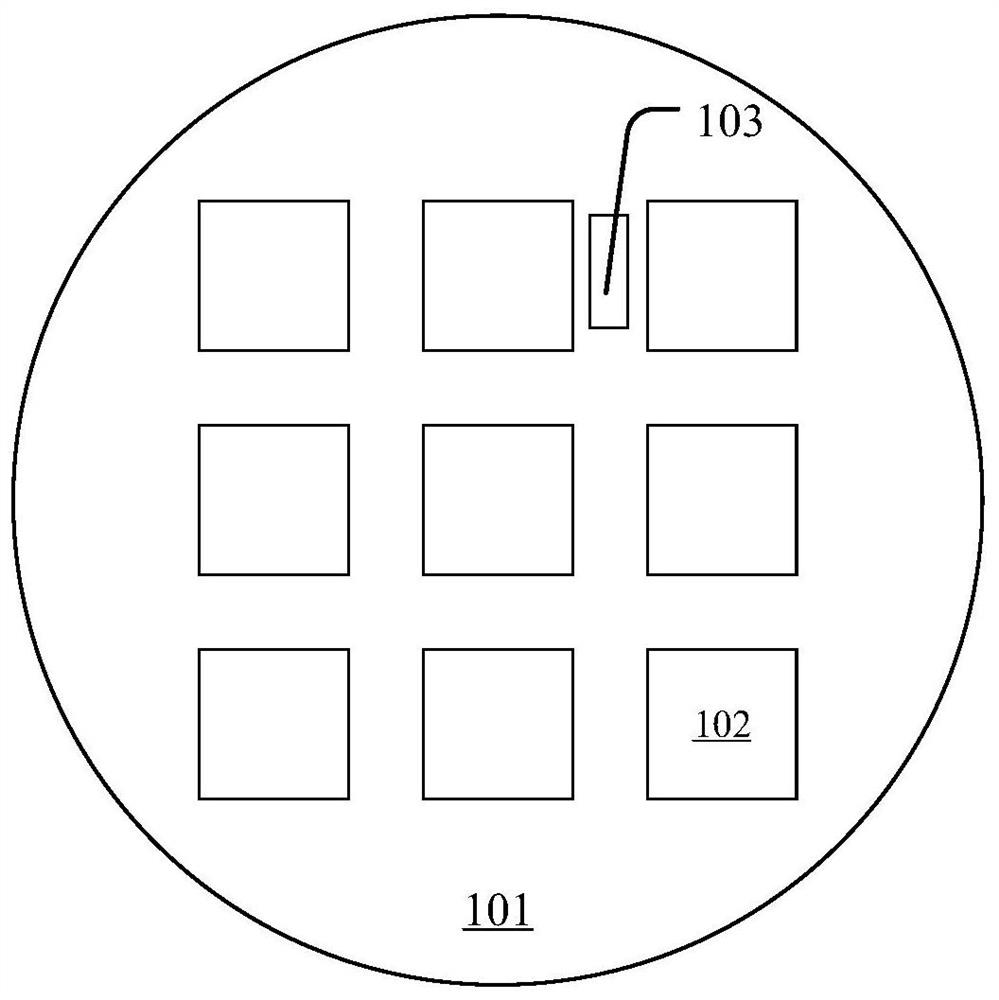

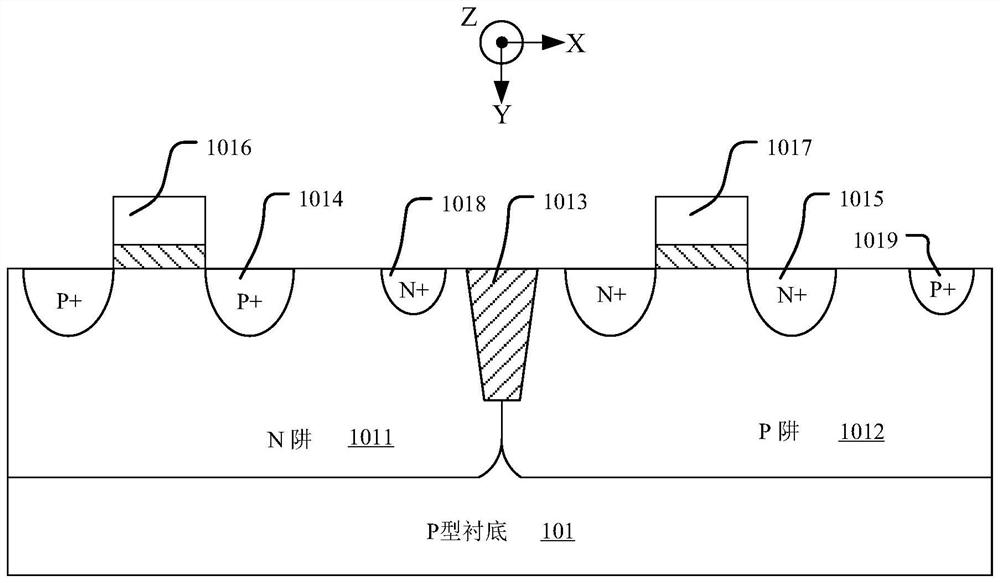

[0029] Various embodiments of the invention will be described in more detail below with reference to the accompanying drawings. In the various drawings, the same elements are denoted by the same or similar reference numerals. The components in the drawings are only for illustration, and do not have actual size proportional relationship. It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined arbitrarily with each other.

[0030] The manufacture of integrated circuits needs to form a large number of circuit components on a specific substrate area according to the specified circuit layout, such as multiple NMOS and PMOS. In order not to affect the performance of integrated circuits, isolation between adjacent circuit components is required. Corresponding Yes, it is also necessary to monitor the isolation of integrated circuits, such as parasitic PN junctions or parasitic BJTs in integrat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More