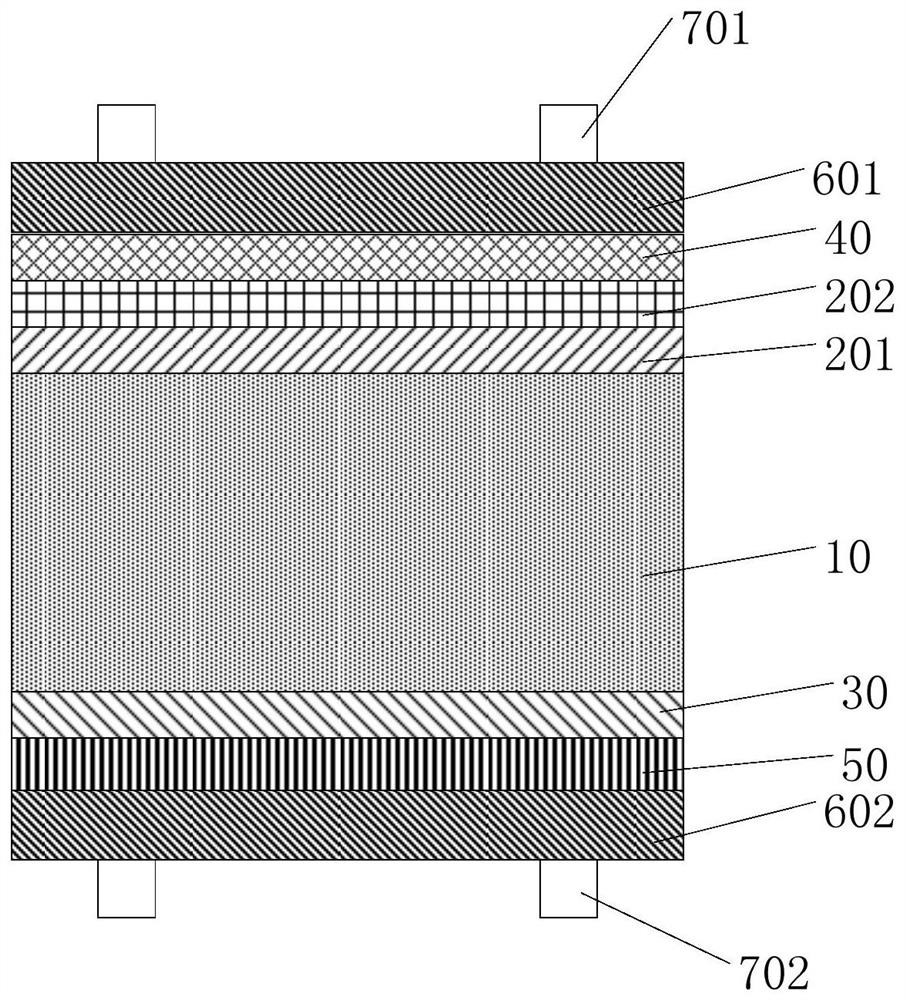

Silicon heterojunction solar cell and manufacturing method thereof

A solar cell and silicon heterojunction technology, which is applied in the field of solar cells, can solve problems such as low fill factor, affecting the efficiency of silicon heterojunction solar cells, large series resistance, etc., and achieve the effect of increasing the open circuit voltage and fill factor

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0073] The fabrication method of silicon heterojunction solar cells is as follows:

[0074] 1) Surface texturing and cleaning of N-type crystalline silicon wafers (n-c-Si) to form a pyramid structure and remove surface contamination impurities to obtain N-type silicon substrates. Among them, the single crystal silicon substrate used in the N-type crystalline silicon wafer is an N-type double-sided polished Czochralski single crystal silicon wafer with a thickness of 180 μm, a resistivity of 0.3Ω·cm, and a minority carrier lifetime of 1000 μs. Texturing of the silicon wafer was carried out using a mixed solution of 2% NaOH and IPA by mass percentage at a temperature of 83°C. Then, use the RCA standard cleaning method to clean the surface of the silicon wafer to remove surface contamination impurities. Next, remove the surface oxide layer with 1% hydrofluoric acid solution.

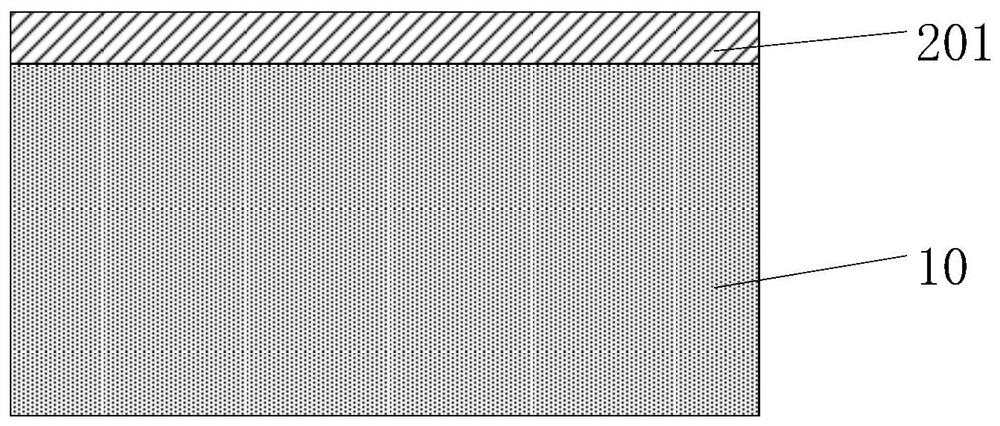

[0075] 2) Deposit a 1nm intrinsic amorphous silicon germanium (i-a-SiGe:H) layer on one side of the N-...

Embodiment 2

[0081] The fabrication method of silicon heterojunction solar cells is as follows:

[0082] 1) For an N-type crystalline silicon wafer (n-c-Si), the surface is textured and cleaned to form a pyramid structure and remove surface contamination impurities to obtain an N-type silicon substrate. Among them, the single crystal silicon substrate used in the N-type crystalline silicon wafer is an N-type double-sided polished Czochralski single crystal silicon wafer with a thickness of 180 μ8, a resistivity of 0.3, and a minority carrier lifetime of 1000 μs. Texturing of the silicon wafer was carried out using a mixed solution of 2% NaOH and IPA by mass percentage at a temperature of 83°C. Then, use the RCA standard cleaning method to clean the surface of the silicon wafer to remove surface contamination impurities. Next, remove the surface oxide layer with 1% by mass hydrofluoric acid solution.

[0083] 2) Deposit a 5nm intrinsic amorphous silicon germanium (i-a-SiGe:H) layer on one...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More