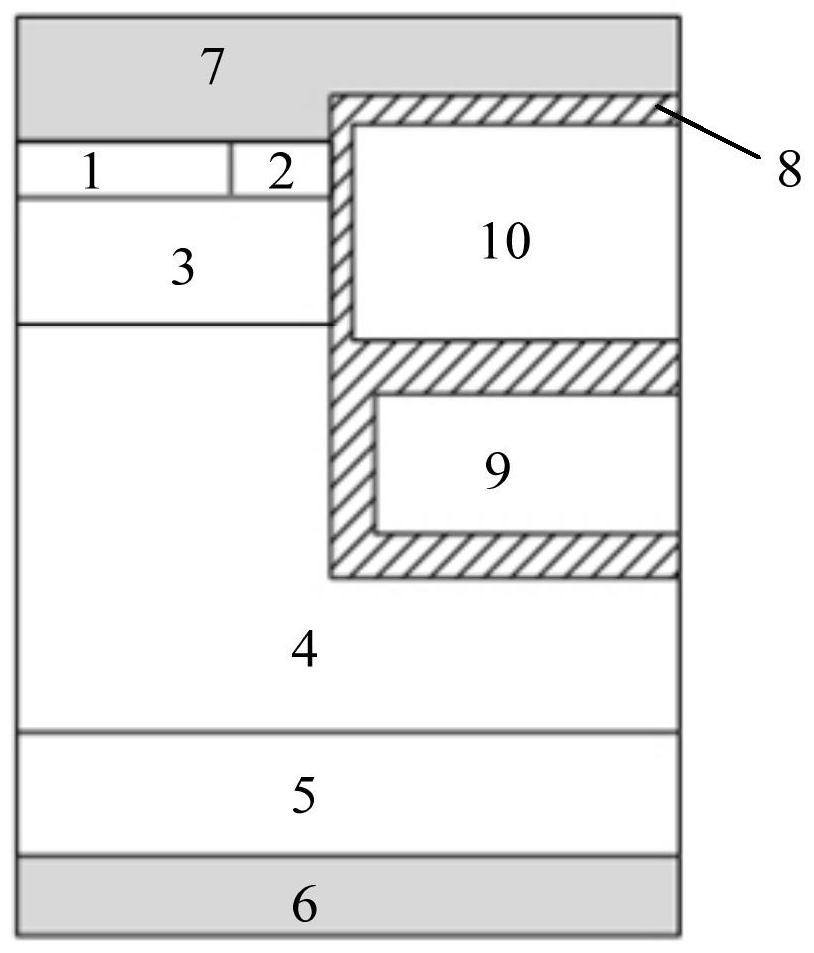

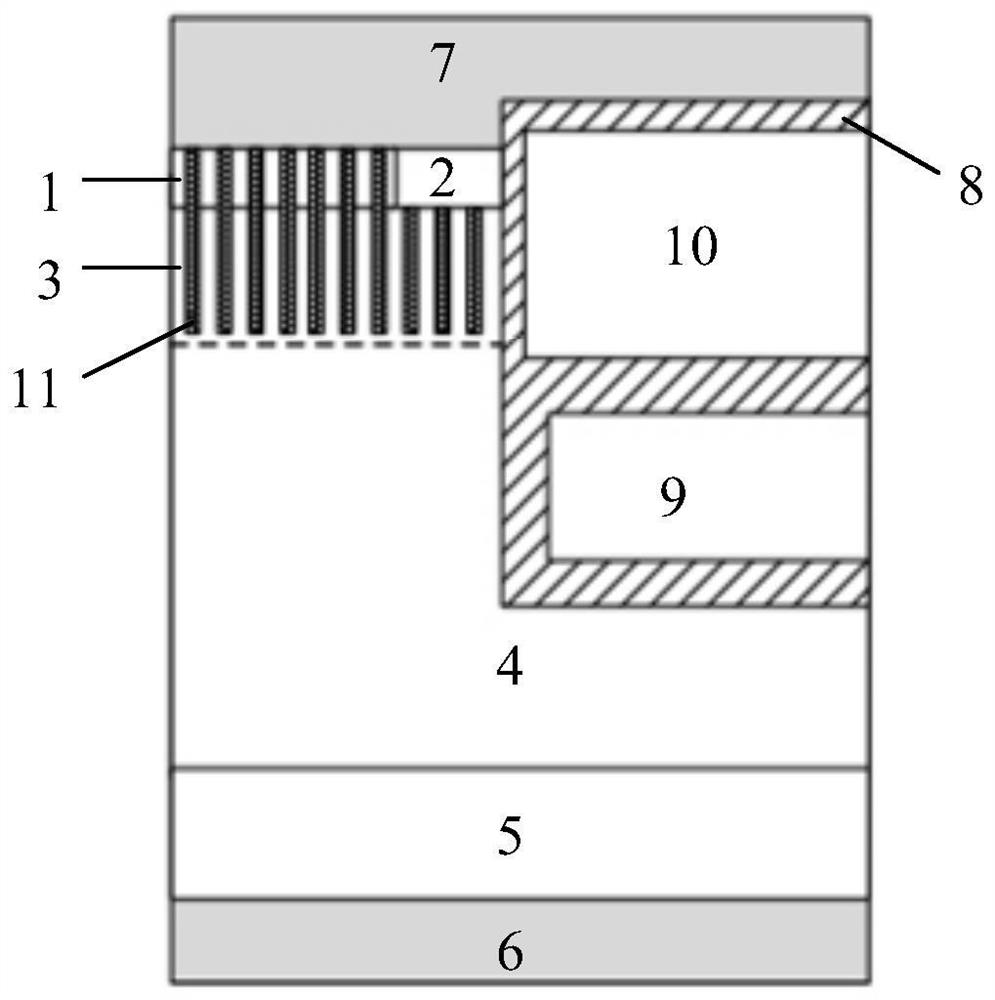

Shield gate MOSFET device with uniformly doped channel and processing technology

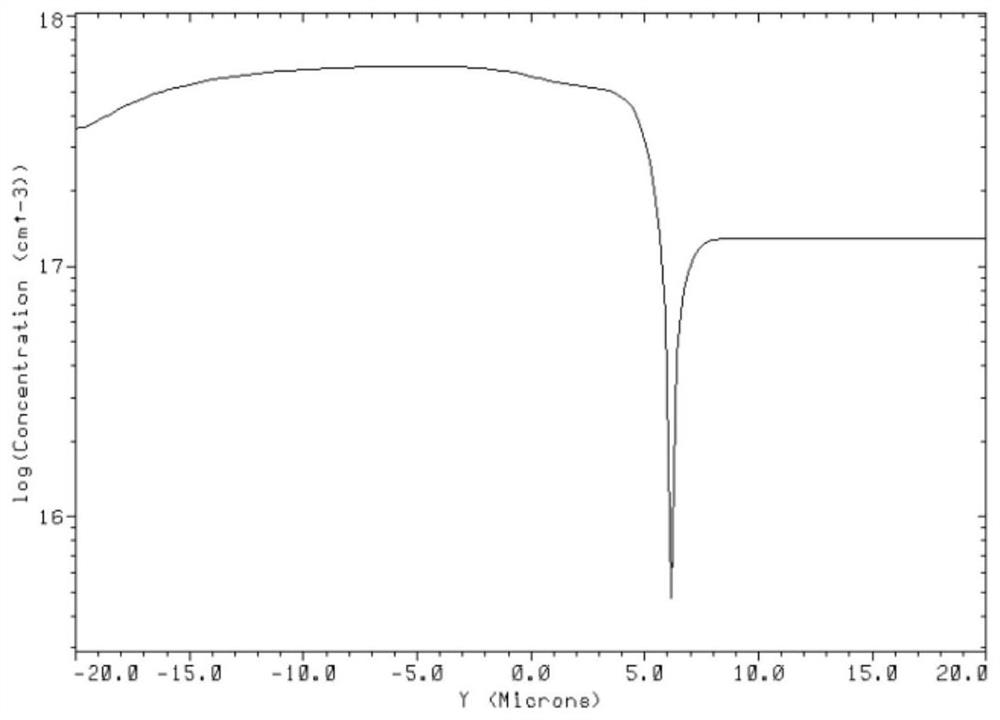

A uniform doping and shielding gate technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of unfavorable device threshold stability, narrowing of P-region depletion region, uneven concentration distribution, etc., to achieve The effect of reducing the risk of punch-through, stabilizing the threshold voltage, and good doping concentration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] Embodiments of the present invention are described below through specific examples, and those skilled in the art can easily understand other advantages and effects of the present invention from the content described in this specification. The present invention can also be implemented or applied through other different specific implementation modes, and various modifications or changes can be made to the details in this specification based on different viewpoints and applications without departing from the spirit of the present invention.

[0035] Below in conjunction with accompanying drawing, describe technical scheme of the present invention in detail:

[0036] In a specific embodiment, the semiconductor of the first conductivity type is a P-type semiconductor, and the semiconductor of the second conductivity type is an N-type semiconductor. In another specific embodiment, the semiconductor of the first conductivity type is an N-type semiconductor, and the semiconduct...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More