On-chip integrated ipd packaging structure and its packaging method, three-dimensional packaging structure

A packaging structure and integrated capacitor technology, which is applied in the field of IPD (Integrated Passive Devices), can solve the problems of large size and poor precision, and achieve the effects of reducing the area required for installation, flexible design, and high control precision

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

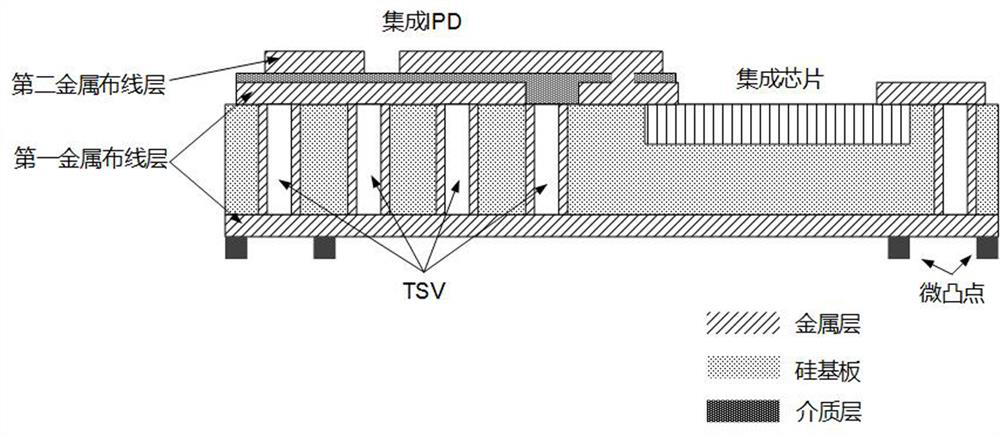

[0052] refer to figure 1 , an embodiment of the present invention provides an on-chip integrated IPD packaging structure, including:

[0053] Silicon substrate layer;

[0054] The first metal wiring layer is arranged on the upper and lower surfaces of the silicon substrate layer and communicated with through silicon vias penetrating the silicon substrate layer;

[0055] a dielectric layer disposed on the surface of the first metal wiring layer located on the upper surface of the silicon substrate layer;

[0056] The second metal wiring layer is arranged on the surface of the dielectric layer, and is sequentially stacked with the dielectric layer and the first metal wiring layer to form an on-chip integrated IPD; and

[0057] chip, integrated on the silicon substrate layer.

[0058] In this embodiment, the silicon substrate layer of the present invention adopts a commonly used silicon substrate, and for a high-frequency system, a high-resistance silicon substrate is preferab...

Embodiment 2

[0069] Based on the on-chip integrated IPD packaging structure described in Embodiment 1, an embodiment of the present invention also provides a packaging method for an on-chip integrated IPD packaging structure, including the following steps:

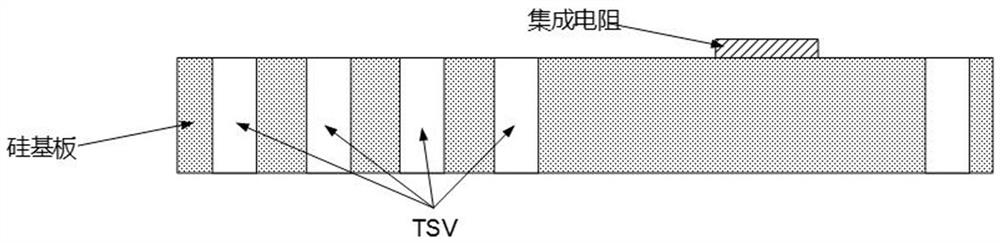

[0070] S1. Fabricate on-chip integrated resistors by sputtering on the silicon substrate layer;

[0071] S2. Fabricate through-silicon vias on the silicon substrate layer using a DRIE etching process;

[0072] S3. Sputter a seed layer on the upper and lower surfaces of the silicon substrate layer and make a photoresist mask, use a double-sided electroplating patterning process to make a continuously thickened metal layer on the upper and lower surfaces of the silicon substrate layer, and make metallized through-holes on the inner wall of the through-silicon hole. hole, remove the photoresist and seed layer to form the first metal wiring layer, including the lower electrode of the on-chip integrated inductor and on-chip integrated capac...

Embodiment 3

[0077] Based on the on-chip integrated IPD packaging structure described in Embodiment 1, the embodiment of the present invention also provides a three-dimensional packaging structure of on-chip integrated IPD, including:

[0078] Multiple single-layer on-chip integrated IPD packaging structures stacked up and down in sequence, and each on-chip integrated IPD packaging structure is interconnected through a micro-bump structure;

[0079] The on-chip integrated IPD package structure specifically includes:

[0080] Silicon substrate layer;

[0081] The first metal wiring layer is arranged on the upper and lower surfaces of the silicon substrate layer and communicated with through silicon vias penetrating the silicon substrate layer;

[0082] a dielectric layer disposed on the surface of the first metal wiring layer located on the upper surface of the silicon substrate layer;

[0083] The second metal wiring layer is arranged on the surface of the dielectric layer, and is sequen...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More