Preparation method of efficient monocrystalline silicon SE-PERC battery piece

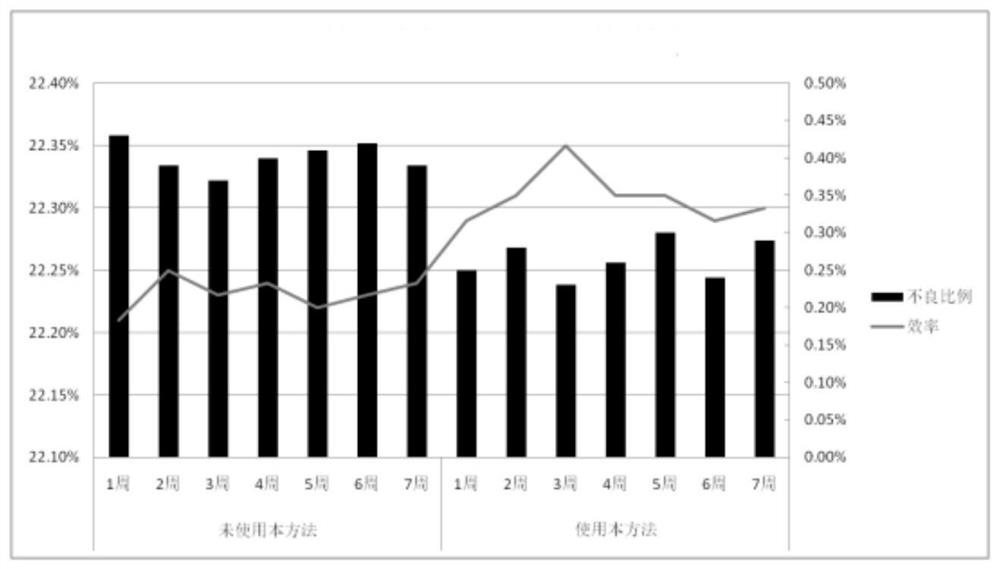

A technology of monocrystalline silicon and solar cells, applied in circuits, photovoltaic power generation, electrical components, etc., can solve the problems of shortened minority carrier diffusion length, dead layer, and photogenerated carriers can no longer be effectively collected, so as to improve conversion efficiency and good rate, the effect of reducing the ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0036] The invention provides a method for preparing a high-efficiency monocrystalline silicon SE-PERC cell, which mainly includes the following steps:

[0037] Select raw silicon wafers: prepare gallium-doped silicon rods, and then cut the gallium-doped silicon rods by wire cutting method to obtain raw silicon wafers, and set the direction of the cutting lines on the silicon wafers as the X direction;

[0038] Texturing: Forming a textured textured surface on the surface of the silicon wafer;

[0039] Diffusion: Phosphorus diffusion treatment is performed on the textured silicon wafer to form a PN junction;

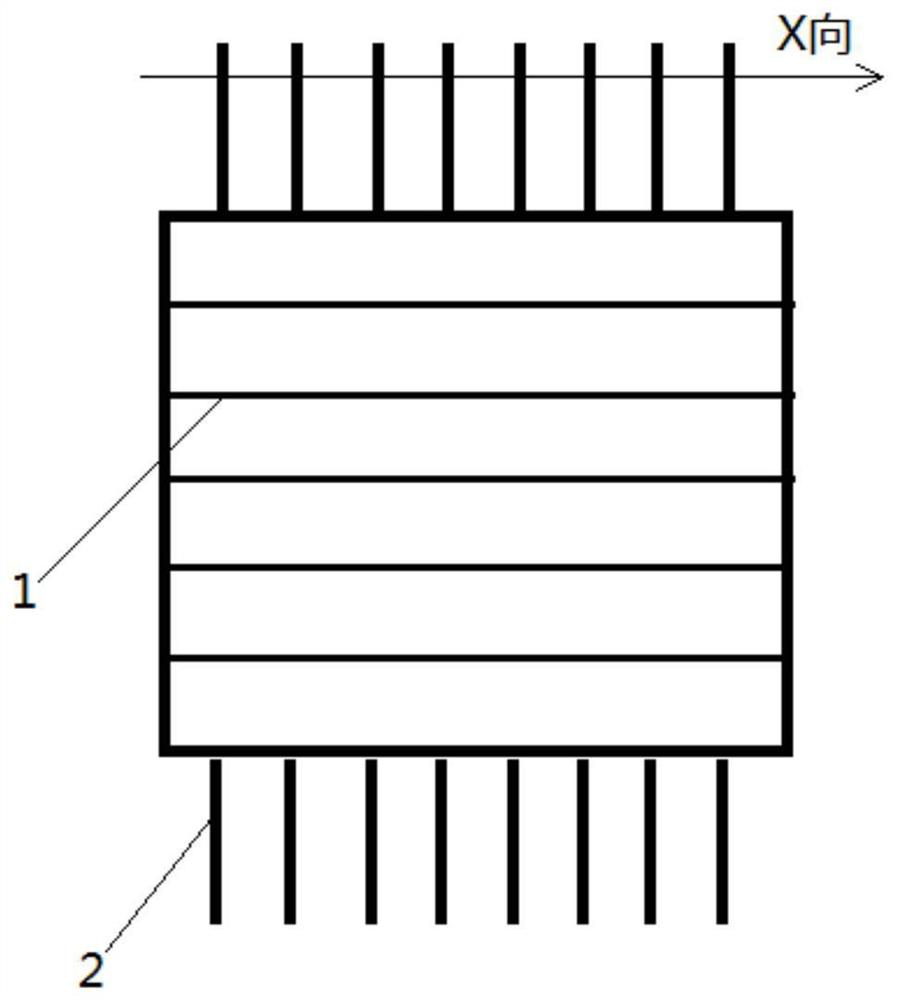

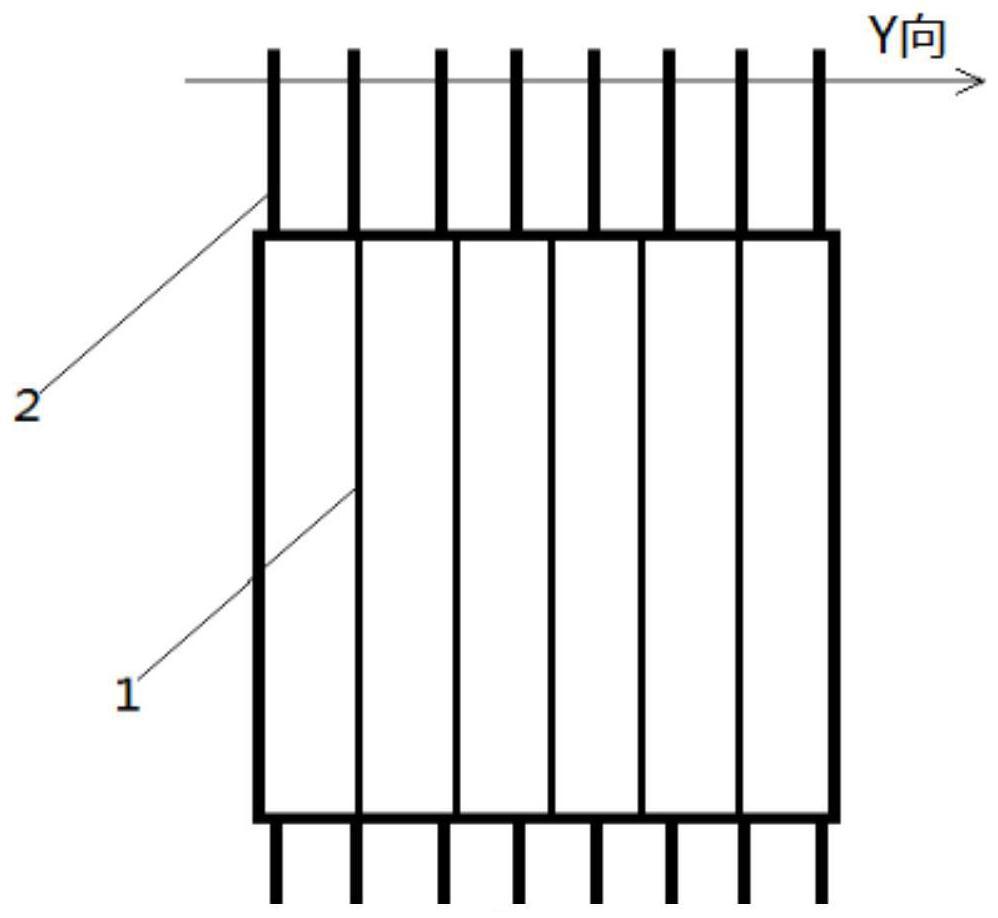

[0040] Laser doping: The diffused silicon wafer is heavily doped with laser, and the graph formed by controlling the laser doping is parallel to the cutting line, that is, it is also in the X direction;

[0041]Phospho-silicate glass removal: remove the phosphorous-silicate glass on the back of the silicon wafer and around it. When removing the phosphorous-silicate glas...

Embodiment 1

[0050] The invention provides a method for preparing a high-efficiency monocrystalline silicon SE-PERC cell, comprising the following steps:

[0051] (1) Step S1, preparing gallium-doped silicon rods, controlling the concentration of gallium elements to ensure that the resistivity is in the range of 0.3-1.1Ω·cm, using diamond wires to cut gallium-doped silicon rods to form X-direction cutting lines Raw silicon wafer;

[0052] (2) Step S2, using a trough type texturing machine to pre-clean and texturize the silicon wafers to ensure that the cutting lines of the silicon wafers in the texturing basket are set vertically;

[0053] (3) Step S3, setting the cutting line direction of the silicon chip after texturing perpendicular to the opening direction of the quartz boat in the diffusion device, forming a PN junction on the surface of the silicon chip after the diffusion step;

[0054] (4) Step S4, according to the metallization pattern of screen printing, the PSG layer formed aft...

Embodiment 2

[0063] The difference from Example 1 is that the passivation film and passivation anti-reflection film on the back of this example are deposited integrally by plate or tube PECVD, and the passivation anti-reflection film is only deposited on the front by tube or plate PECVD.

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More