Semiconductor structure and forming method thereof

A semiconductor and graphics layer technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of increasing the difficulty and complexity of integrated circuits, so as to ensure the integrity of graphics, reduce the probability of mis-etching, and improve The effect of craft effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] At present, the problem of short circuit between interconnect lines formed in the inter-metal dielectric layer is likely to occur. The reasons for the short-circuit problem between interconnect lines are analyzed in combination with a method for forming a semiconductor structure.

[0014] refer to Figure 1 to Figure 6 , a schematic diagram of the structure corresponding to each step in a method for forming a semiconductor structure is shown.

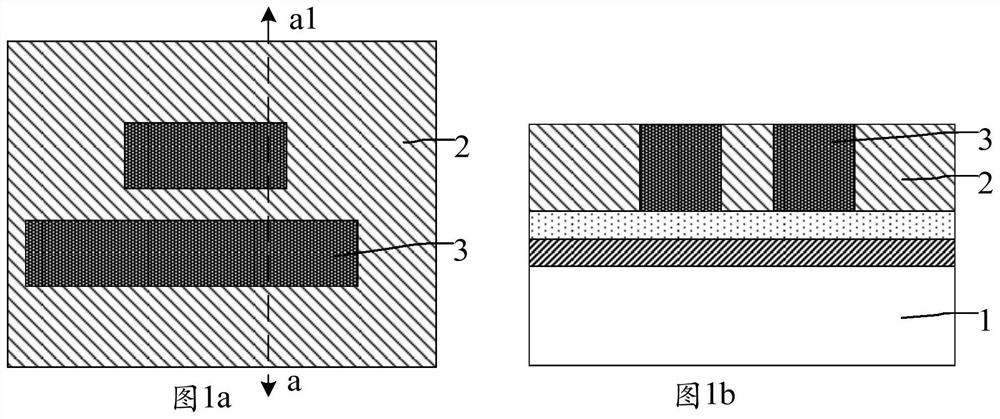

[0015] refer to figure 1 , figure 1 a is a top view, figure 1 b is figure 1 The cross-sectional view along the secant line aa1 in a, a substrate (not shown) is provided, and a metal interlayer dielectric layer 1 is formed on the substrate.

[0016] continue to refer to figure 1 , a core layer 2 and a plurality of sacrificial layers 3 located in the core layer 2 are formed on the inter-metal dielectric layer 1, and the plurality of sacrificial layers 3 are arranged at intervals.

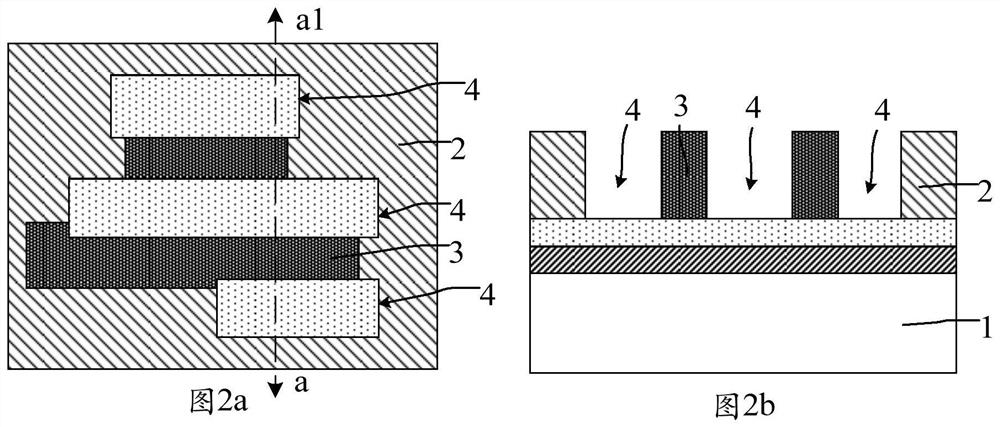

[0017] refer to figure 2 , figure 2...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More