Preparation method of transistor channel, source electrode and drain electrode based on micro-region electrochemical etching

A source-drain electrode, electrochemical technology, used in transistors, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of complex process, high cost, low resolution, etc., and achieve the effect of solving complex process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

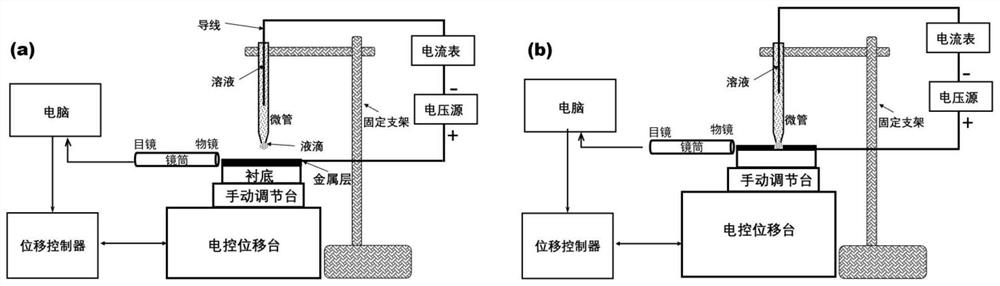

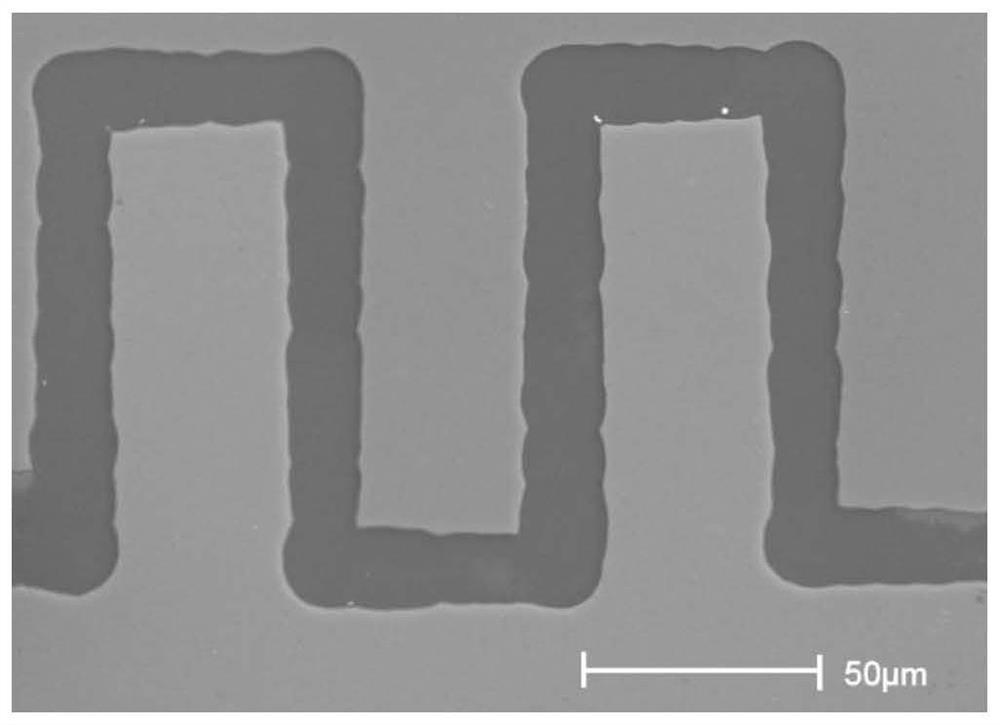

[0029] In this example, SiO 2 Taking the preparation of inter-finger electrodes on the / Si substrate as an example, the preparation method of transistor channel and source-drain electrodes based on micro-area electrochemical etching in the present invention is explained. The microtube used is a glass capillary treated by heating and stretching, and the diameter of the tip of the capillary is 15 microns. 0.5M CuSO 4 As an electrolyte, insert a copper wire into the electrolyte to ground. SiO 2 A copper layer with a thickness of 85 nanometers is deposited on the / Si substrate by vacuum thermal evaporation process, and a bias voltage of 2V is applied to the copper layer. Fill the prepared microtubes with 0.5M CuSO 4 . Fix the glass microtube above the substrate, and use the electric translation stage to control the upward movement of the substrate until it is observed that the electrolyte forms a liquid meniscus between the nozzle of the glass microtube and the substrate and ...

Embodiment 2

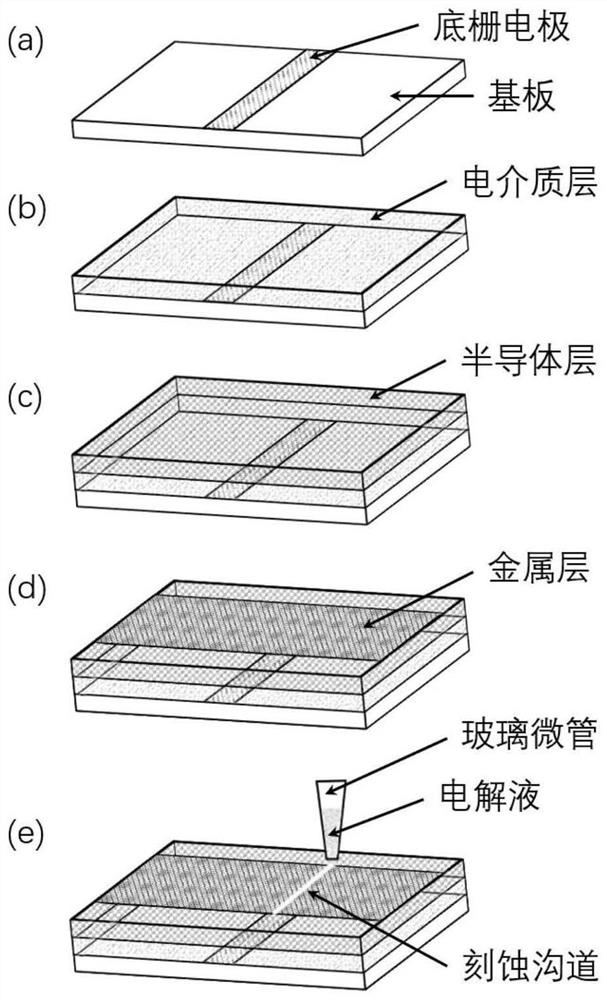

[0032] This example takes the preparation of bottom-gate top-contact structure transistors on flexible polyimide substrates as an example, and explains the method for preparing transistor channels and source-drain electrodes based on micro-area electrochemical etching in the present invention. The specific steps as follows:

[0033] Step 1: prepare an aluminum bottom gate electrode with a width of 1mm and a thickness of 50nm by vacuum deposition on the cleaned polyimide substrate;

[0034] Step 2: Prepare a PVDF-TrFE-CTFE dielectric layer on the aluminum electrode described in Step 1 by spin coating, and anneal at 130° C. for 3 hours;

[0035] Step 3: Prepare organic semiconductor DPP-DTT on the dielectric layer described in Step 2 by spin coating, and anneal at 130° C. for 3 hours;

[0036] Step 4: Prepare copper stripes with a width of 0.78 mm and a thickness of 85 nm by vacuum deposition on the organic semiconductor layer described in step 3;

[0037] Step five: use the m...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More