Near-threshold circuit delay estimation method based on polynomial chaos Kriging element model

A kriging element and circuit delay technology, applied in CAD circuit design, special data processing applications, etc., can solve the problems that sub-threshold circuits cannot meet the requirements of calculation speed, increase leakage power consumption, and weaken energy consumption advantages. Achieve the effects of saving simulation time, improving accuracy, and increasing model accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

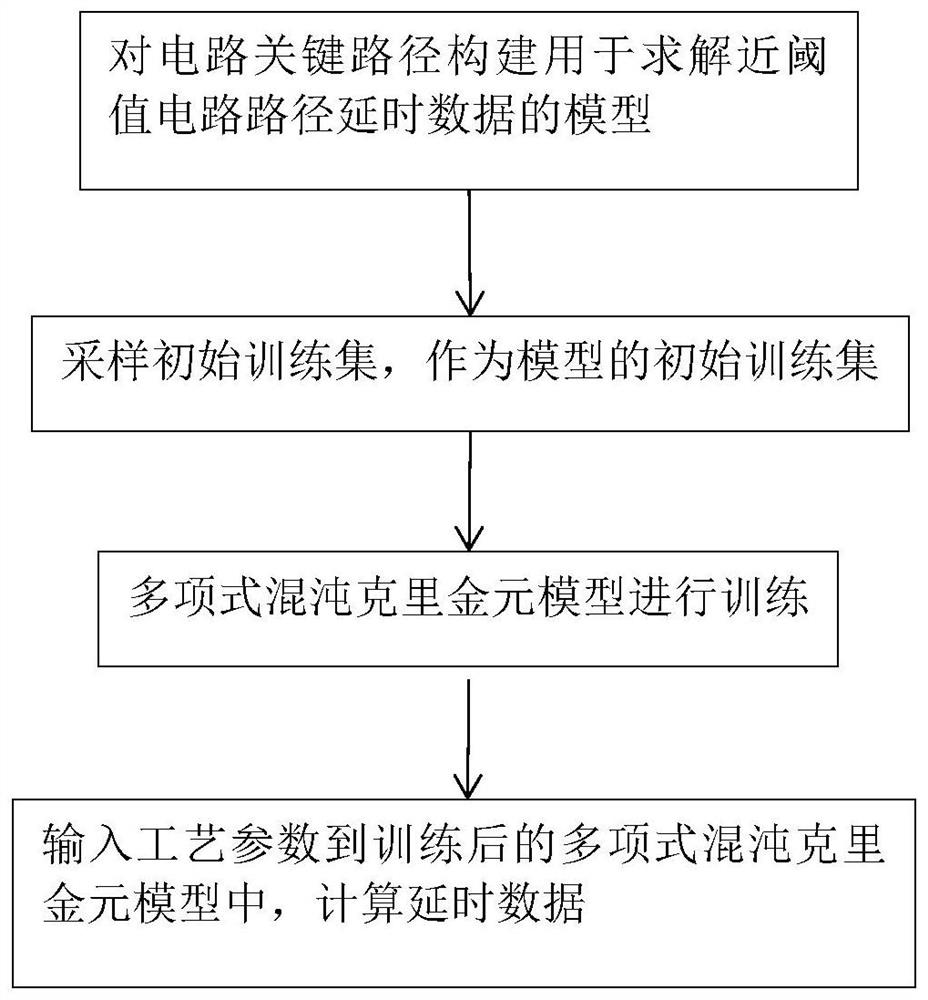

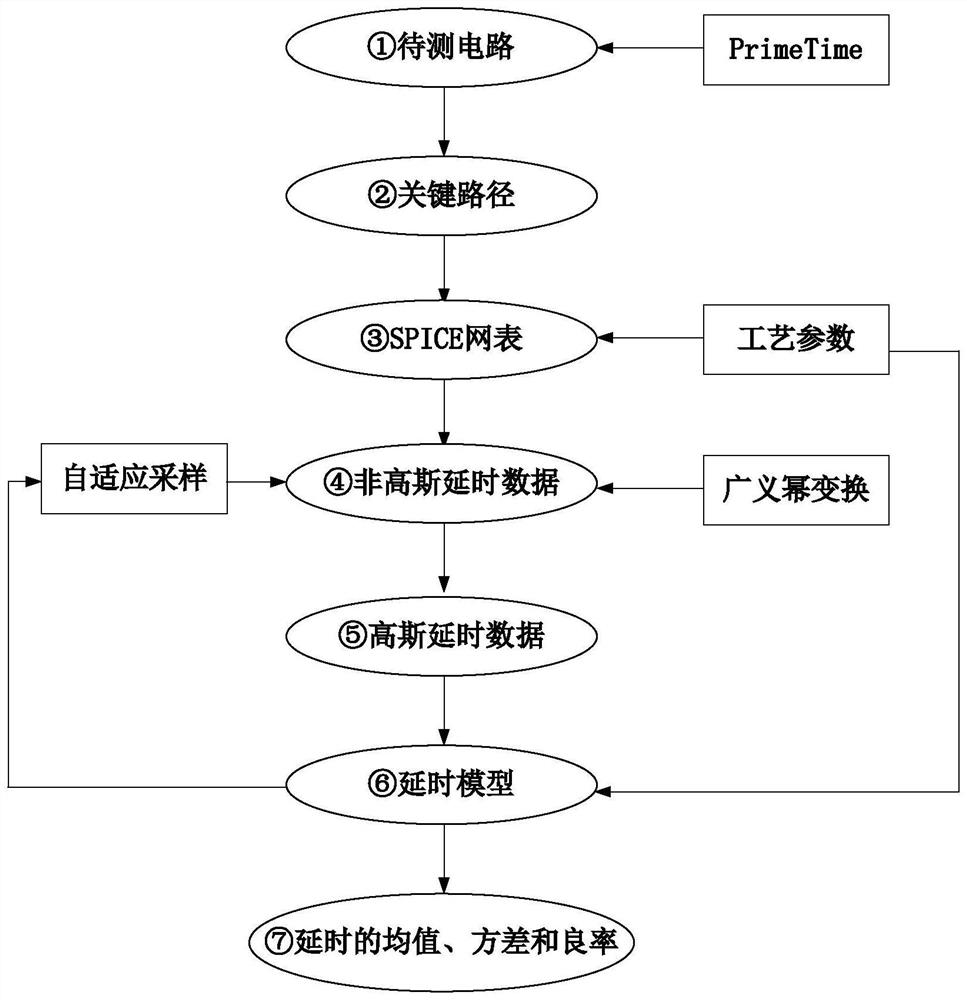

[0024] Under normal voltage, the delay fluctuation caused by the process deviation is small, and the performance loss caused by the pessimistic estimation of the path delay fluctuation by the traditional timing analysis method is small. However, as the supply voltage decreases, the delay fluctuation increases under the process deviation, and the traditional timing analysis method will cause serious performance loss, which is no longer suitable for the near-threshold circuit timing analysis under the process deviation. Different from traditional timing analysis methods, the present invention's near-threshold circuit delay estimation method based on polynomial chaotic Kriging element model models the delay of the path as a distribution, and determines the delay by solving the distribution and its statistics. time fluctuation magnitude and worst case delay. Compared with the traditional timing analysis method, the statistical timing analysis method used in the present invention h...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More