Multi-chip packaging structure and manufacturing method thereof

A technology of multi-chip packaging and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., and can solve the difficulties in meeting the requirements of high performance, fast speed, multi-chip connection packaging and modularization, etc. problem, to achieve excellent heat dissipation effect, simple process structure, and short electrical path

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0042] In the embodiment, a novel chip packaging structure is provided, and the manufacturing method is as follows:

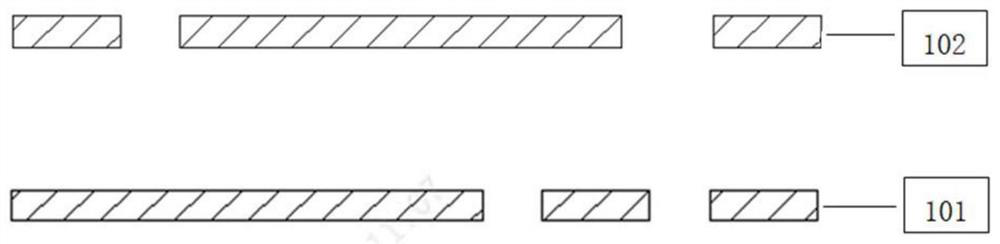

[0043] S101, provide patterned first metal substrate 101, second metal substrate 102 ( figure 1 ).

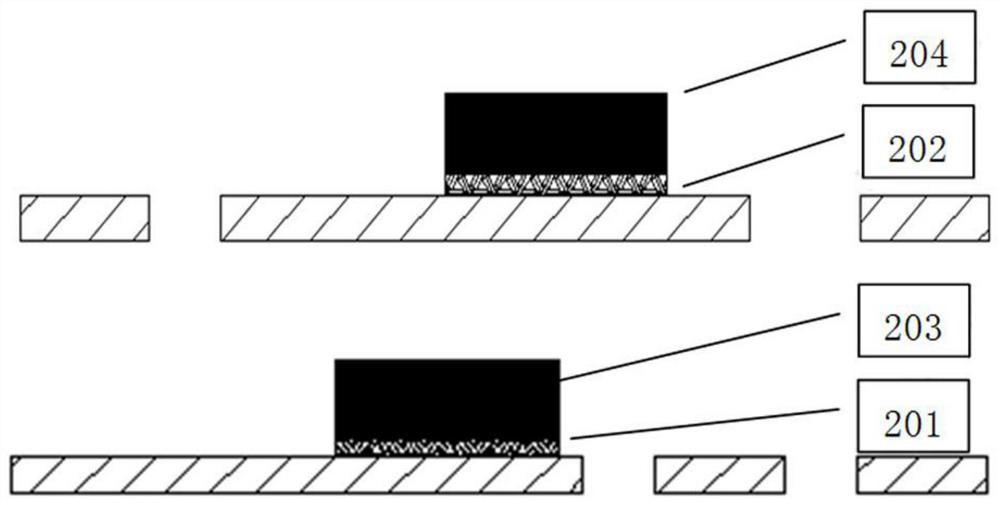

[0044] S102. Fabricate a first conductive layer 201 and a second conductive layer 202 on the first metal substrate 101 and the second metal substrate 102, and respectively place the first chip 203 and the first chip 203 on the first conductive layer 201 and the second conductive layer 202. Chip 204 ( figure 2 ).

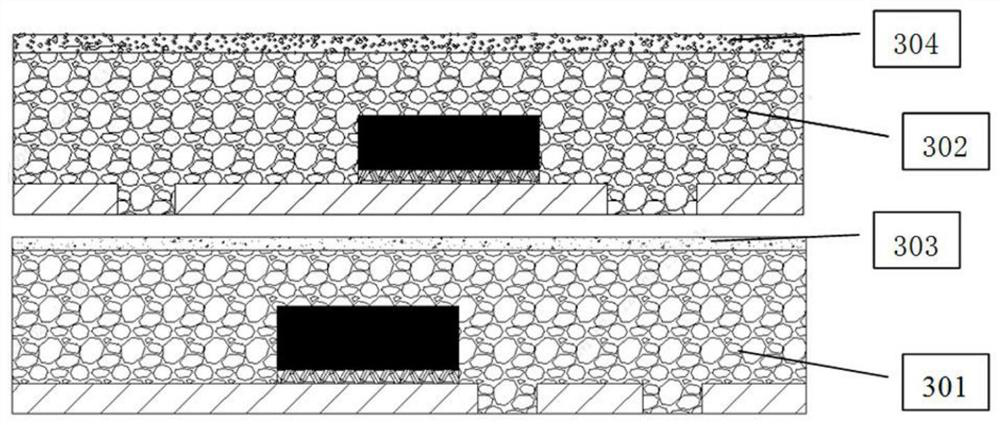

[0045] S103, on the first metal substrate 101, the second metal substrate 102, the side of the first conductive layer 201, the side sheet of the second conductive layer 202, the first chip 203, and the second chip 204, make the first dielectric layer 301 and the second dielectric layer layer 302 , on the first dielectric layer 301 and the second dielectric layer 302 , the seventh conductive layer 303 and the eighth conductive layer 304 are fabricat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More