POLO-IBC solar cell and preparation method thereof

A solar cell and electrode technology, applied in the field of solar cells, can solve the problems of high cost, complicated process, and long production cycle, and achieve the effects of reducing processes and steps, simple process, and shortening the production cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

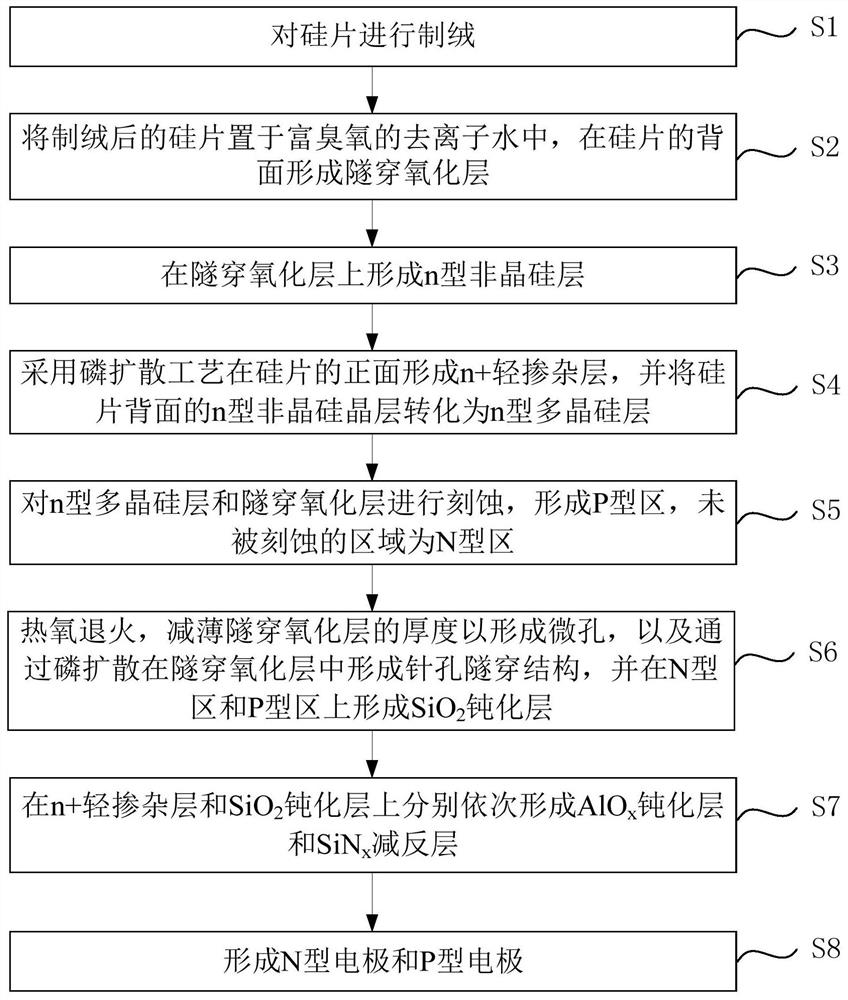

[0037] see figure 1 , the preparation method of a kind of POLO-IBC solar cell provided by the invention, comprises the following steps:

[0038] S1. Texturing the silicon wafer;

[0039] Specifically, the silicon wafer is a P-type silicon wafer with a thickness of 50-200 μm, a resistivity of 0.3-10 Ω·cm, a minority carrier lifetime of 0.2-2 ms, and a pyramidal light-trapping structure formed on the surface of the silicon wafer after texturing.

[0040] S2, placing the textured silicon wafer in ozone-rich deionized water to form a tunnel oxide layer on the back side of the silicon wafer;

[0041] Specifically, the textured silicon wafer is placed in ozone-rich deionized water for 1-30 minutes, and a tunnel oxide layer with a thickness of 0.5-2.5 nm is formed on the back surface of the silicon wafer. Wherein the tunnel oxide layer is SiO 2 layer.

[0042] Preferably, the temperature of the ozone-enriched deionized water is 15-60°C.

[0043]It should be noted that the ozone-...

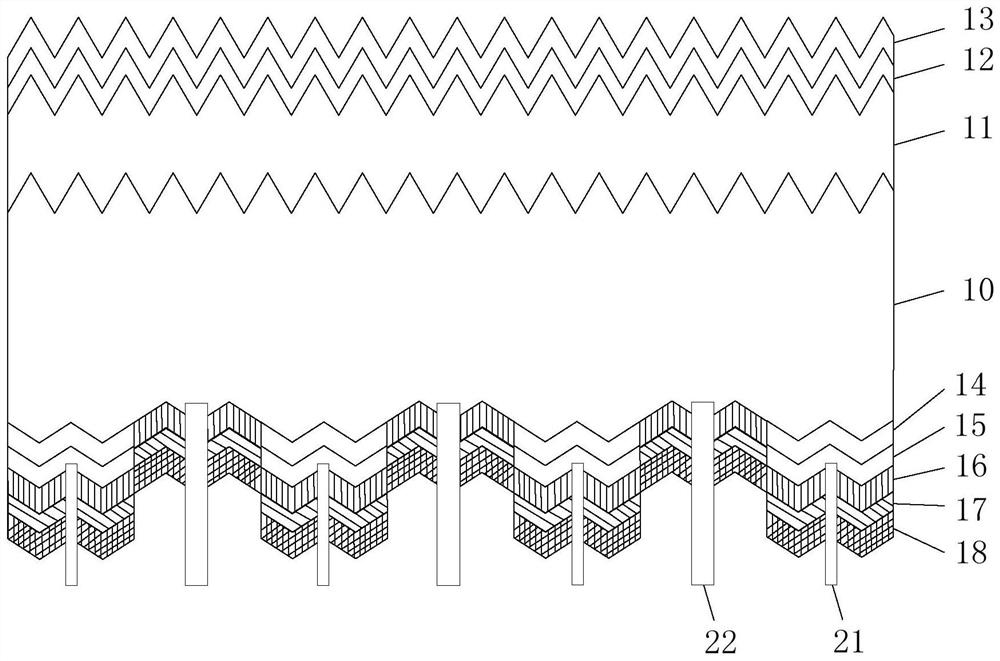

Embodiment 1

[0079] S1. Texturing a silicon wafer, the silicon wafer is a P-type silicon wafer with a size of 166mm*166mm, a thickness of 160μm, a resistivity of 2.0Ω·cm, and a minority carrier lifetime of 1ms;

[0080] S2. Place the textured silicon wafer in ozone-rich deionized water for 15 minutes to form a tunneling oxide layer with a thickness of 1.5 nm on the back side of the silicon wafer;

[0081] S3, adopt CVD equipment, pass into PH 3 、SiH 4 and N 2 gas, at a temperature of 450°C, deposit and form an n-type amorphous silicon layer on the tunnel oxide layer, and the doping concentration of the n-type amorphous silicon layer is 4*10 20 cm -3 , with a thickness of 180nm;

[0082] S4. Place the silicon wafer in the diffusion equipment, feed the phosphorus source into the diffusion equipment, and diffuse for 80 minutes at a temperature of 850°C, wherein the back of the silicon wafer leans against the boat, and the front faces the phosphorus source (POCl 3 ), forming an n+ lightly ...

Embodiment 2

[0089] S1, same as step S1 of embodiment 1;

[0090] S2. Place the textured silicon wafer in ozone-rich deionized water for 20 minutes to form a tunneling oxide layer with a thickness of 2.0 nm on the back side of the silicon wafer;

[0091] S3, adopt CVD equipment, pass into PH 3 、SiH 4 and N 2 gas, at a temperature of 550°C, deposit and form an n-type amorphous silicon layer on the tunnel oxide layer, and the doping concentration of the n-type amorphous silicon layer is 3*10 20 cm -3 , with a thickness of 300nm;

[0092] S4. Place the silicon wafer in the diffusion equipment, feed the phosphorus source into the diffusion equipment, and diffuse for 75 minutes at a temperature of 950°C, wherein the back of the silicon wafer leans against the boat, and the front faces the phosphorus source (POCl 3 ), forming an n+ lightly doped layer on the front side of the silicon wafer, and converting the n-type amorphous silicon layer on the back side of the silicon wafer into an n-ty...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More