Ferroelectric double-annealing process capable of enhancing storage window

An annealing process, ferroelectric technology, applied in circuits, electrical components, electric solid-state devices, etc., can solve the problem of slow cell size scaling, and achieve the effect of large storage window and large storage window value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0035] In this example, taking the ferroelectric memory based on hafnium oxide as an example, a new double annealing step process step is briefly described. Under the conditions of the same read and write times and the same read and write voltage, it has a larger storage window. Compared with the mainstream land, the device has good retention characteristics and a small operating voltage. It is a non-volatile memory with excellent performance.

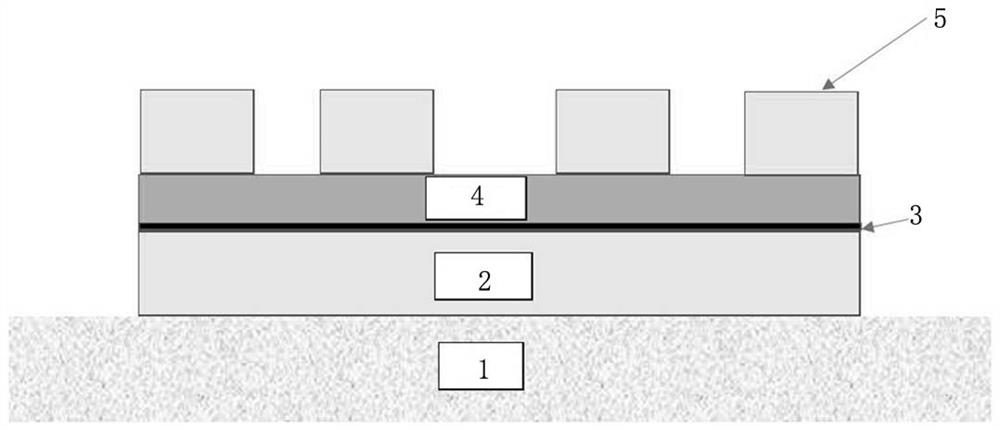

[0036] Figure 9 The flow chart of preparing the ferroelectric memory for this example includes 6 steps of preparing the lower motor, preparing the intercalation layer, pre-annealing the sample, preparing the functional layer, preparing the upper electrode and post-annealing the sample.

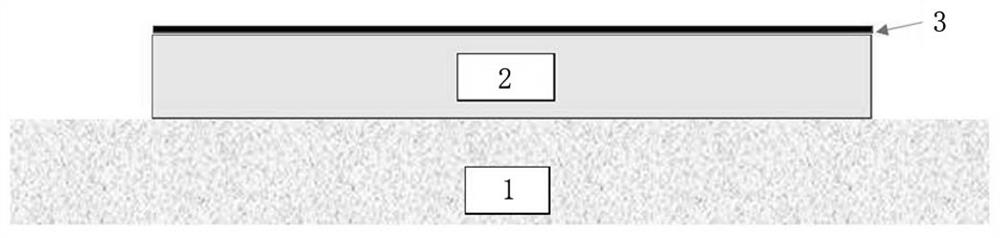

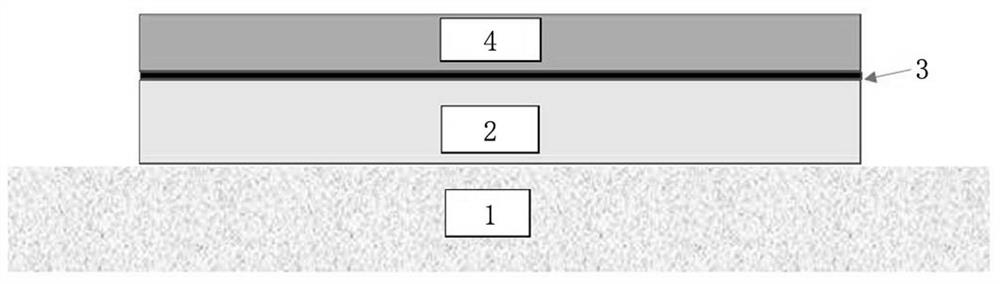

[0037] figure 1 The structure of the lower electrode 2 and the pre-annealing intercalation layer 3 is given. During the preparation process, the lower electrode 2 is first grown on a silicon-based or silicon dioxide substrate 1. This article uses m...

Embodiment 2

[0042] In this example, after the zirconia intercalation is prepared, the device is pre-annealed at a high temperature of 200 degrees Celsius. After the intercalation is prepared, the hafnium-zirconium-oxygen functional layer of 10 nanometers is grown in the atomic layer deposition (atomic layer deposition) instrument. In this step, 100 pulse cycles are grown (a single growth is larger than 0.1 nm), and the cycle method is superimposed growth of 5 hafnium oxide pulse cycles plus five zirconia pulse cycles, and then a triangle with a period of 1 millisecond is added to the upper and lower electrodes of the sample. Pulse, the pulse is first increased from 0V to 3V, then reduced from 3V to -3V, and then increased to 0V. Pulse waveform such as Figure 7 As shown, the period is 1 millisecond. The current is collected while the pulse is applied. After the current is collected, it is integrated, and the sum of the integrated current is divided by the area of the electrode to conv...

Embodiment 3

[0044] In this embodiment, after the 2nm zirconia intercalation layer is grown, the sample is moved to a high-temperature rapid annealing furnace, and in a nitrogen atmosphere, the temperature is raised to 400 degrees Celsius at a rate of 20 degrees Celsius per second, and kept for one minute. Rapid anneal after one minute. When the temperature drops to 50 degrees Celsius, the sample is taken out, and then the functional layer is prepared. After the sample is taken out, the upper electrode is prepared, and finally annealed at the second high temperature. Move the sample into a high-temperature rapid annealing furnace, and raise the temperature to 500 degrees Celsius at a rate of 20 degrees Celsius per second in a nitrogen atmosphere, and keep it for one minute. Rapid anneal after one minute. When the temperature retreated to 50 degrees Celsius, the samples were taken out. Apply a triangular pulse with a period of 1 millisecond to the upper and lower electrodes of the sample....

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More