Patents

Literature

39results about How to "Increase storage window" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Resistive random access memory based on organic/inorganic hybrid perovskite material and fabrication method of resistive random access memory

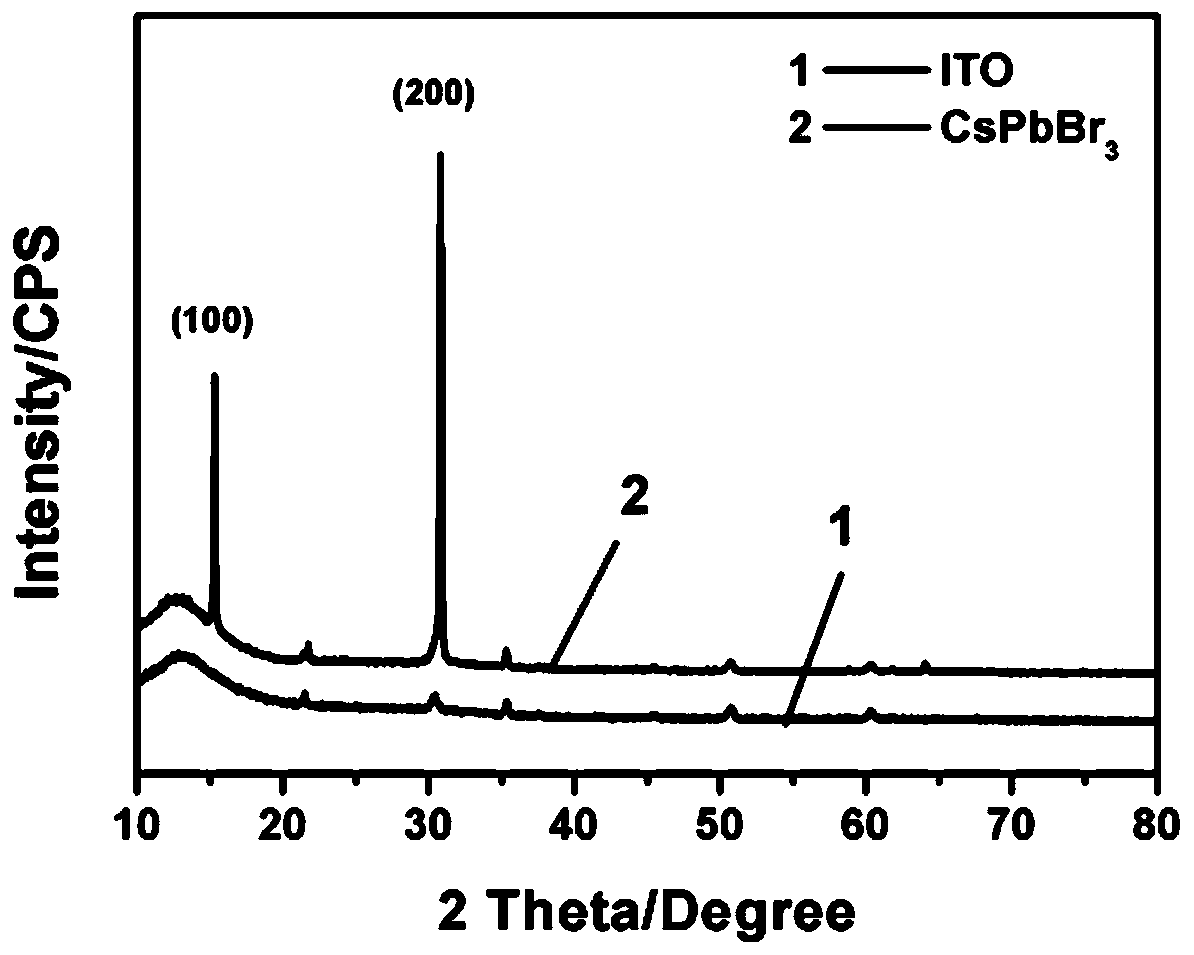

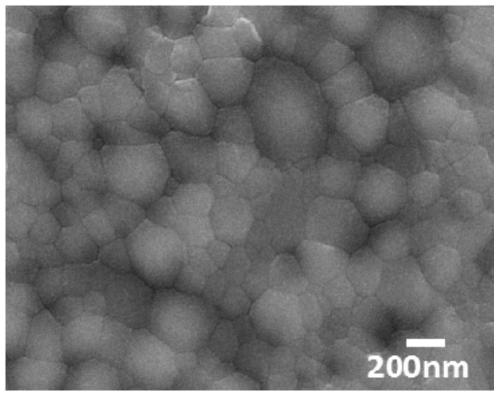

ActiveCN105789434ASimple structureImprove thermal stabilityElectrical apparatusStatic random-access memoryGas phase

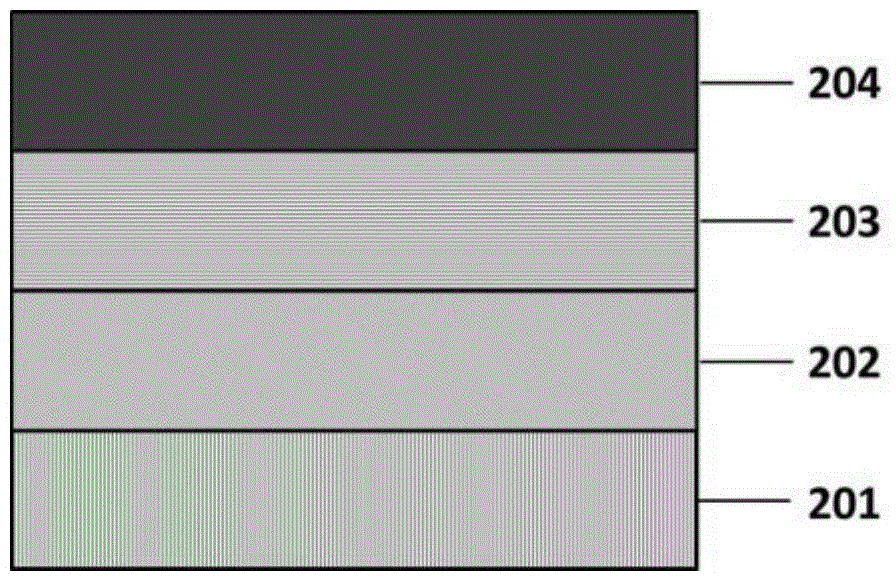

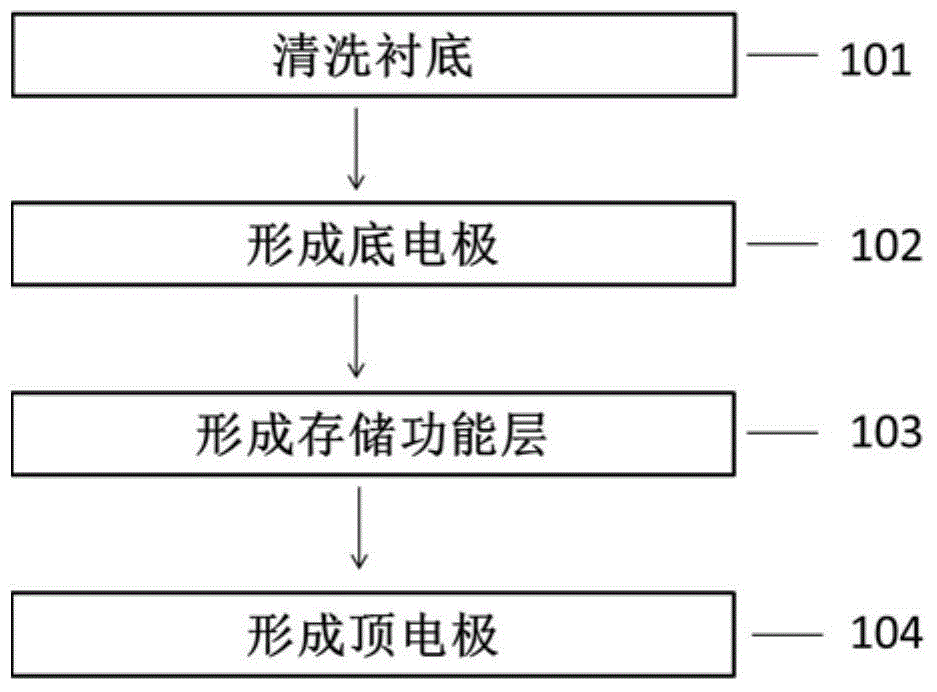

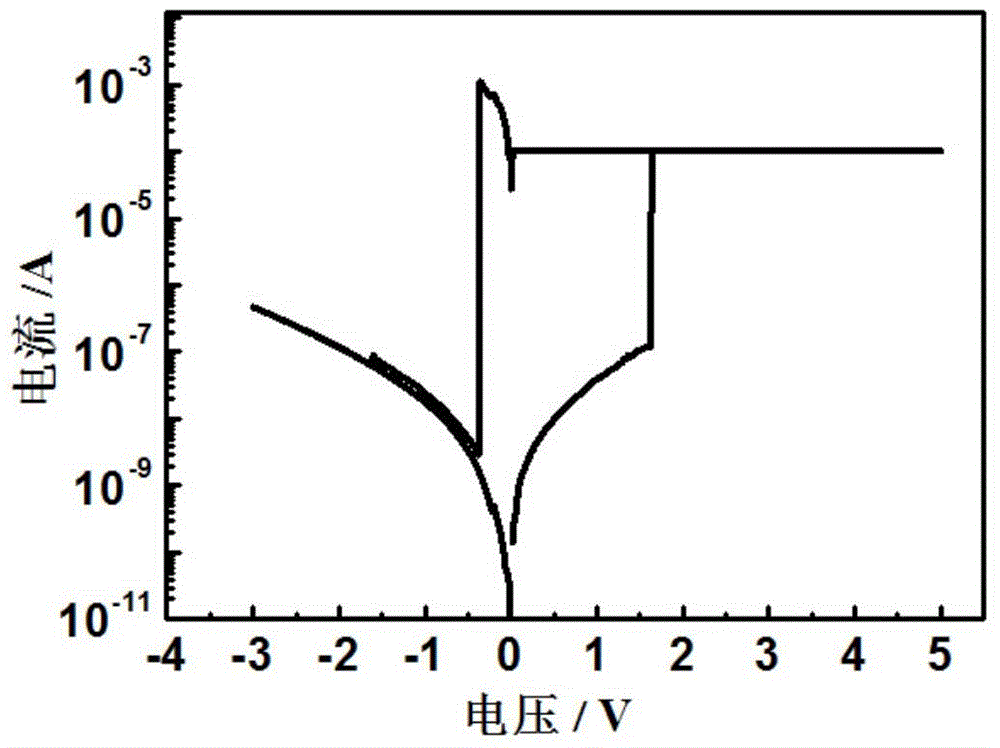

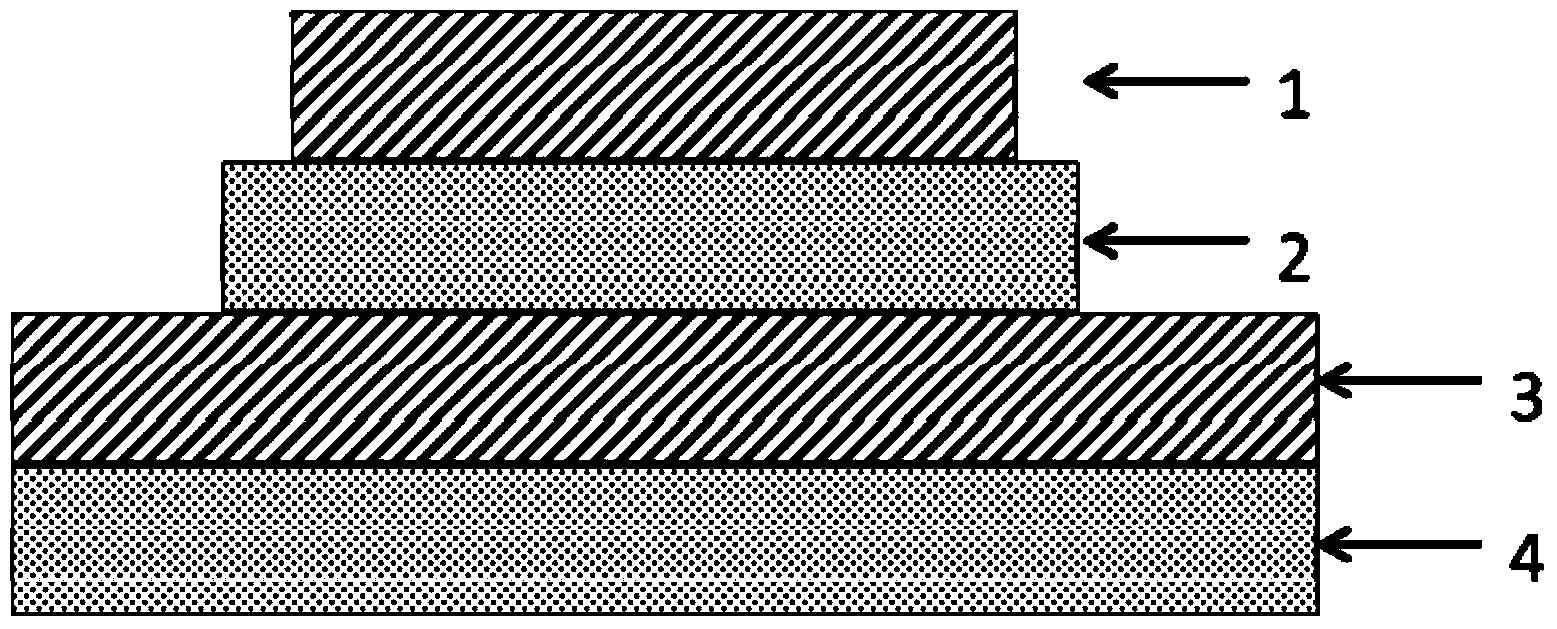

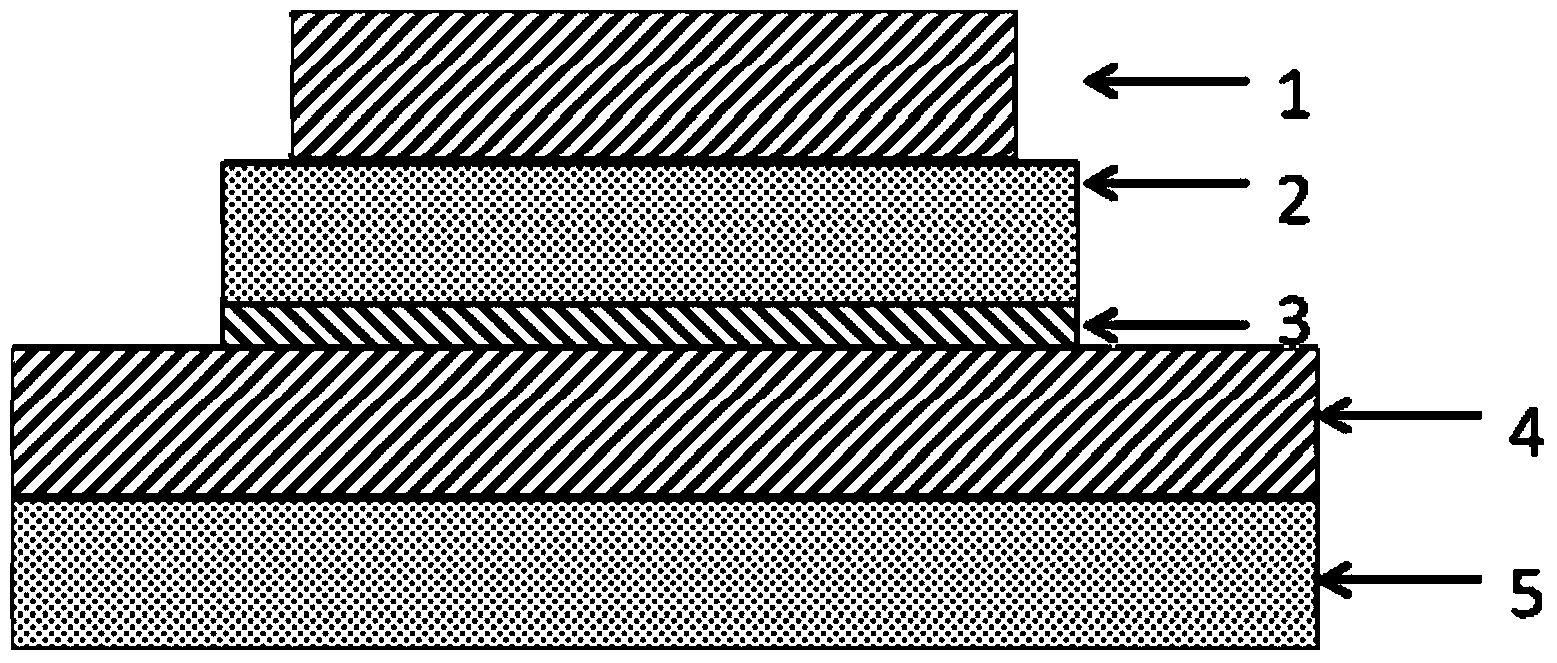

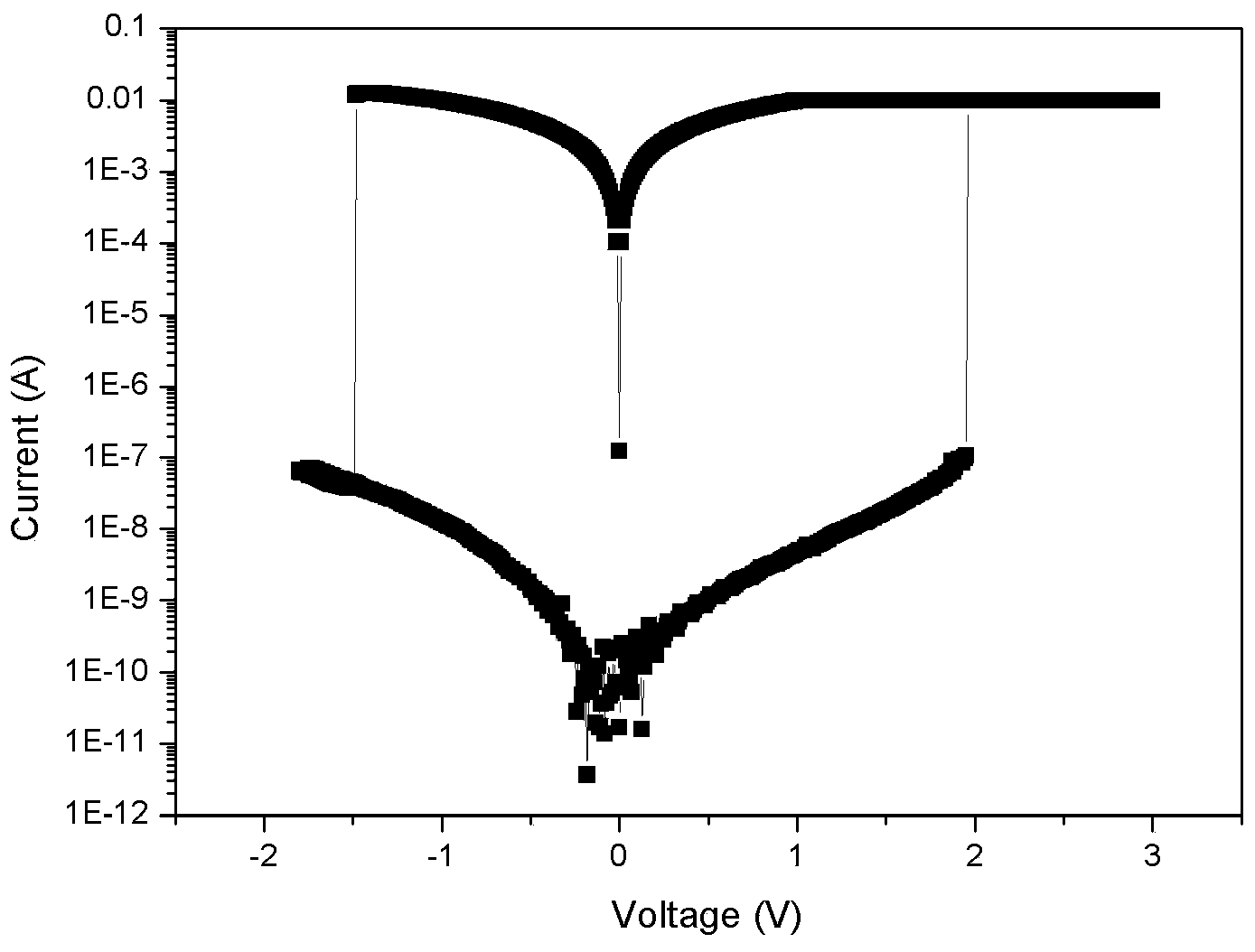

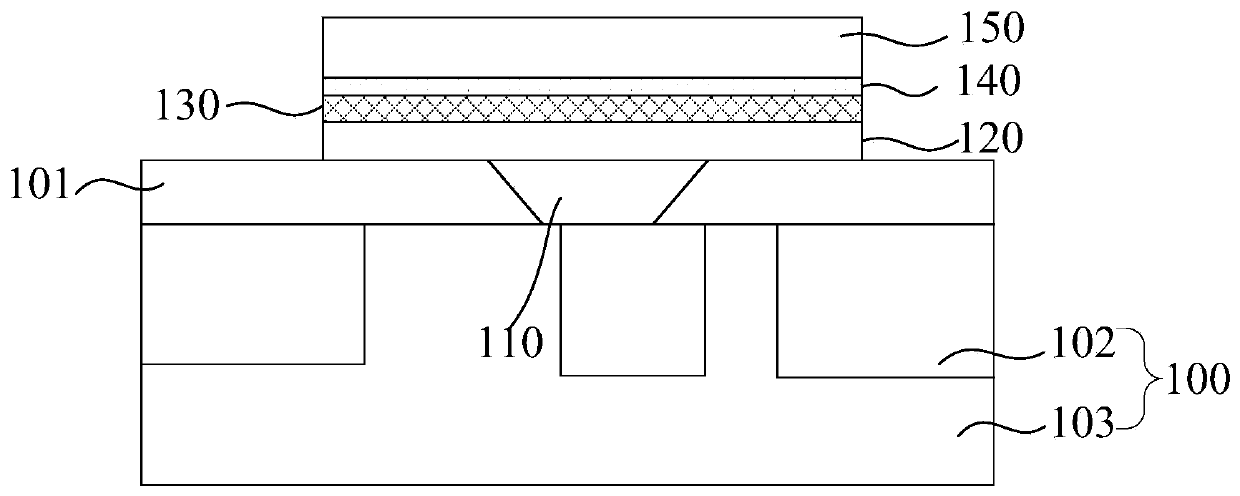

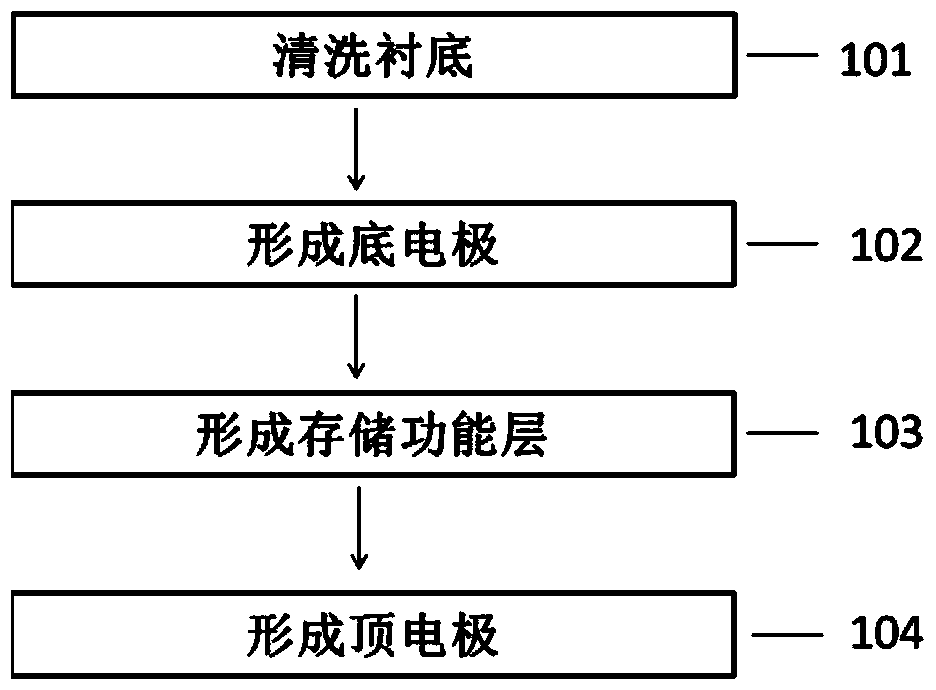

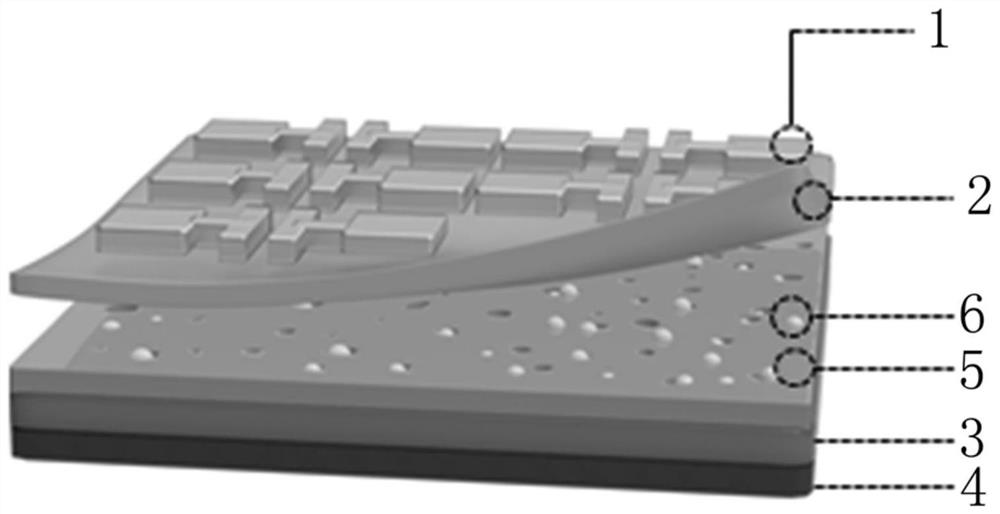

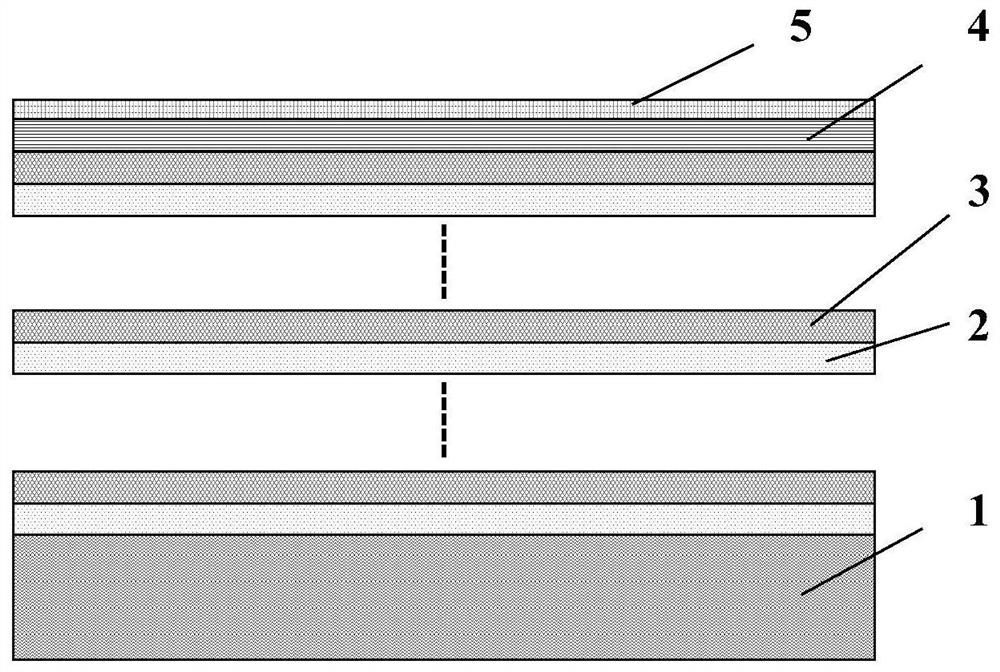

The invention discloses a resistive random access memory based on an organic / inorganic hybrid perovskite material and a fabrication method of the resistive random access memory. The resistive random access memory comprises a bottom electrode, a top electrode and a resistance changing functional layer material, wherein the resistance changing functional layer material is arranged between the bottom electrode and the top electrode and comprises one layer or multiple layers of organic / inorganic hybrid perovskite thin film materials. The fabrication method comprises the following steps of (1) cleaning a substrate; (2) depositing the bottom electrode on the substrate by employing a physical vapor deposition technique; (3) forming the organic / inorganic hybrid perovskite thin film material on the bottom electrode as a resistance changing functional layer by techniques such as spin coating, dip coating and vacuum evaporation; and (4) depositing the top electrode on the resistance changing functional layer by employing the physical vapor deposition technique. According to the resistive random access memory, the structure is simple, and low-temperature and low-cost fabrication can be carried out; and the fabricated device has the technical advantages of large memory window, low conversion voltage, high conversion speed, multi-value storage capability, favorable thermal stability and device durability and the like.

Owner:GRIMAT ENG INST CO LTD

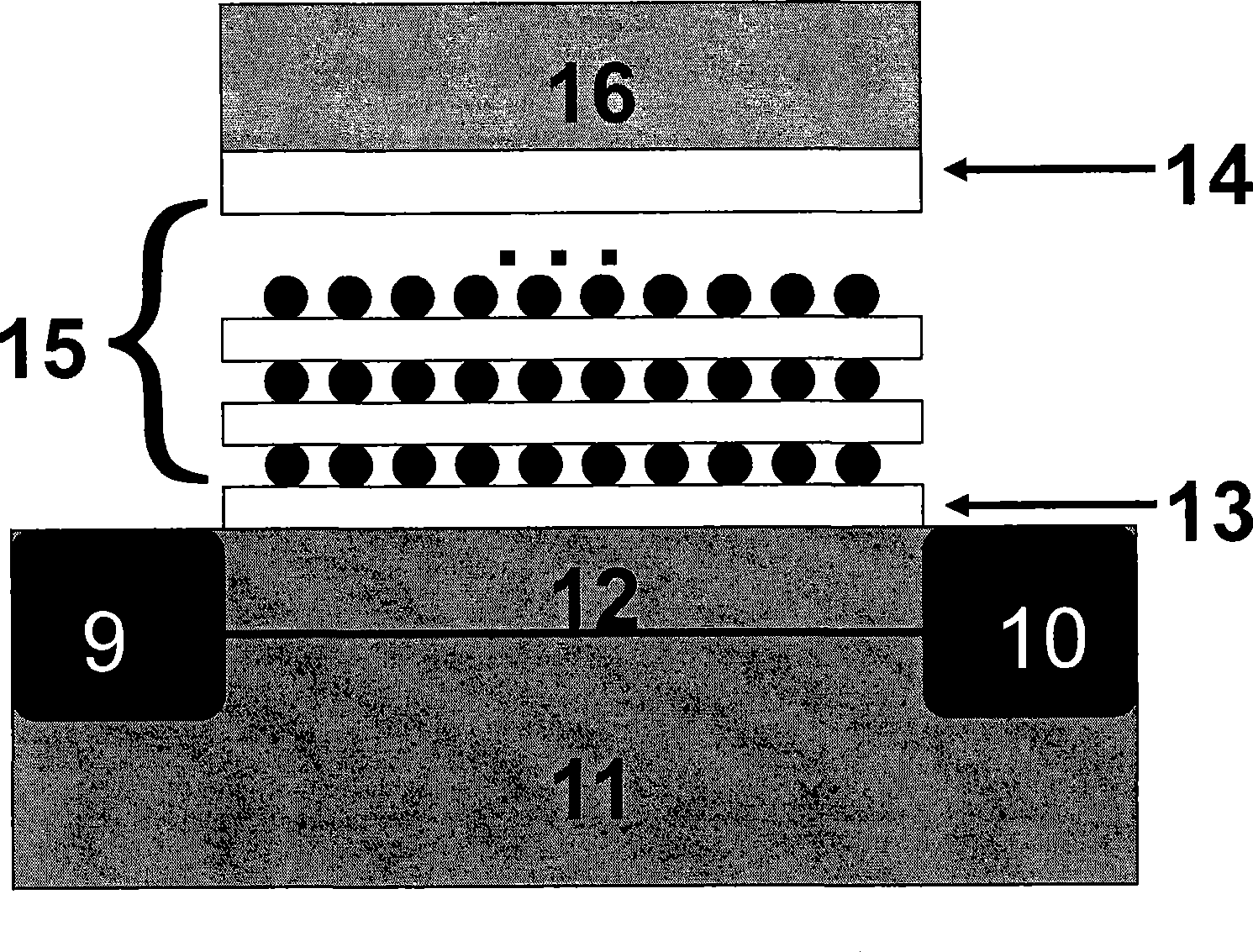

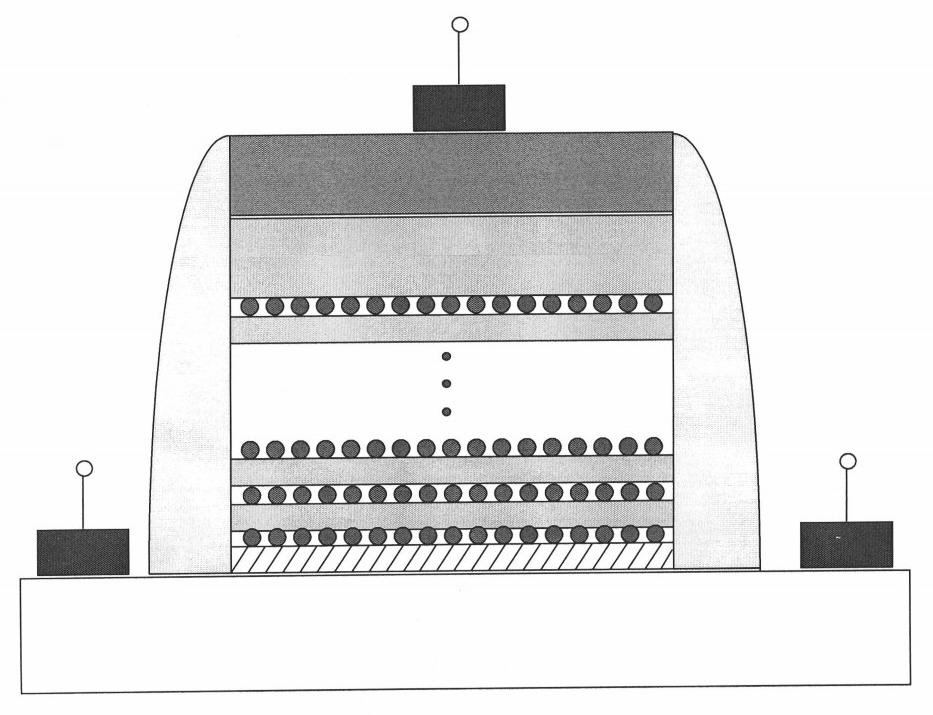

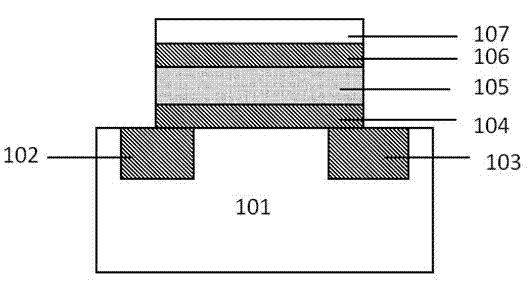

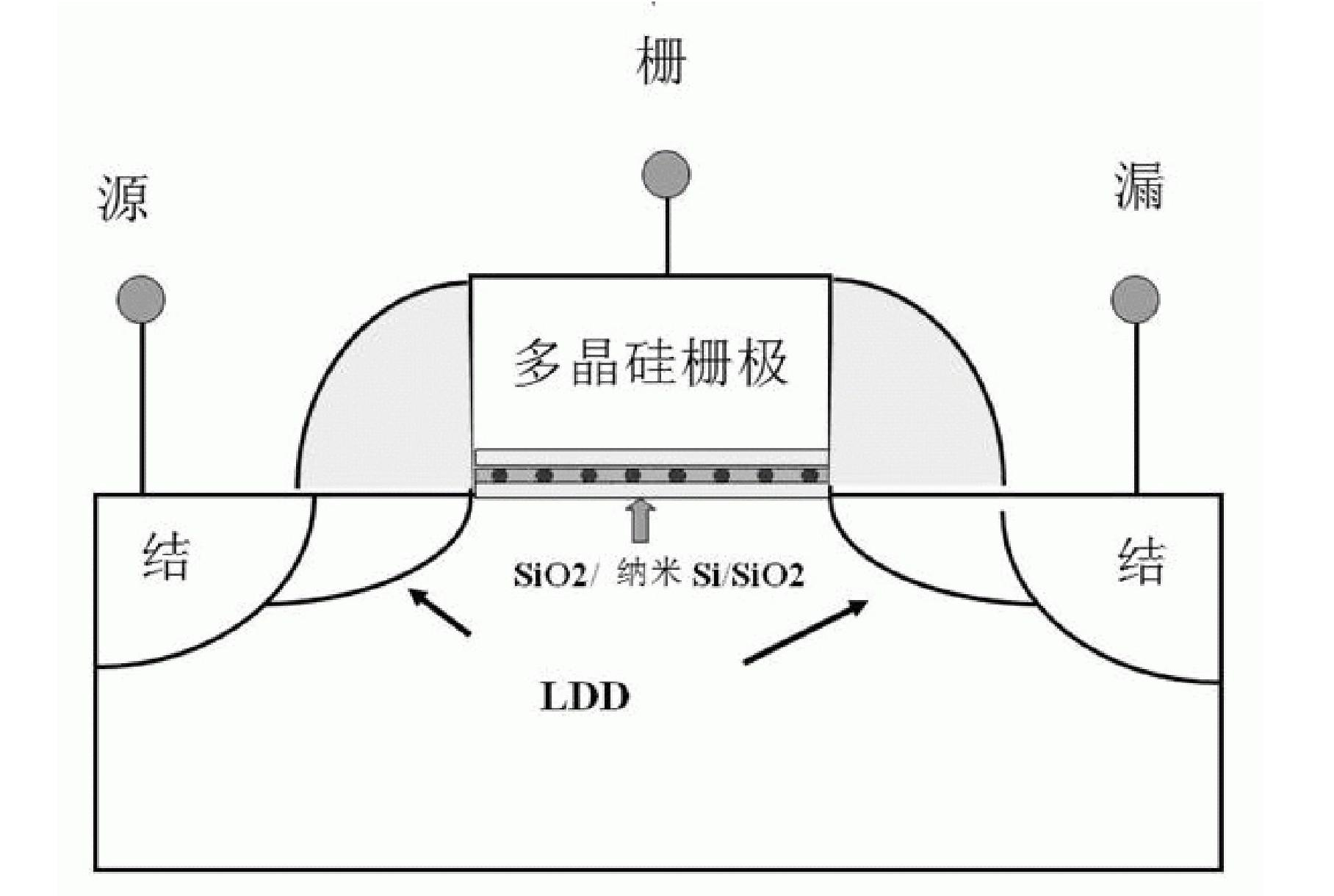

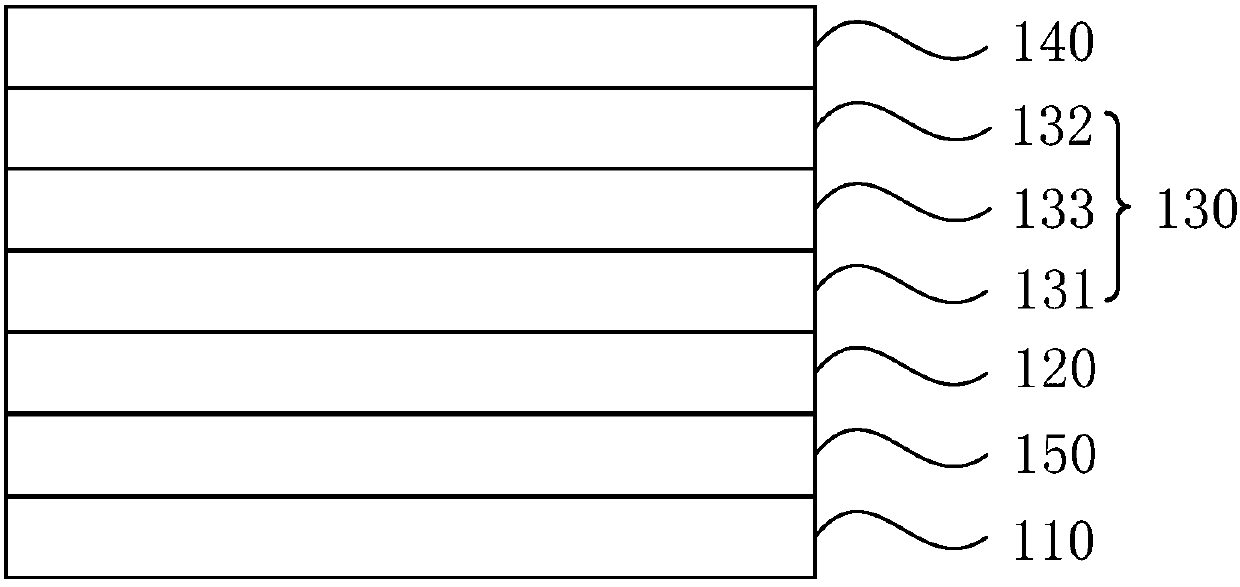

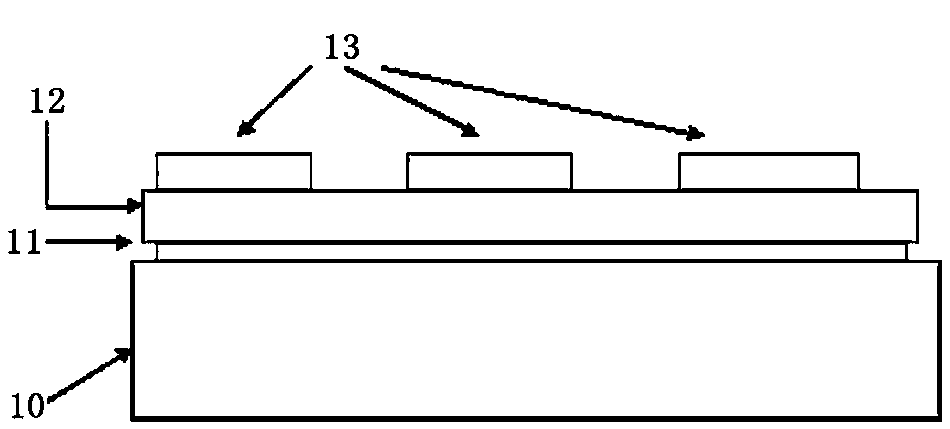

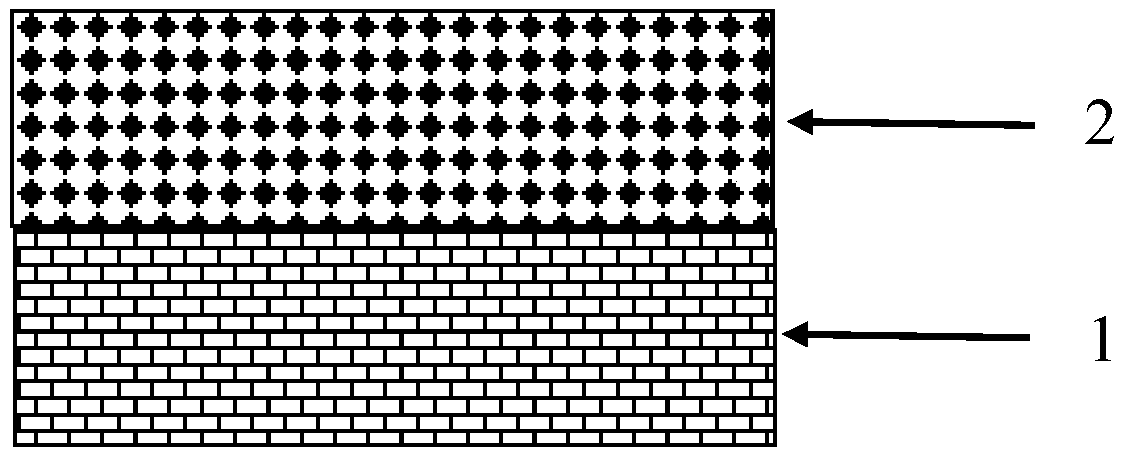

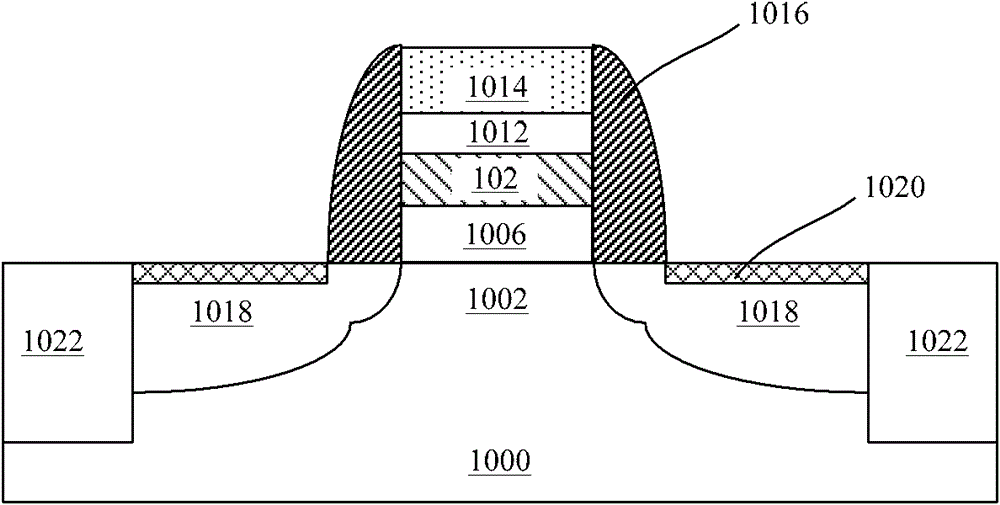

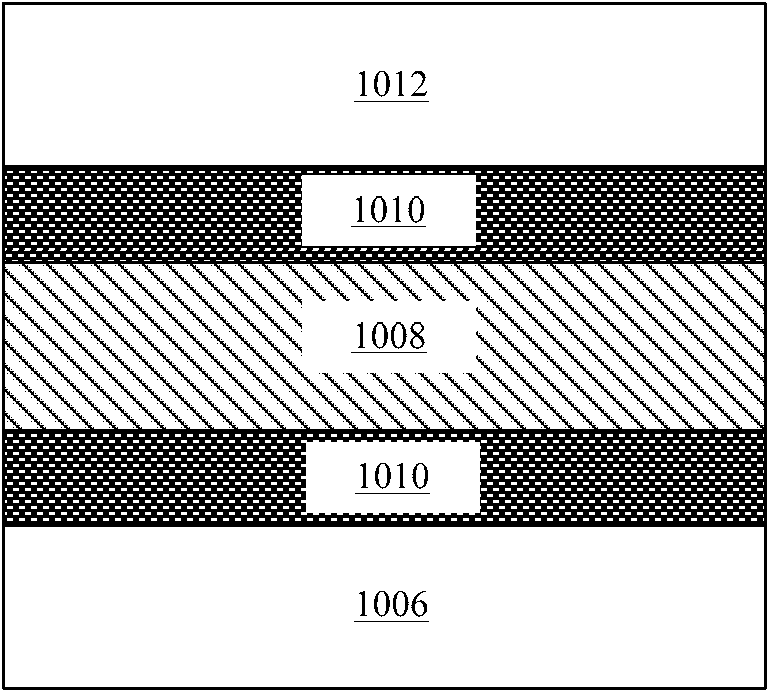

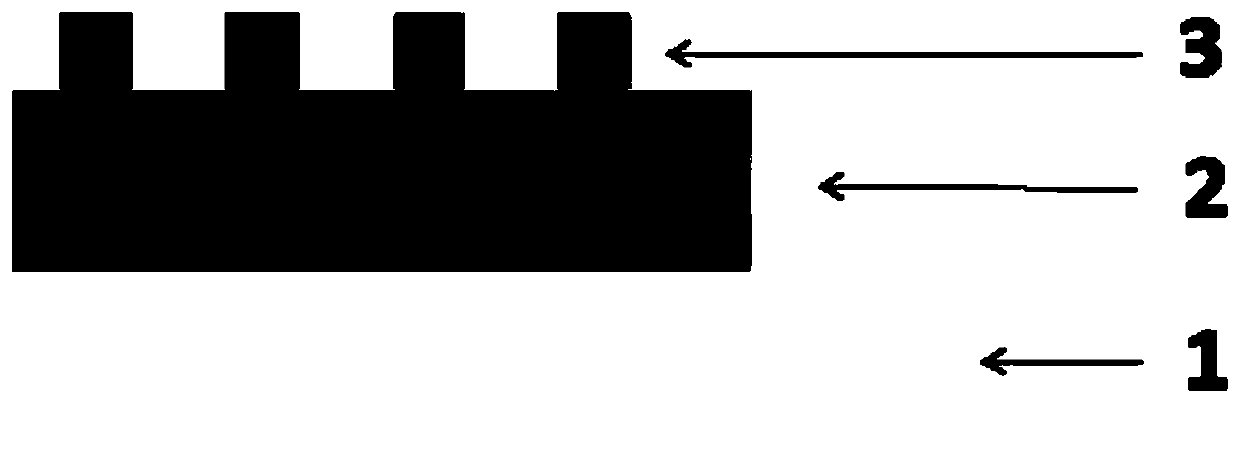

Non-volatile memory of multi-layered nano-crystal floating gate structure

InactiveCN101383378AIncrease the number ofIncrease storage windowTransistorSolid-state devicesComputer architectureNanocrystal

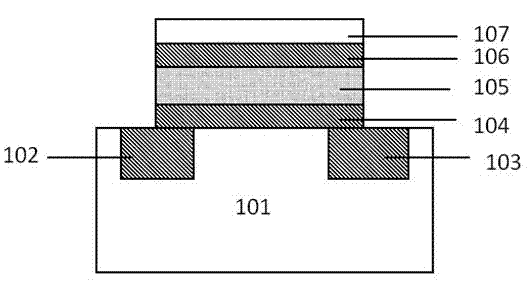

The invention discloses a nonvolatile memory with a multi-layer nanocrystal floating gate structure, which belongs to the technical field of the nonvolatile memory. The nonvolatile memory comprises a semiconductor substrate 11 used for supporting the entire nonvolatile memory, a source 9 and a drain 10 which are formed in the semiconductor substrate 11 in a doped way, a channel 12 between the source 9 and the drain 10, a tunneling oxidizing layer 13 positioned on the channel 12, a control oxidizing layer 14 used for controlling oxidation of the multi-layer nanocrystal floating gate structure, a gate electrode 16 positioned on the control oxidizing layer 14 and a multi-layer nanocrystal floating gate structure 15 positioned between the tunneling oxidizing layer 13 and the control oxidizing layer 14 and used as the floating gate storage unit of the nonvolatile memory. The invention also discloses a method for preparing the nonvolatile memory with the multi-layer nanocrystal floating gate structure. The invention solve the contradiction between the programming time / voltage of the single-layer nanocrystal floating gate memory and the storage time, and increases the storage time of the element under the precondition of shorter programming time.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

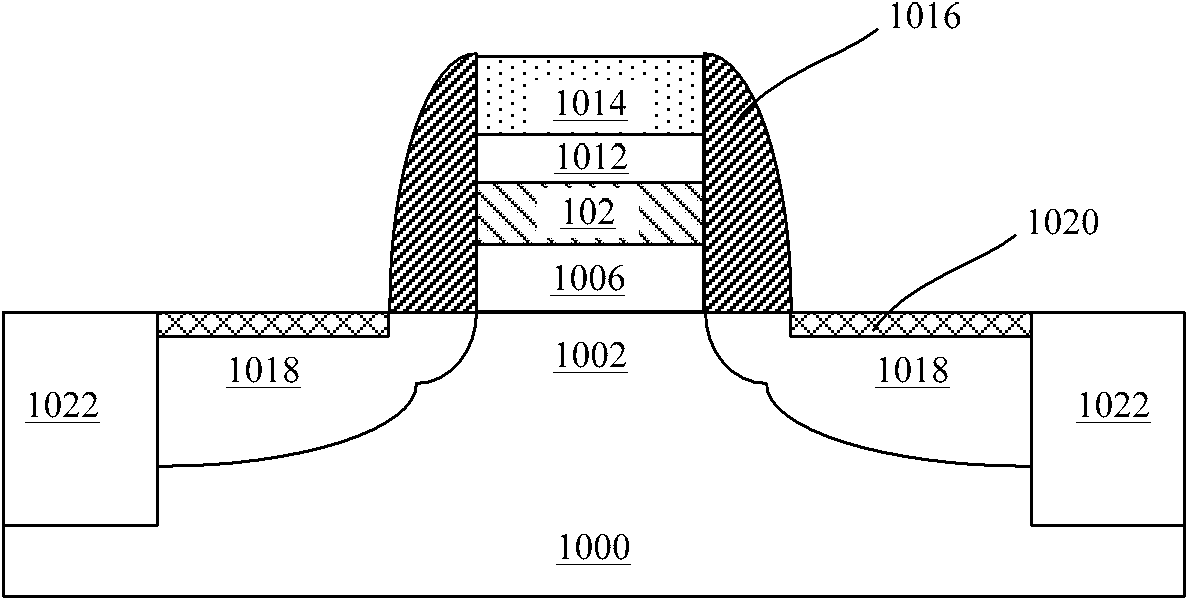

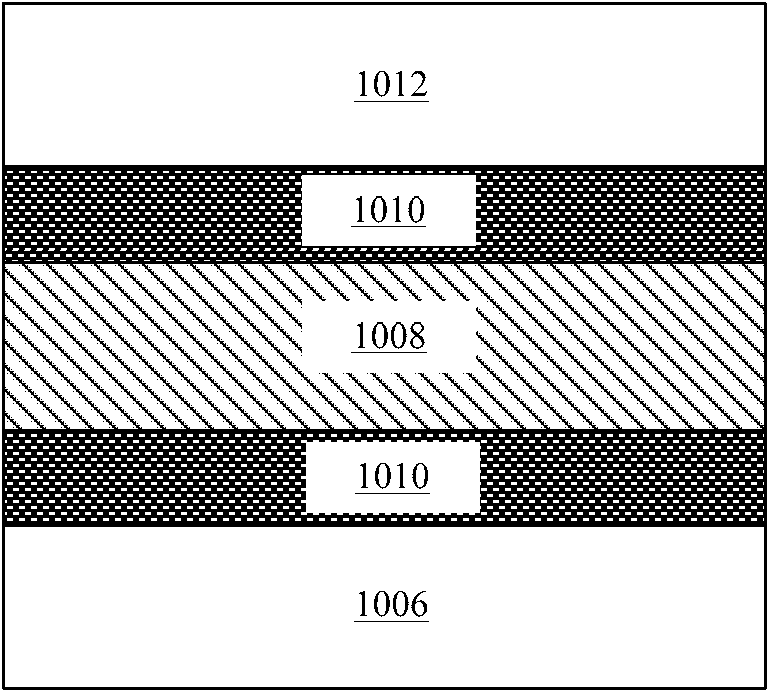

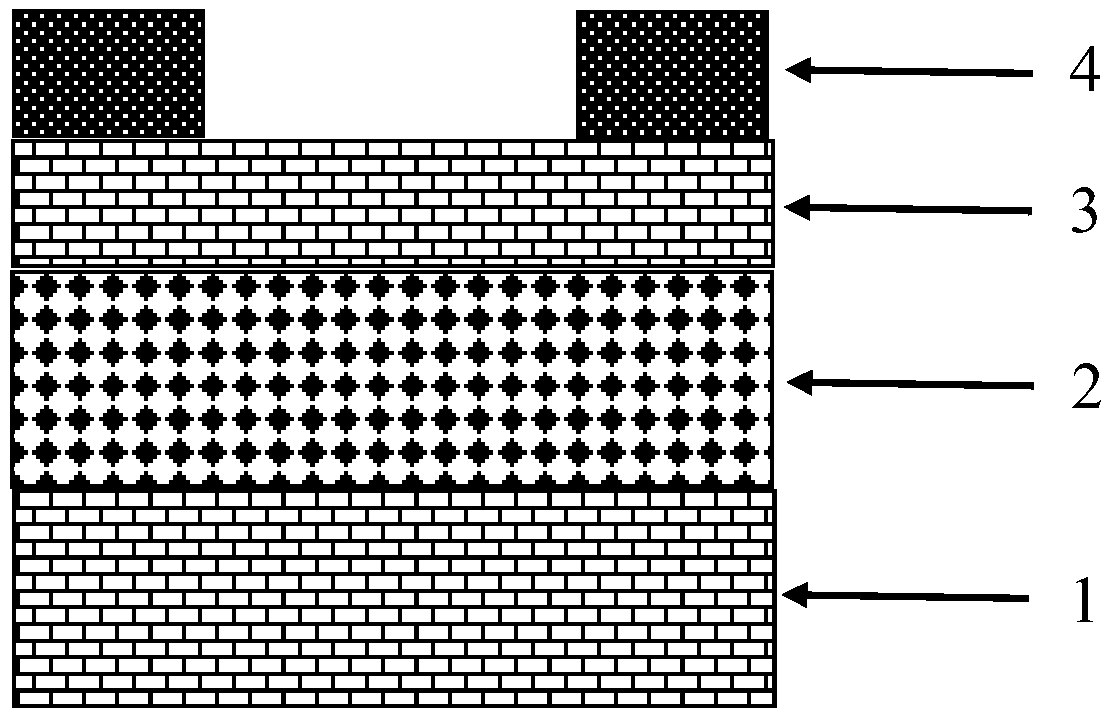

Memory and manufacturing method thereof

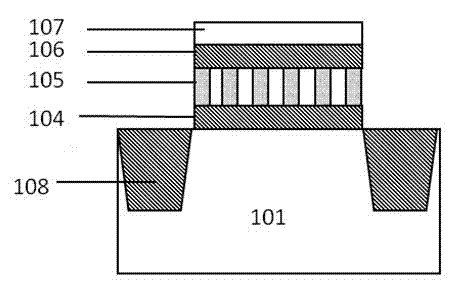

ActiveCN102810541AIncrease the number of capturesHigh densitySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorGrating

The invention discloses a memory and a manufacturing method of the memory. The memory structurally comprises a semiconductor substrate, a channel region, a grating stack and a source region or a drain region, wherein the channel region is arranged on the semiconductor substrate; the grating stack is arranged on the channel region and comprises a tunneling layer, a charge trapping layer, a barrier layer and a gate electrode layer; the tunneling layer is arranged on the channel region; the charge trapping layer is arranged on the tunneling layer; the barrier layer is arranged on the charge trapping layer; the gate electrode layer is arranged on the barrier layer; the source region or the drain region is arranged on two sides of the channel region and is embedded in the semiconductor substrate; and the charge trapping layer comprises a first charge trapping layer and a second charge trapping layer(s), wherein the second charge trapping layers which are arranged above or / and below the first charge trapping layer.

Owner:ZHUHAI CHUANGFEIXIN TECH CO LTD

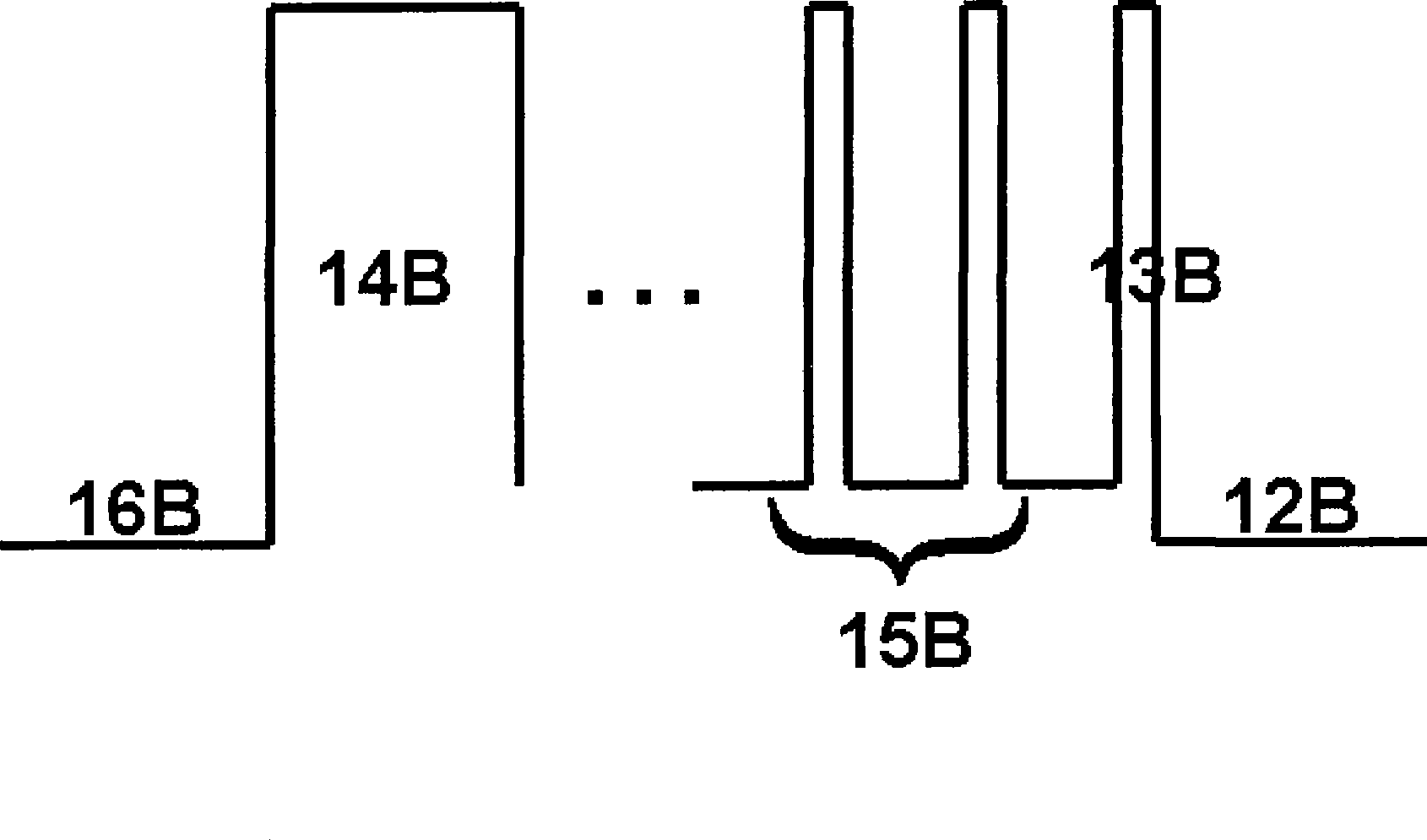

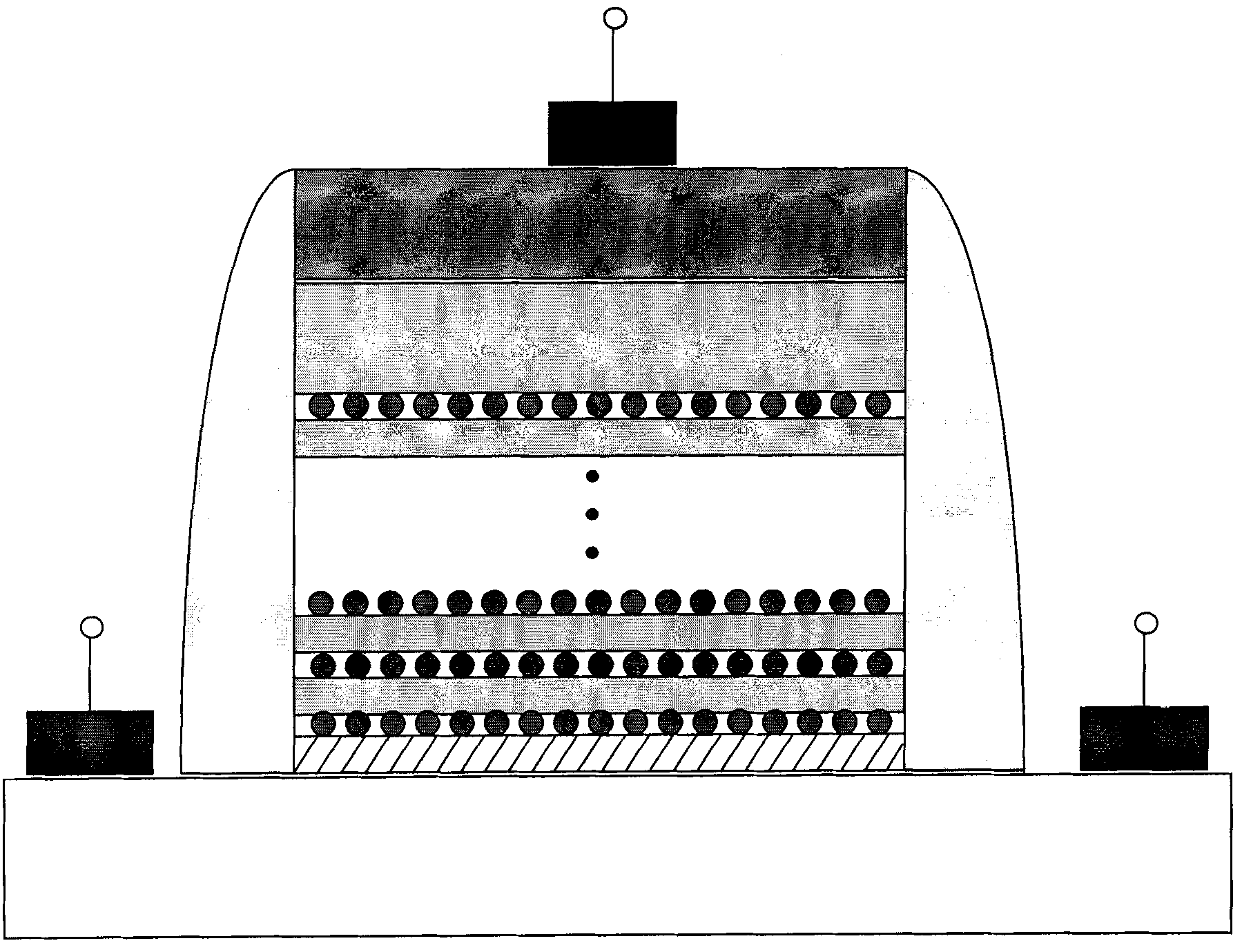

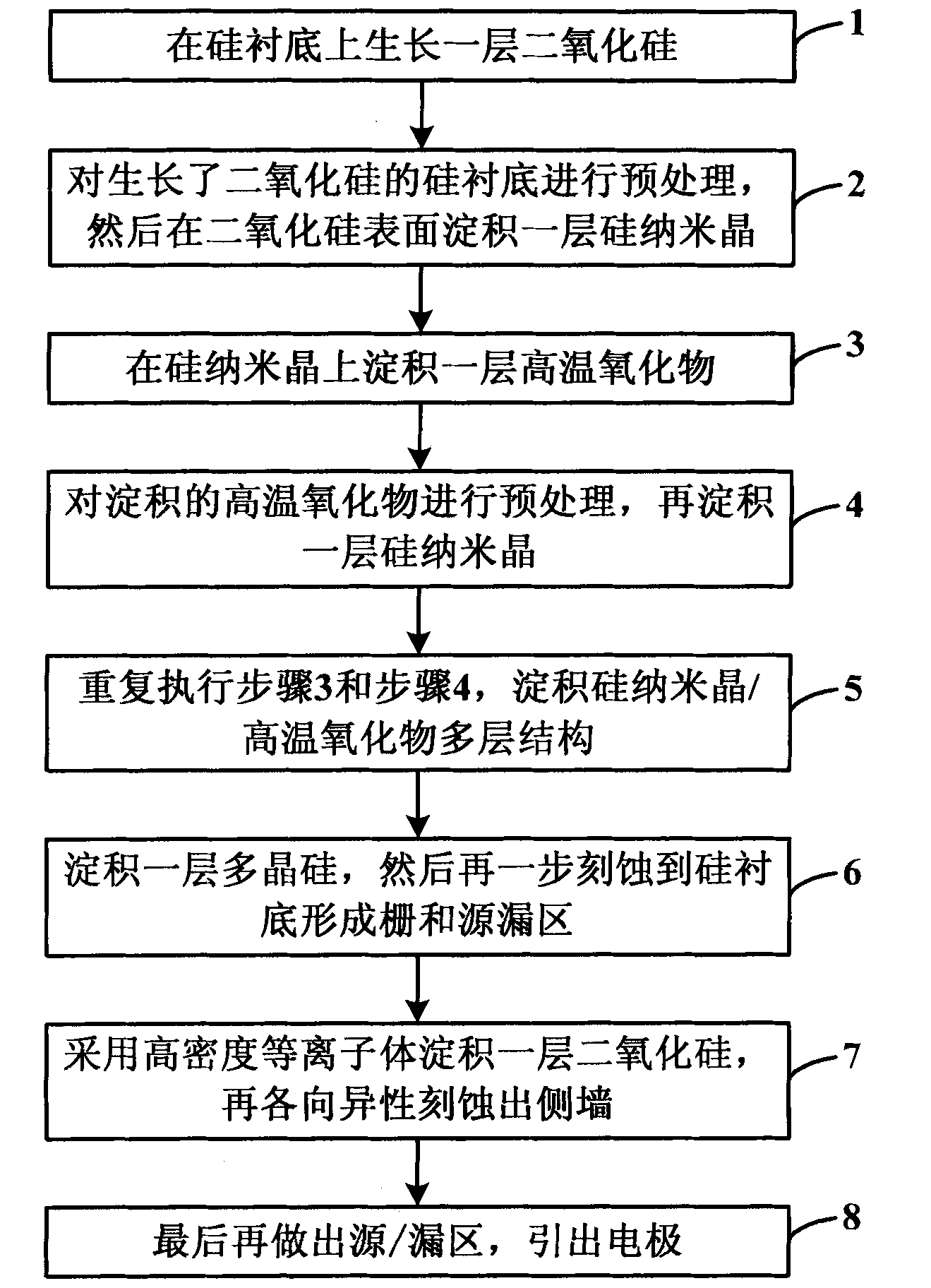

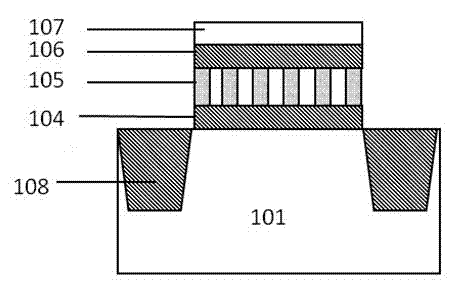

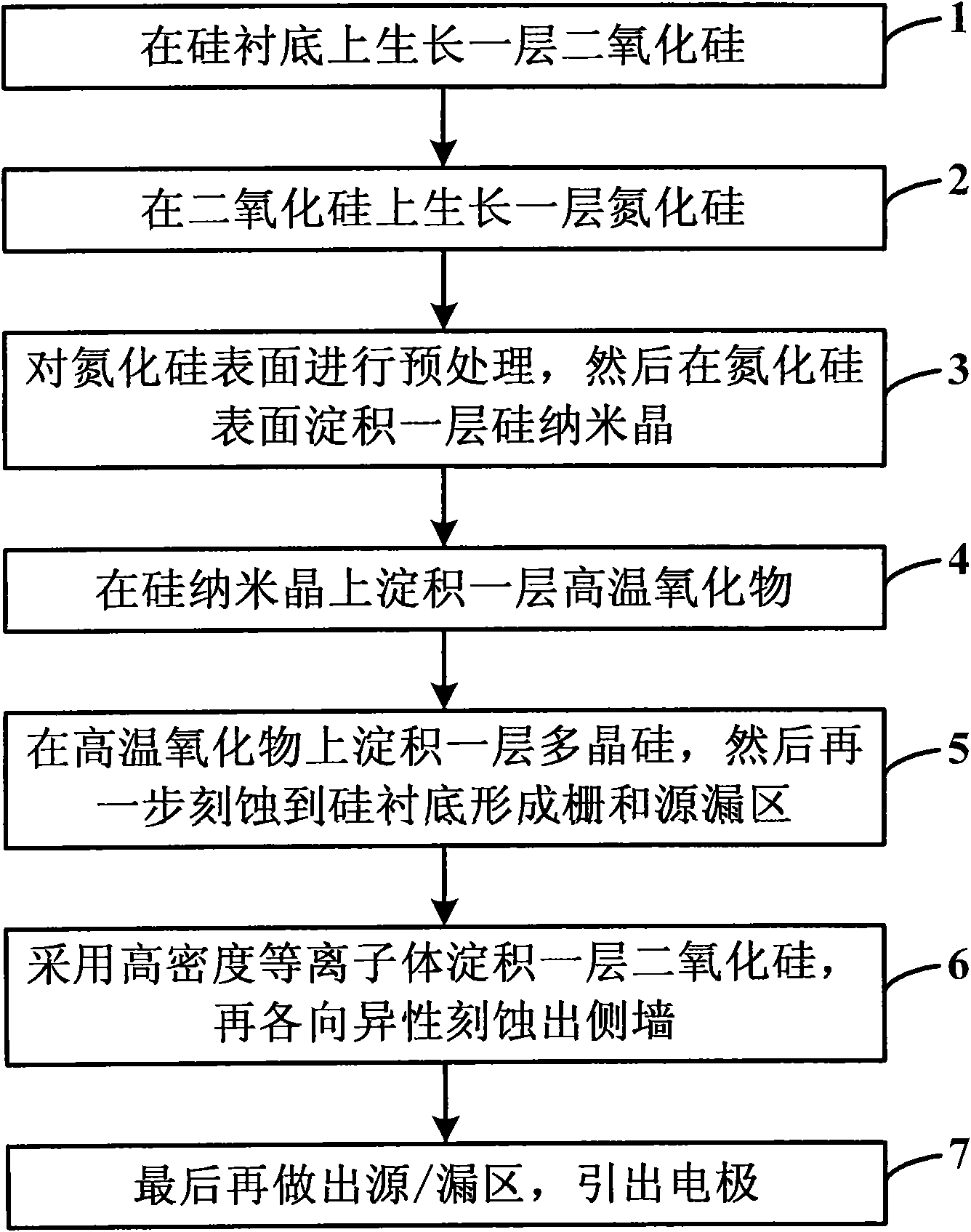

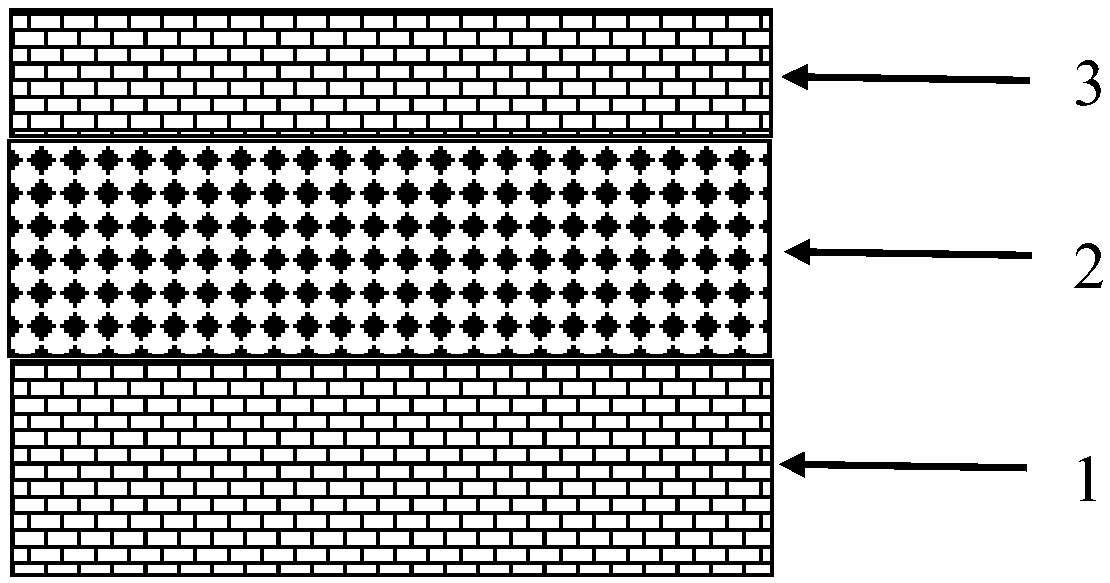

Multi-layer floating gate nonvolatile memory structure and production method thereof

InactiveCN101814505AHigh densityIncrease storage windowSolid-state devicesSemiconductor/solid-state device manufacturingSilicon nanocrystalsSilicon dioxide

The invention discloses a multi-layer floating gate nonvolatile memory structure and a production method thereof, wherein the multi-layer floating gate nonvolatile memory structure comprises a silicon substrate, a silicon dioxide layer, a silicon nanocrystals / high temperature oxide multilayer structure, a polysilicon layer, a silicon dioxide layer, grid and source / drain region formed by sculpturing on the silicon substrate, and a side wall formed by sculpturing on the silicon dioxide layer. The invention solves the defects because the traditional Flash technology node can downsized, utilizes the multi-layer floating gate to storage charge to enhance a storage window, so that the reliability of the floating grid for storing charge can be increased and the retention performance of a floating device can be improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

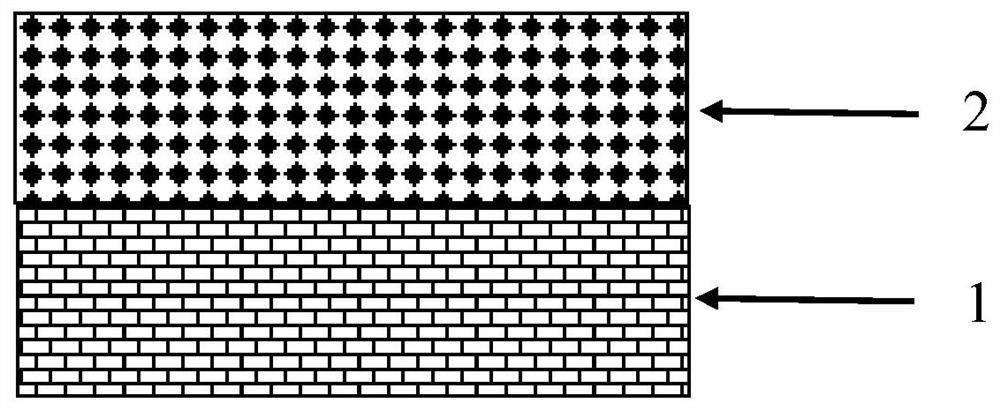

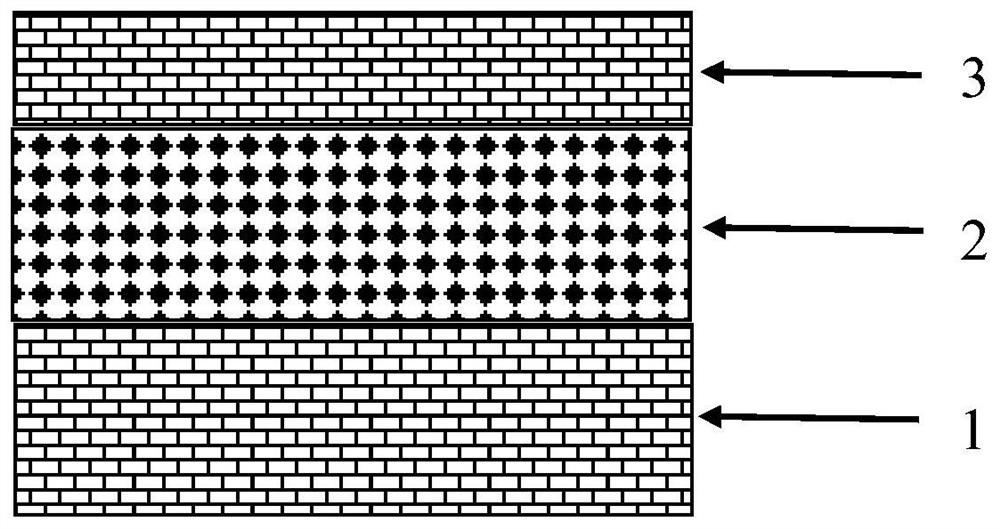

Multistage resistive random access memory and manufacturing method thereof

InactiveCN103915565AImprove stabilityReduce dissipationElectrical apparatusNanoinformaticsElectrical resistance and conductanceStatic random-access memory

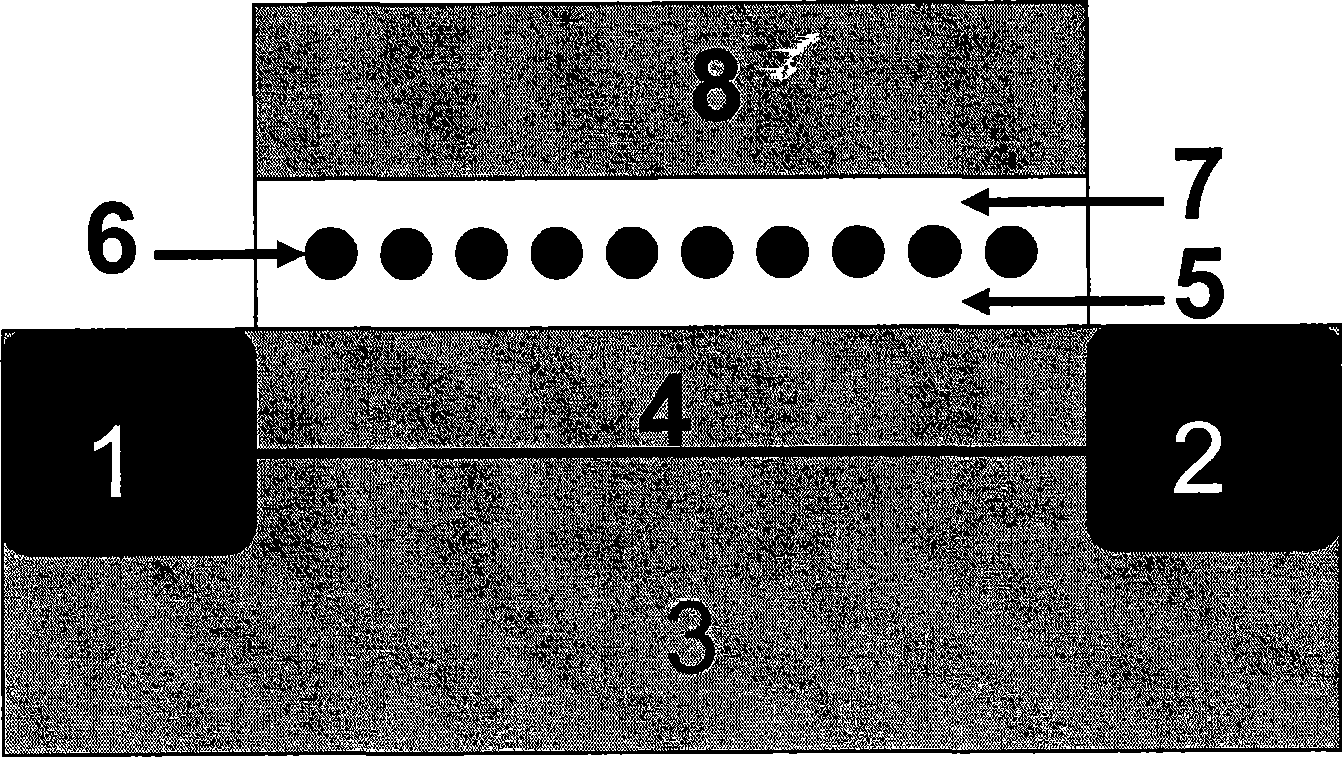

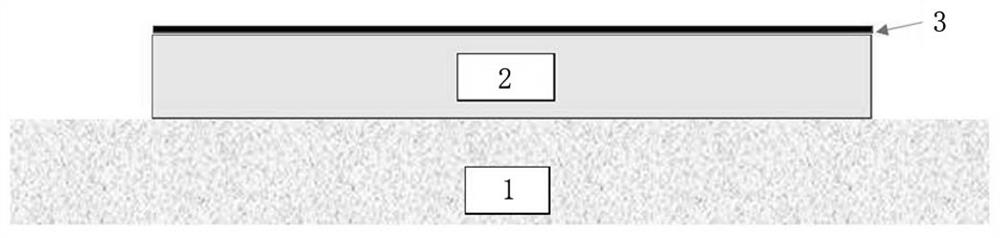

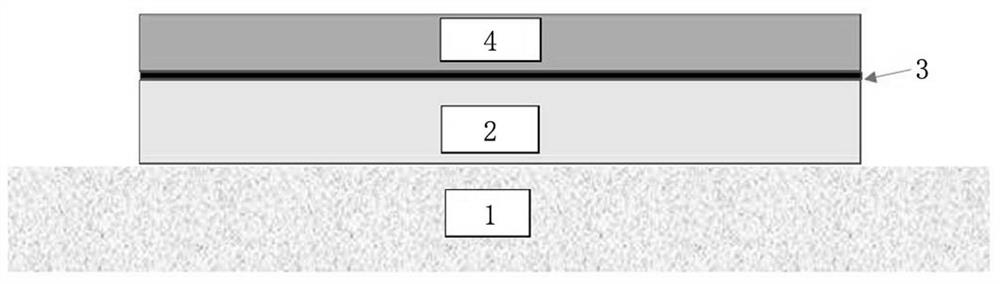

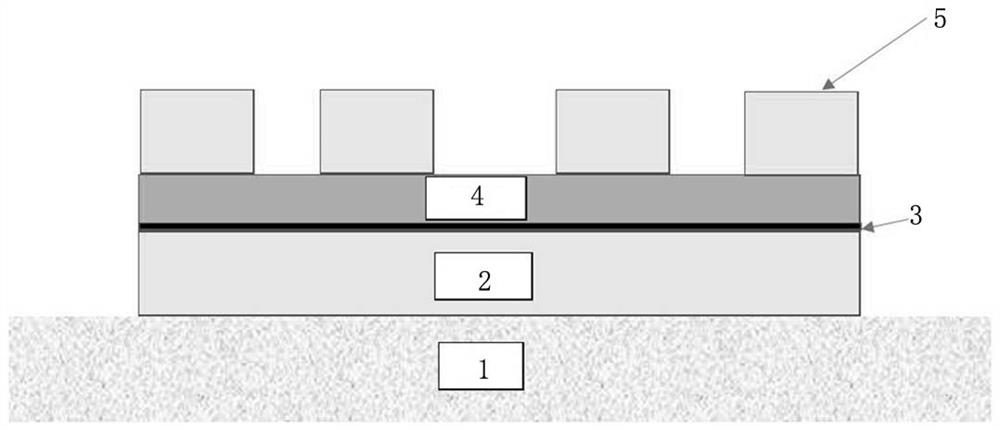

The invention aims to provide a multistage resistive random access memory and a manufacturing method of the multistage resistive random access memory. The multistage resistive random access memory comprises a substrate, a bottom electrode, a resistive layer and a top electrode, wherein the substrate, the bottom electrode, the resistive layer and the top electrode are arranged from bottom to top in sequence. The multistage resistive random access memory is characterized in that an isolation layer is further arranged between the bottom electrode and the resistive layer. According to the multistage resistive random access memory and the manufacturing method of the multistage resistive random access memory, the nanoscale isolation layer is additionally arranged, so that the magnitude of a storage window of the resistive random access memory is increased to over 105, and the primary condition needed by multistage storage is met; electrochemical active materials are used as the top electrode, different resistance states are achieved under the condition of different voltage drives through the drifting character of the electrochemical active materials, and the purpose of multistage storage is achieved; in addition, due to the additional arrangement of the isolation layer, dissipation of oxygen ions in the movement process is reduced, the bottom electrode is effectively protected, and the stability of a device is improved. In addition, the manufacturing method of the multistage resistive random access memory is simple and easy to control.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

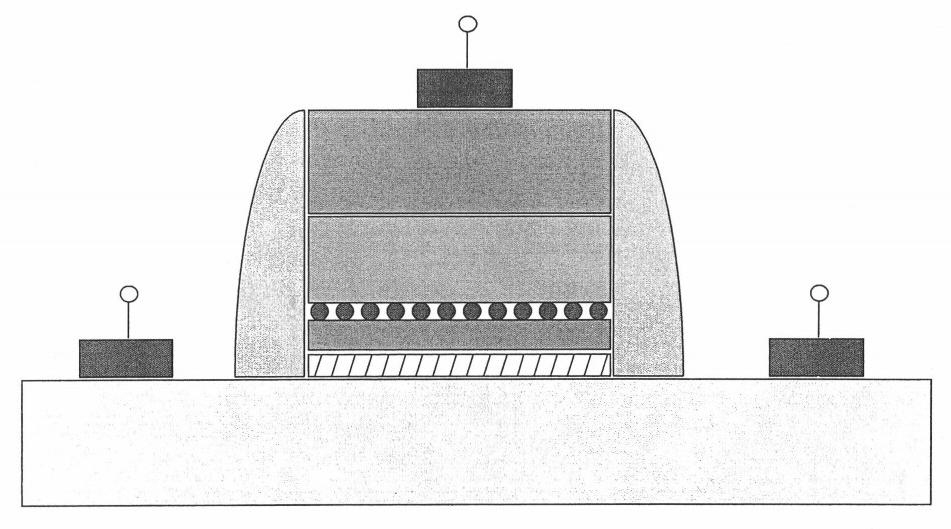

Multiple-valued non-volatile memory and preparation method thereof

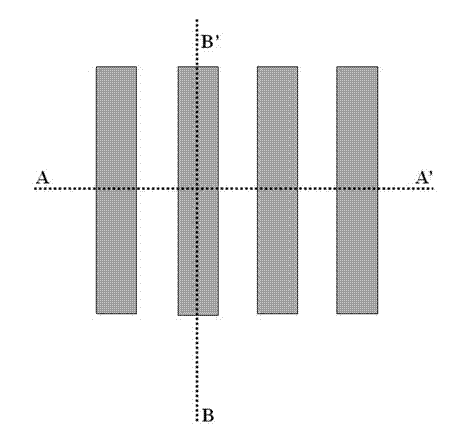

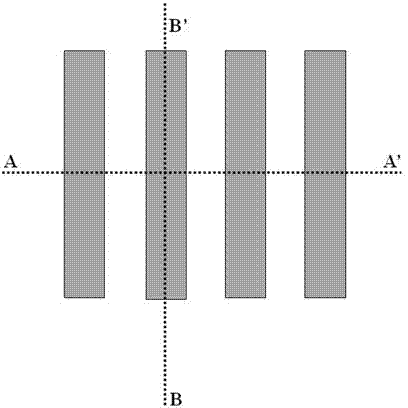

ActiveCN102693984ALow Program Erase VoltageGood programming and erasing speedSolid-state devicesSemiconductor/solid-state device manufacturingMulti valuedHigh density storage

The invention relates to a multiple-valued non-volatile memory and a preparation method thereof. The memory comprises a semiconductor substrate, wherein both ends of the semiconductor substrate include a source electrode and a drain electrode respectively along the direction of a memory bit line and both ends of the semiconductor substrate include a shallow tunnel isolation structure respectively along the direction of a memory sub-line. A tunneling dielectric layer, a charge storage layer, a charge blocking layer, and a gate electrode are sequentially arranged on the semiconductor substrate, wherein the charge storage layer is a combination of two different storage materials which are alternatively arranged along the direction of the memory sub-line. The multiple-valued non-volatile memory of the invention adopts the storage layer formed by alternatively arranging the two different materials, which increases the storage density, promises a large window while reducing the thickness of a gate dielectric layer greatly,. Therefore, multiple-valued storage and high-density storage are realized the cost is reduced in turn.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Composite storage medium floating-gate memory structure and manufacture method thereof

InactiveCN101814506AHigh densityIncrease storage windowTransistorIndividual molecule manipulationSilicon nanocrystalsOptoelectronics

The invention discloses a composite storage medium floating-gate memory structure and a manufacture method thereof. The composite storage medium floating-gate memory structure sequentially comprises the following structures from bottom to top: a silicon substrate, a tunneling medium layer, silicon nitride, silicon nanocrystals, high-temperature oxides, a polysilicon layer, a grid and source / drain region and a side wall, wherein the grid and source / drain region is formed on the silicon substrate through etching, and the side wall is etched on the silicon dioxide layer. When being used, the invention solves the problem of reducibility of nodes in the traditional Flash technology, two storage media are adopted for storing electric charges, and a storage window is enlarged, so the reliability of the floating-gate electric charge storage is improved, and the holding feature of a floating-grate device is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

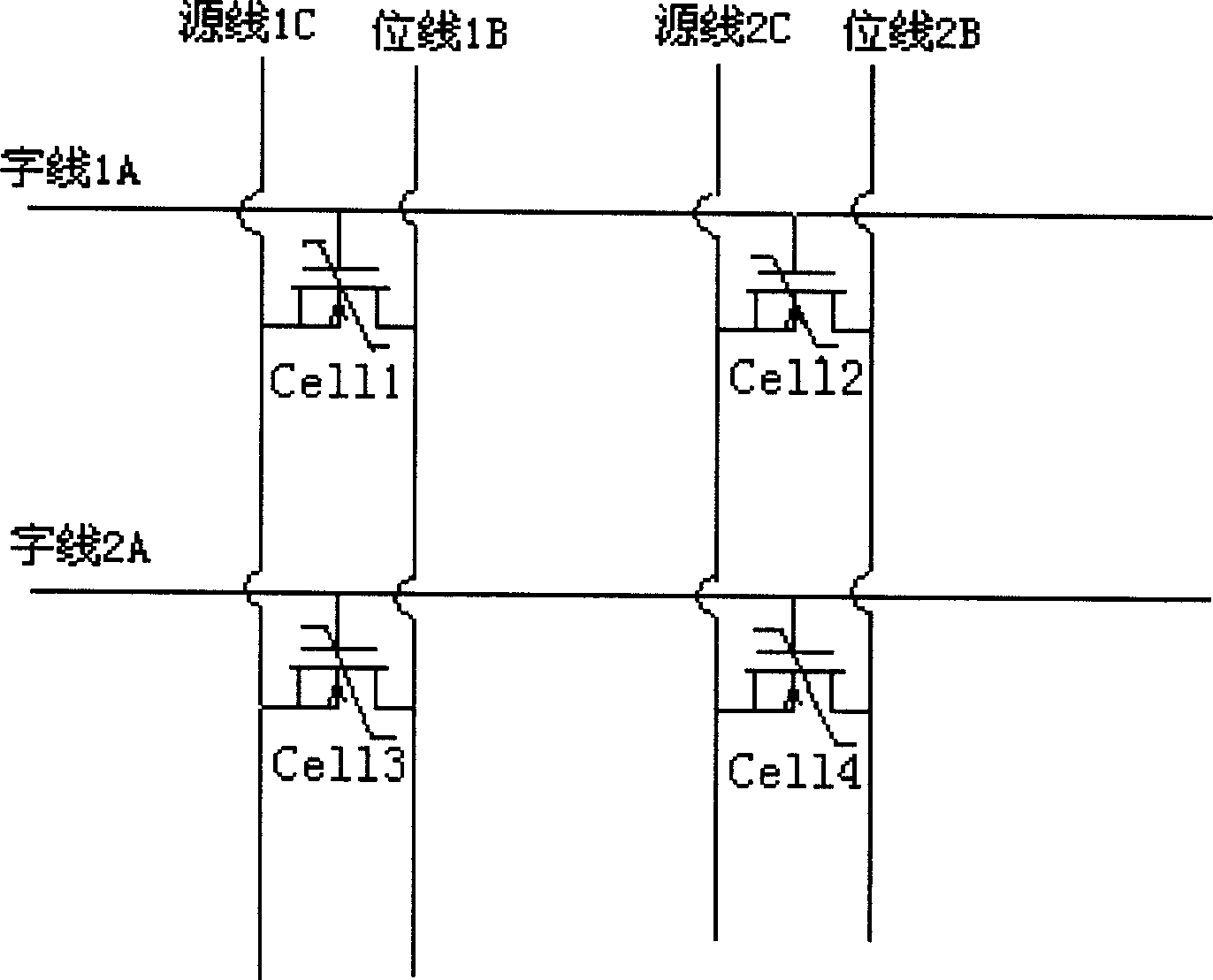

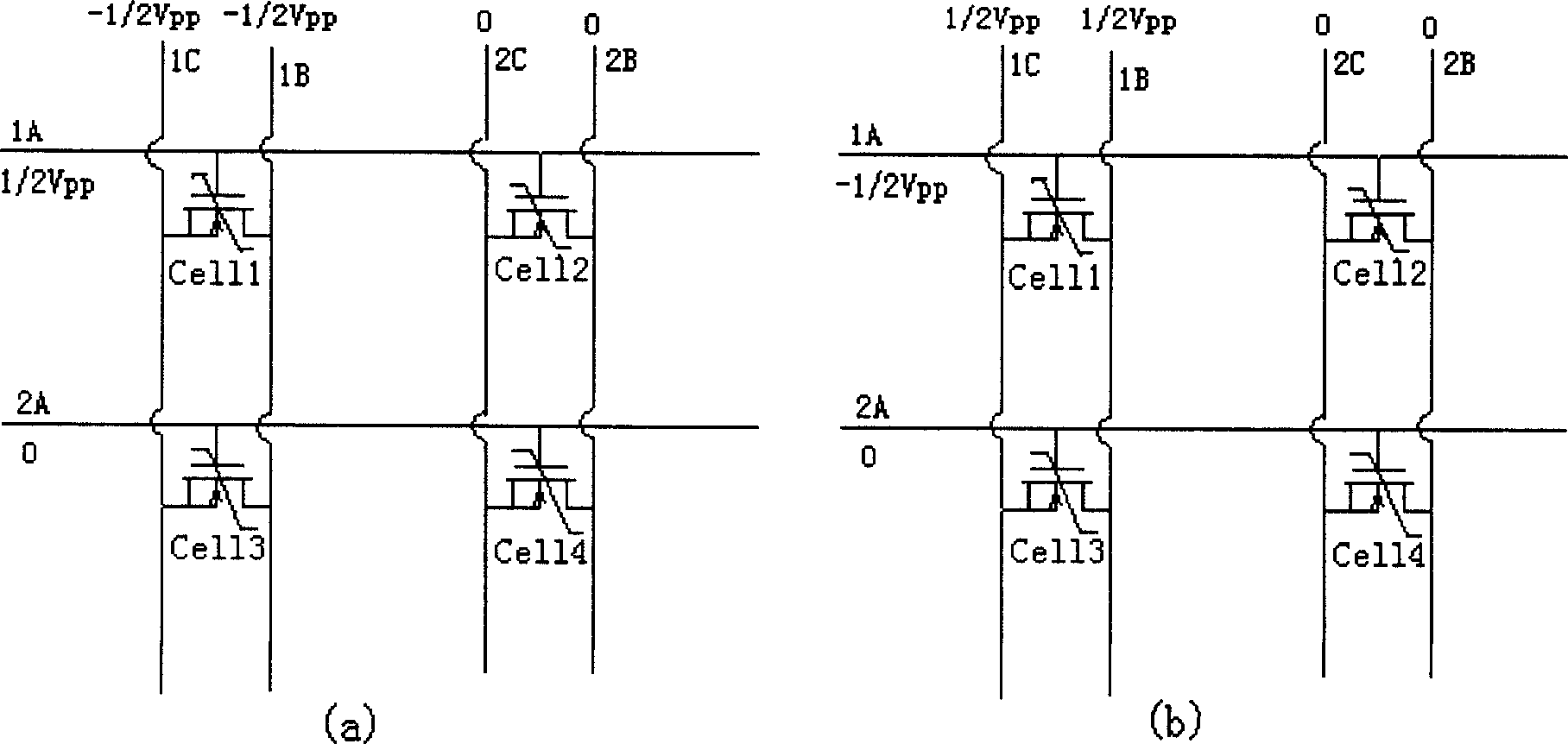

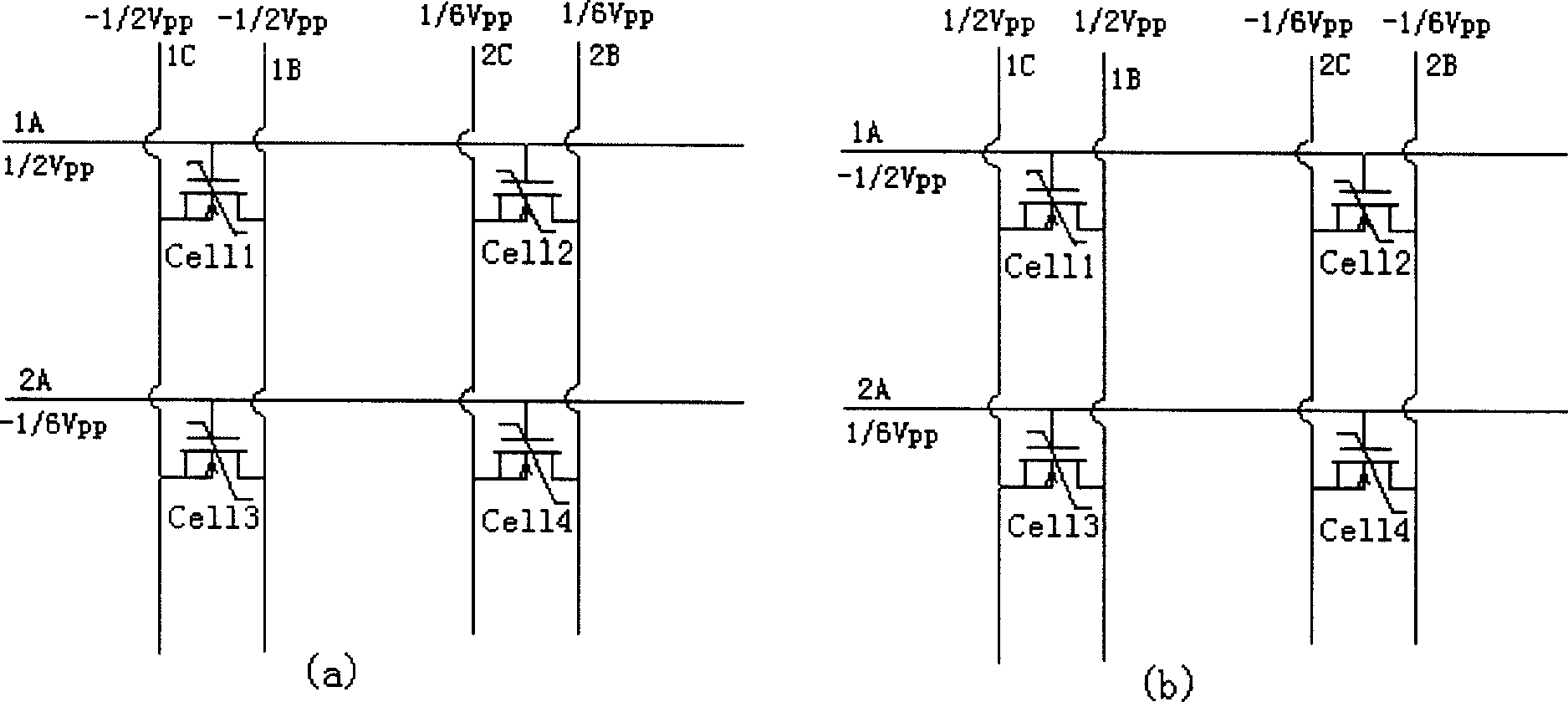

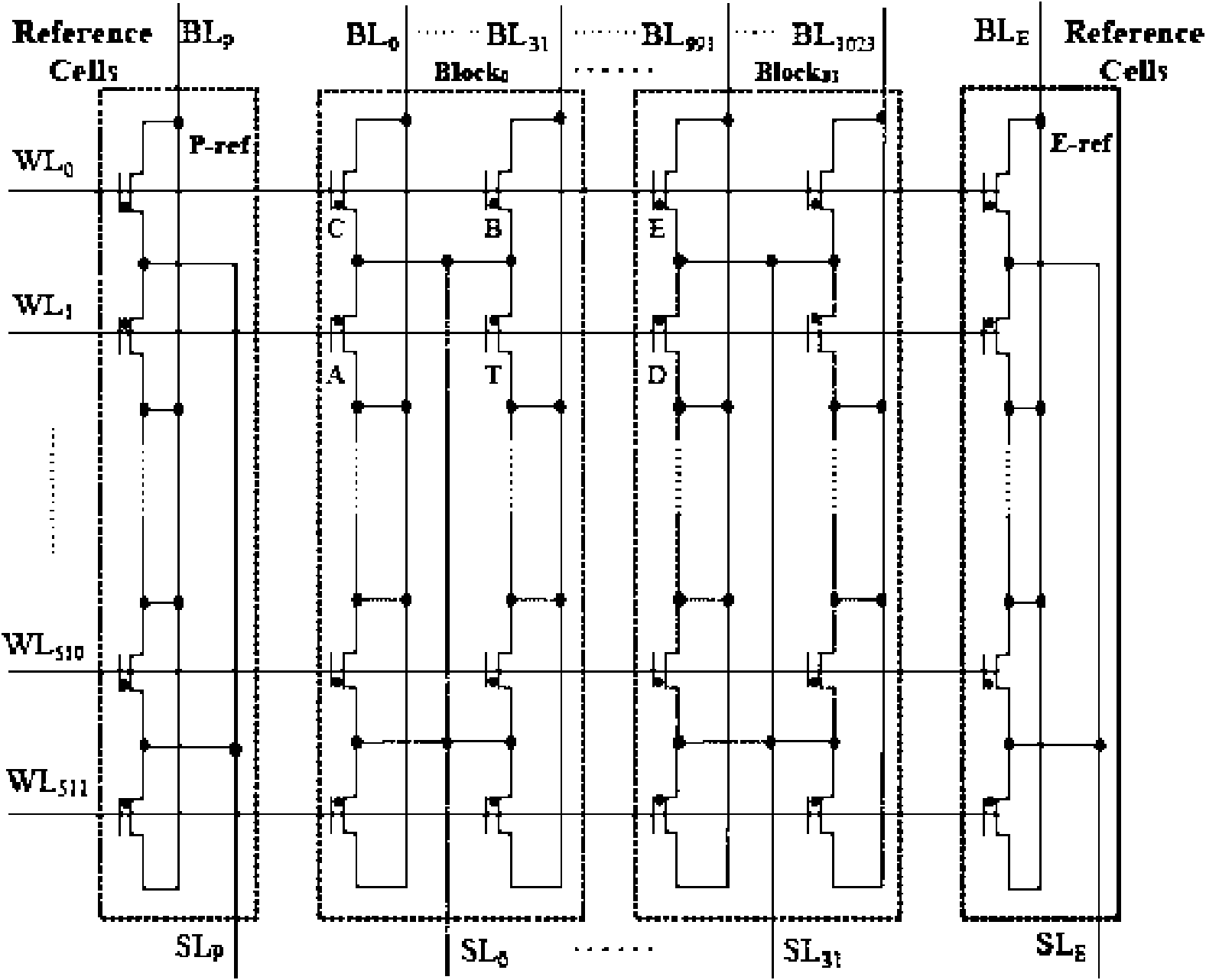

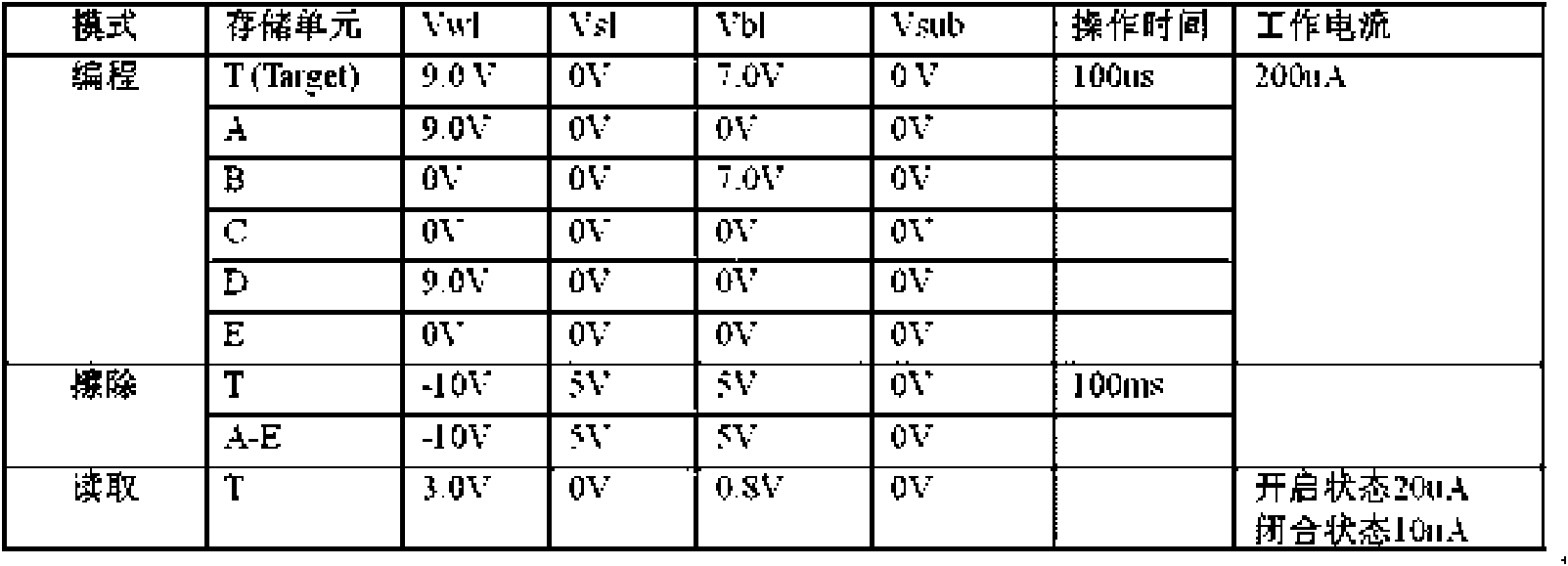

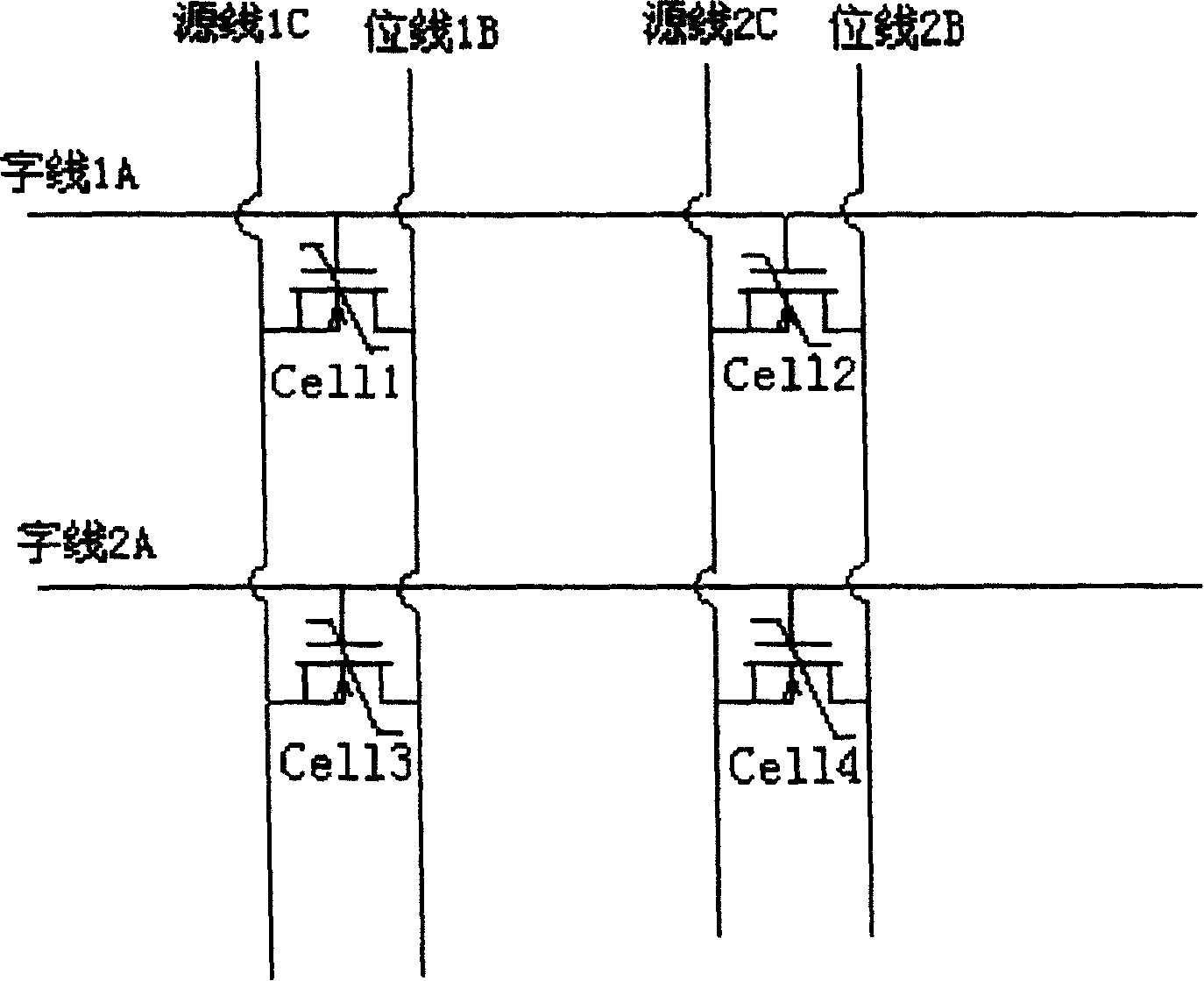

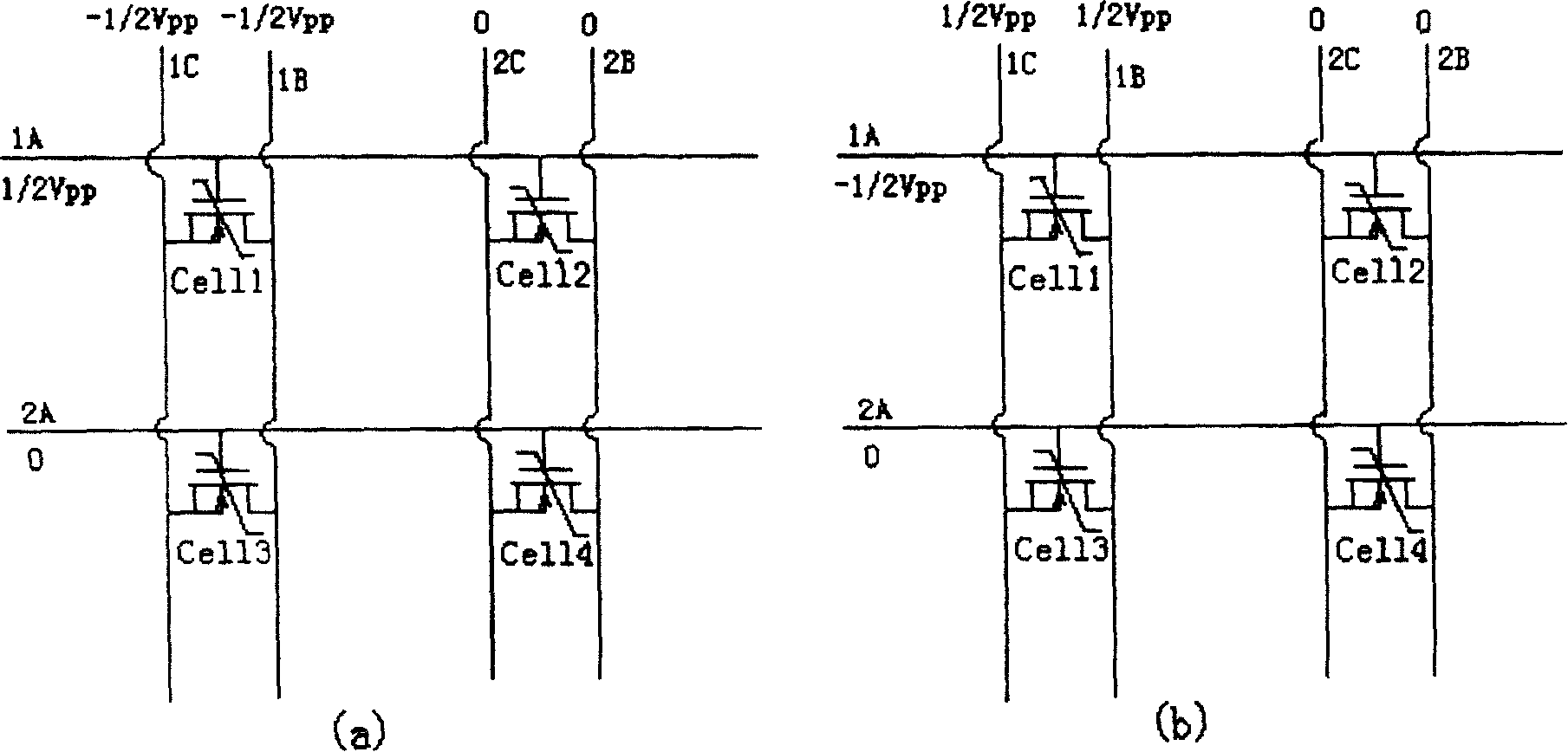

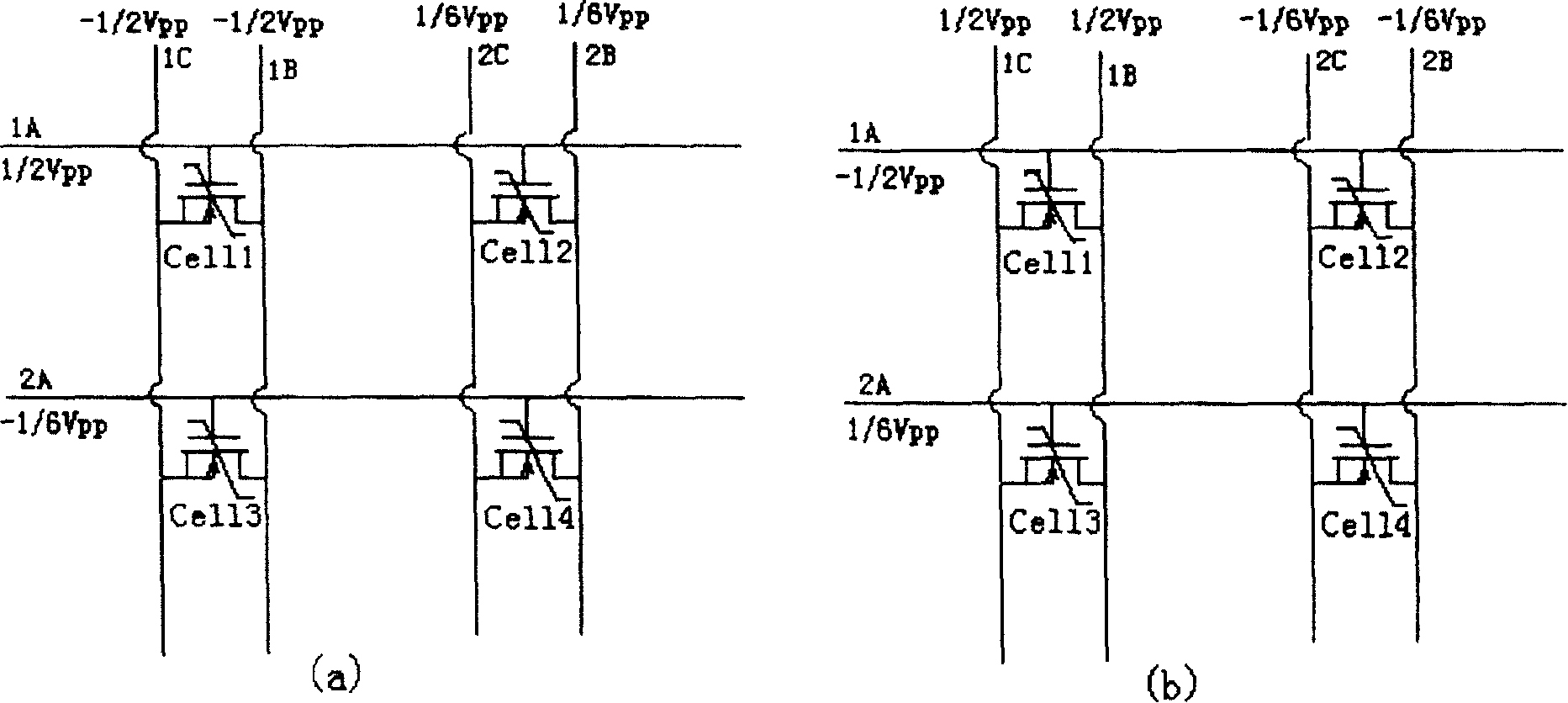

Programing method for ferroelectric dynamic random access single-tube unit array

InactiveCN1848293AThe range of programming voltages increasesReduce restrictionsDigital storageIntegrated circuitRandom access

The present invention provides a programming method of ferro-electric dynamic random memory single-tube unit array, belonging to the field of semiconductor integrated circuit design and manufacture technology. In the course of programming true unit said method can apply the voltage for inhibiting programming to word line, bit line and source line of non-true unit so as to make the range of programming voltage which can be applied to said single-tube unit array be further increased, so that the larger storage window can be obtained.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

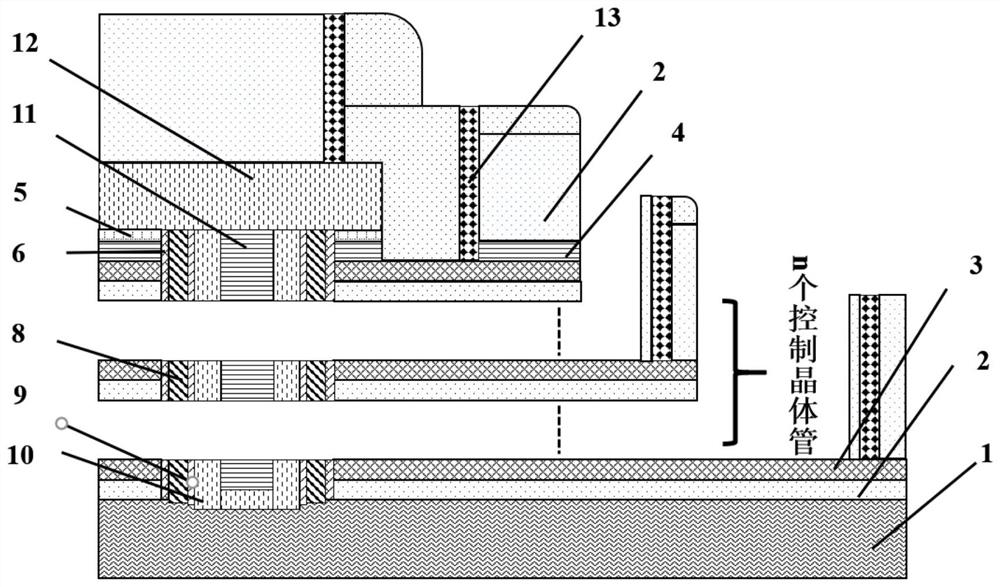

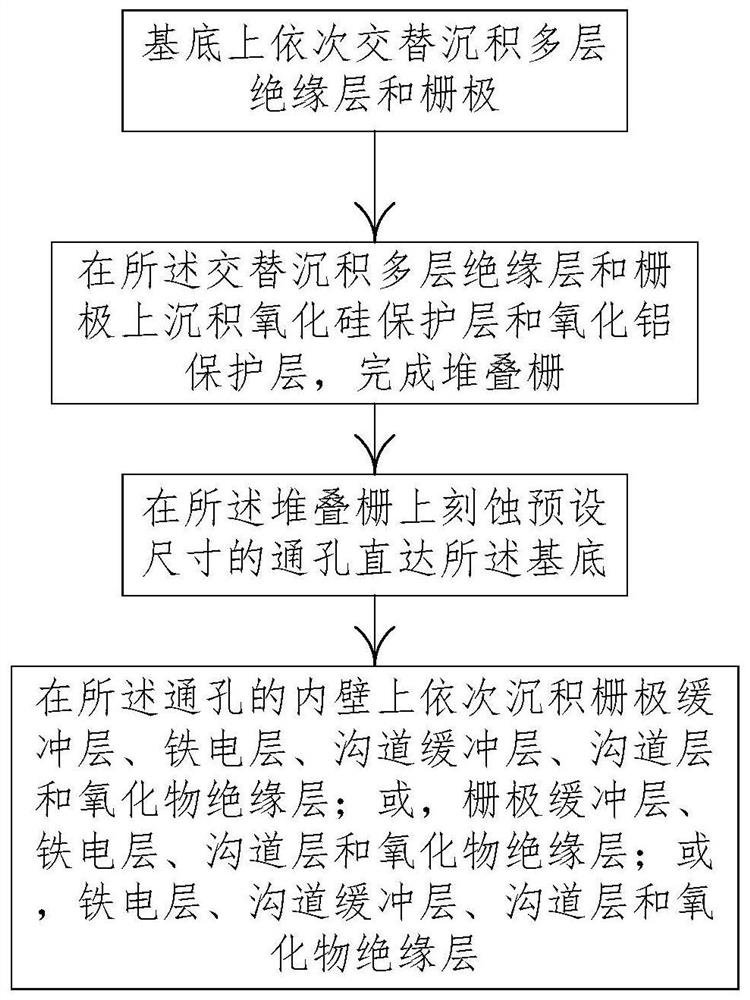

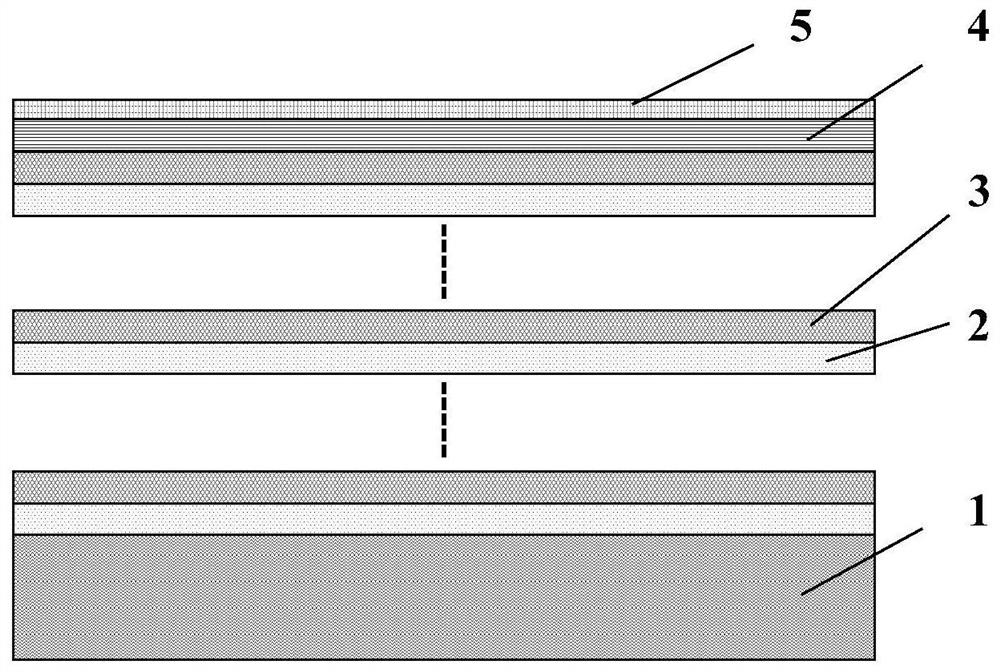

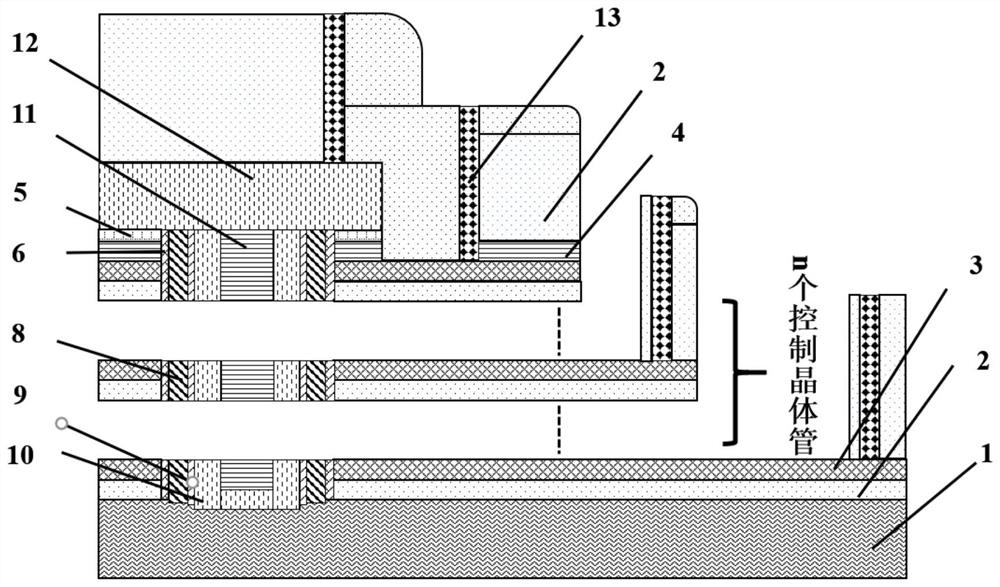

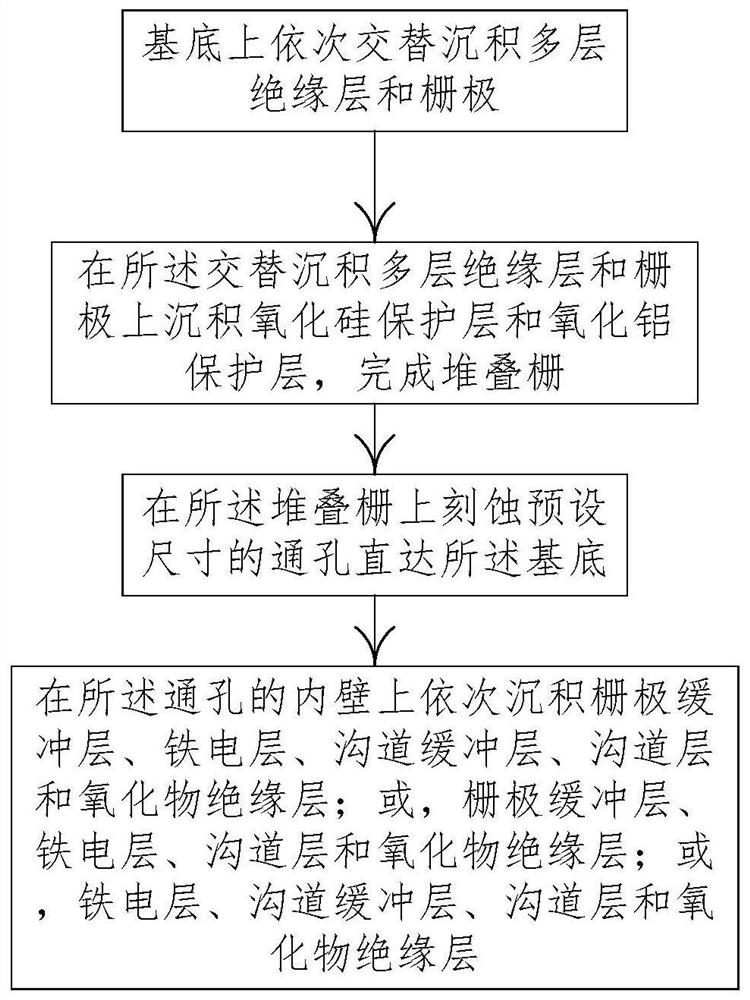

NAND ferroelectric storage unit with three-dimensional structure and preparation method thereof

ActiveCN112164699AIncrease storage windowImprove interface performanceSolid-state devicesSemiconductor devicesFerroelectric thin filmsPhysical chemistry

Provided are a NAND ferroelectric storage unit with a three-dimensional structure and a preparation method thereof. The ferroelectric storage unit comprises an oxide insulating layer, a channel layer,a channel buffer layer, a ferroelectric layer, a gate buffer layer and a gate which are sequentially arranged from inside to outside; a channel buffer layer is arranged between the channel layer andthe ferroelectric layer; and / or a gate buffer layer is arranged between the ferroelectric layer and the gate. According to the storage unit, the buffer layer has the following effects: 1, the ferroelectric film can be induced to crystallize to generate a ferroelectric phase; 2, adverse effects caused by different crystallization characteristics of the channel layer and the ferroelectric layer during unified annealing crystallization can be reduced, and the quality and the uniformity of a deposited film are improved; and 3, the buffer layer can improve the interface performance of the channel layer, reduce the leakage current and improve the anti-fatigue performance of the device. Therefore, the buffer layer can integrally improve the storage performance and uniformity of the storage unit in the three-dimensional structure, increase the storage window of the storage unit, improve the fatigue performance of the storage unit and improve the uniformity of the storage performance of a plurality of transistors.

Owner:XIANGTAN UNIV

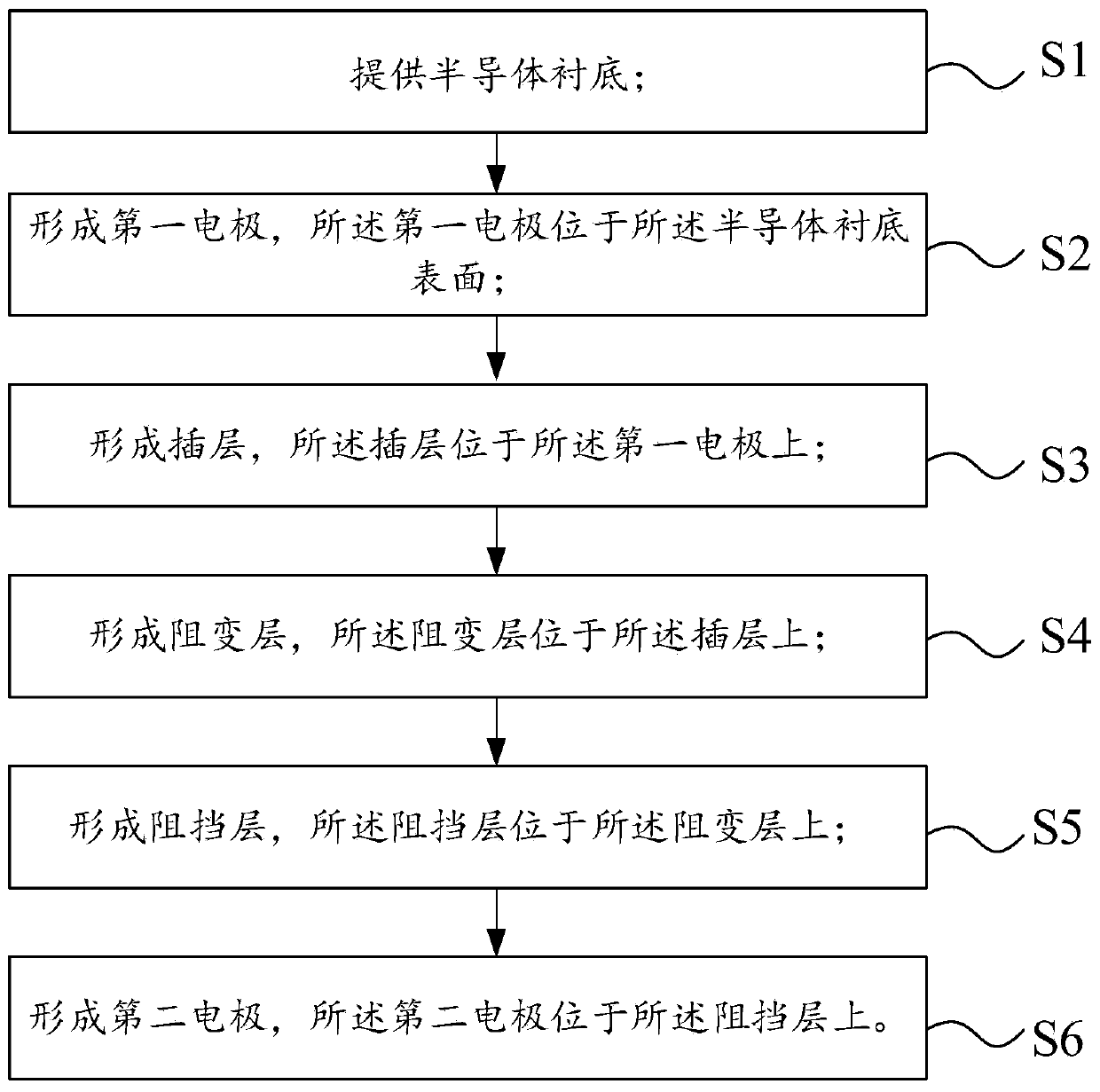

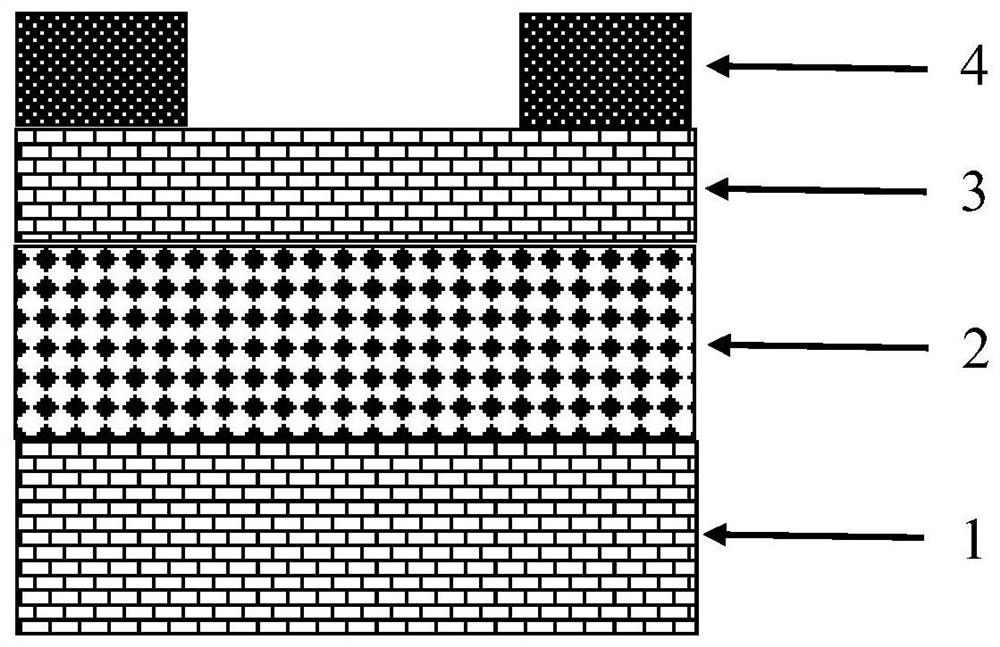

Resistive random access memory and manufacturing method thereof

PendingCN110854267AIncrease storage windowImprove process uniformityElectrical apparatusComputational physicsSemiconductor

The invention provides a resistive random access memory and a manufacturing method thereof. According to the resistive random access memory and the manufacturing method thereof provided by the invention, a first electrode is formed on the surface of a semiconductor substrate, an intercalation layer is formed on the first electrode, a resistive switching layer is formed on the intercalation layer,a barrier layer is formed on the resistive switching layer, and a second electrode is formed on the barrier layer. The intercalation layer can be matched with the resistive switching layer to achievebetter device performance, and the initial resistance of the resistive random access memory can be modulated through the intercalation layer, so that the storage window of the resistive random accessmemory can be enlarged, and the process uniformity and the performance of the resistive random access memory can be improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Device with storage and gating functions and preparation method thereof

ActiveCN108598257AIncrease storage windowReduce the degree of offsetElectrical apparatusHigh resistanceElectrical resistance and conductance

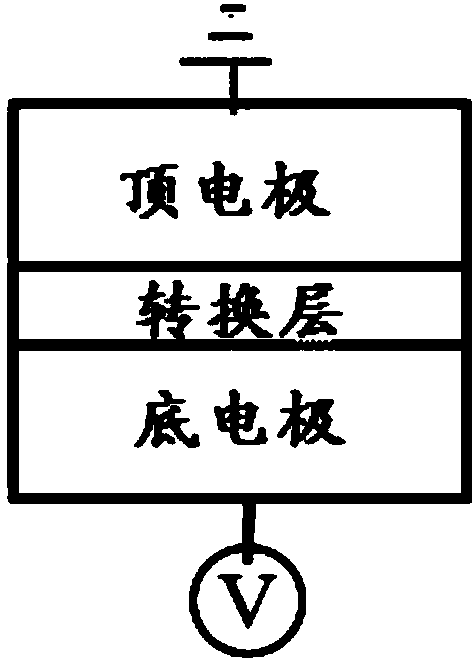

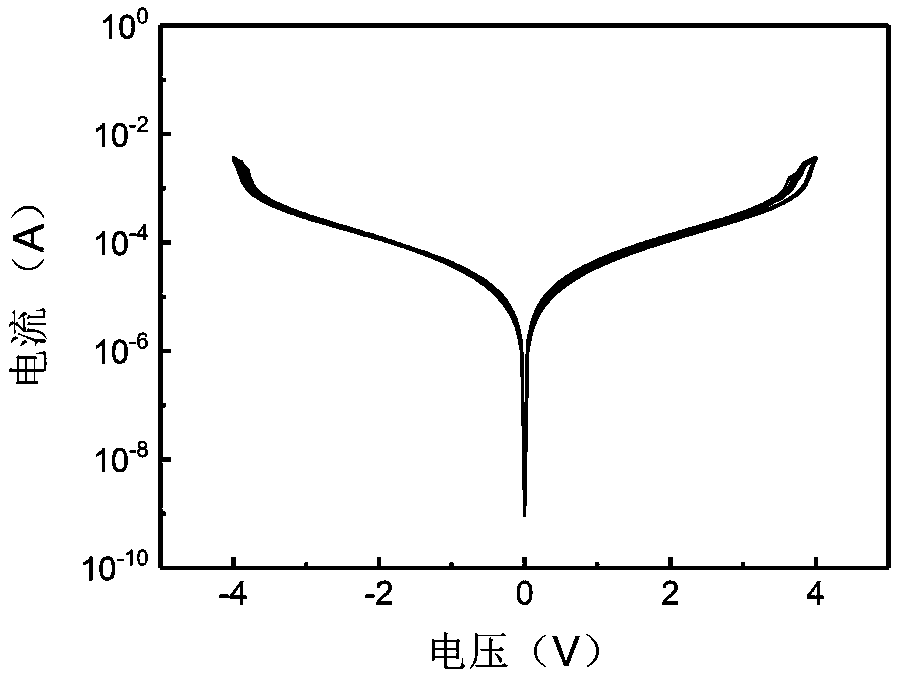

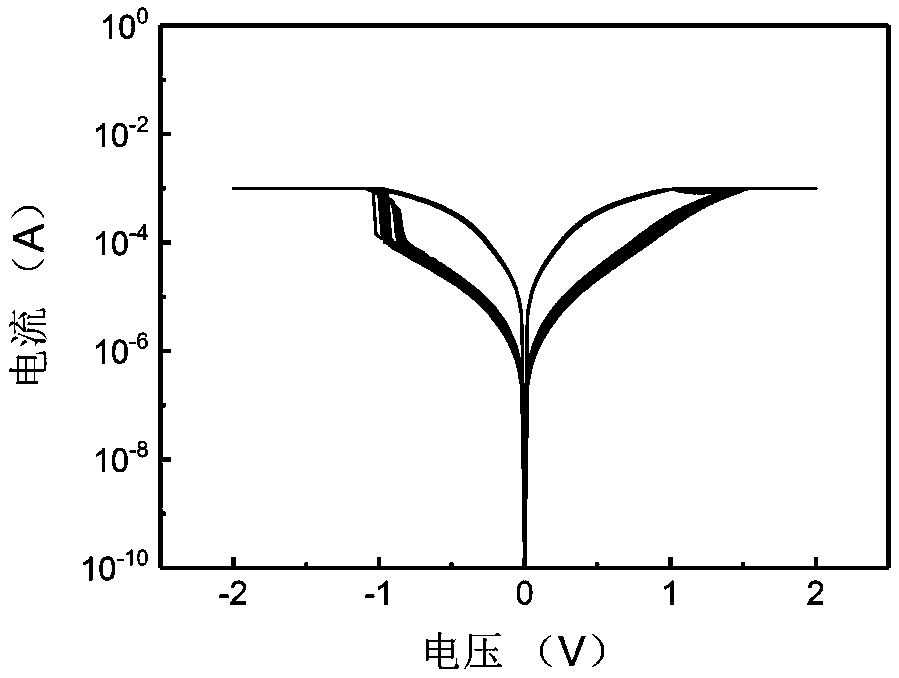

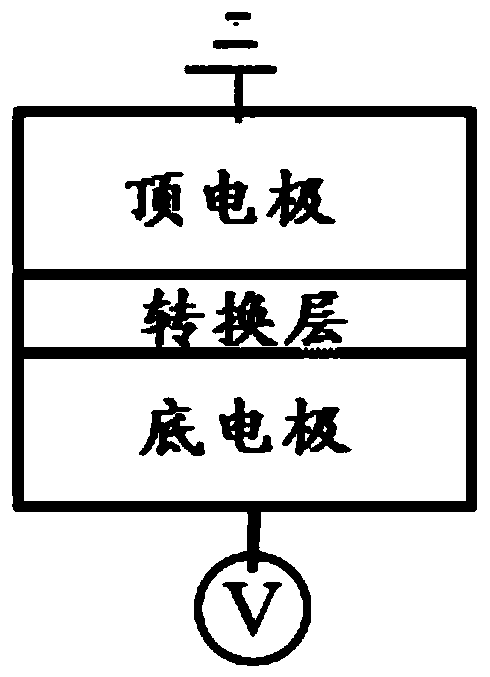

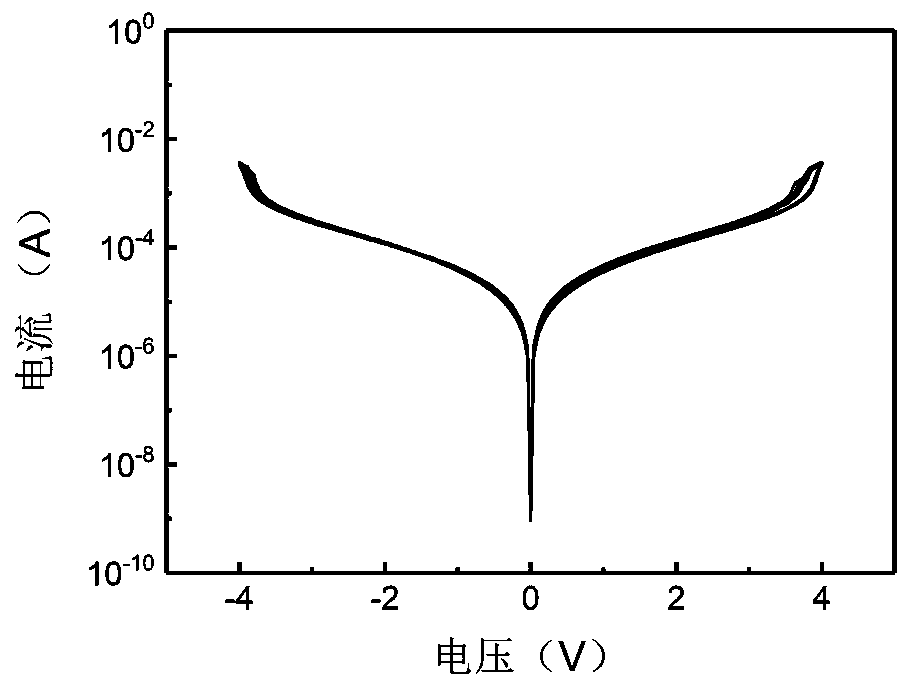

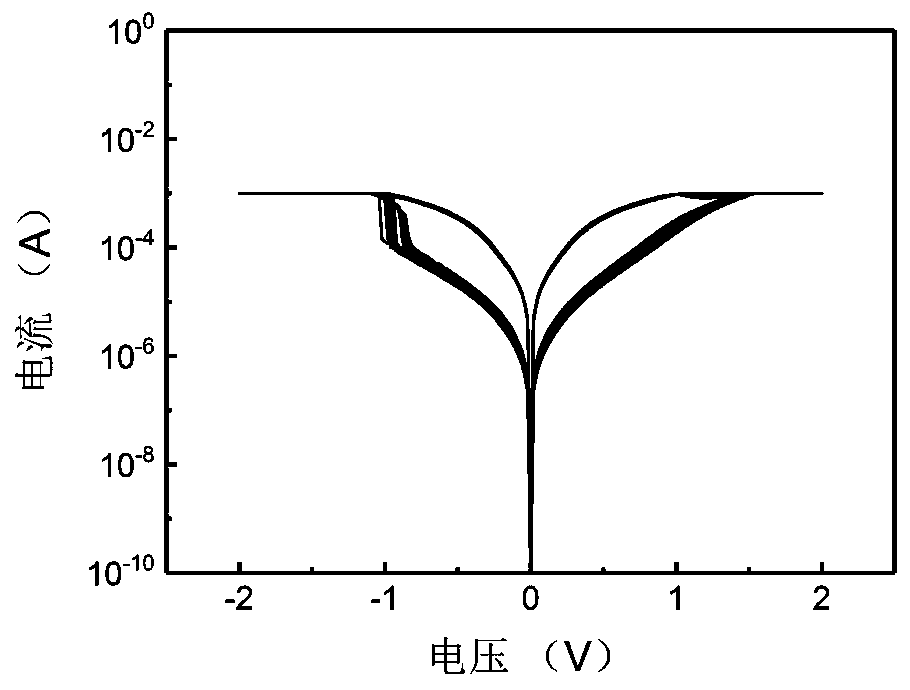

The invention provides a device with storage and gating functions which comprises a bottom electrode, a conversion layer and a top electrode sequentially from downside to upside; the bottom electrodeis TiN or conductive glass; the conversion layer is made of niobium oxide; and the top electrode is tungsten. The device with the storage and gating functions is composed of the niobium oxide which serves as the conversion layer, the TiN or conductive glass which serves as the bottom electrode, and the metal tungsten which serves as the top electrode. The experimental results show that the deviceprovided by the invention has a gating function in the presence of big current limitation and has a resistance change performance (storage performance) in the presence of small current limitation; thedevice also has excellent stability as the deviation degree of the obtained curve is very small after the device is subjected to circular test for 100 turns in the gating and resistance change performance test; and the device also has a relatively big storage window as the resistance value of a high-resistance resistor is 10 greater than that of a low-resistance resistor in the resistance changeperformance test.

Owner:HUBEI UNIV

Memory method for nanocrystalline floating gate structure-based multi-value nonvolatile memory

ActiveCN102117656AImprove programming efficiencyIncrease storage windowRead-only memoriesMulti valuedConventional memory

The invention relates to a memory method for a nanocrystalline floating gate structure-based multi-value nonvolatile memory, and belongs to the technical field of memories. In the memory method, hot electron injection is used as a programming mode, Fowler-Nordheim (FN) tunneling is used as an erasing mode, and four memory states of 00, 01, 10 and 11 are differentiated according to amplitude of read current, so that multi-value memory can be realized under the condition of the same area to double memory capacity. In the method, the new programming mode is adopted to simultaneously program at asource end and a drain end, and the multi-value memory is formed, so that the programming efficiency is greatly improved, a memory window is also increased, memory of more points is realized, and thememory capacity which is twice the conventional memory capacity is realized on a memory unit of the same size; in addition, a manufacturing process is not changed while the advantage is realized, andthe cost is greatly reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

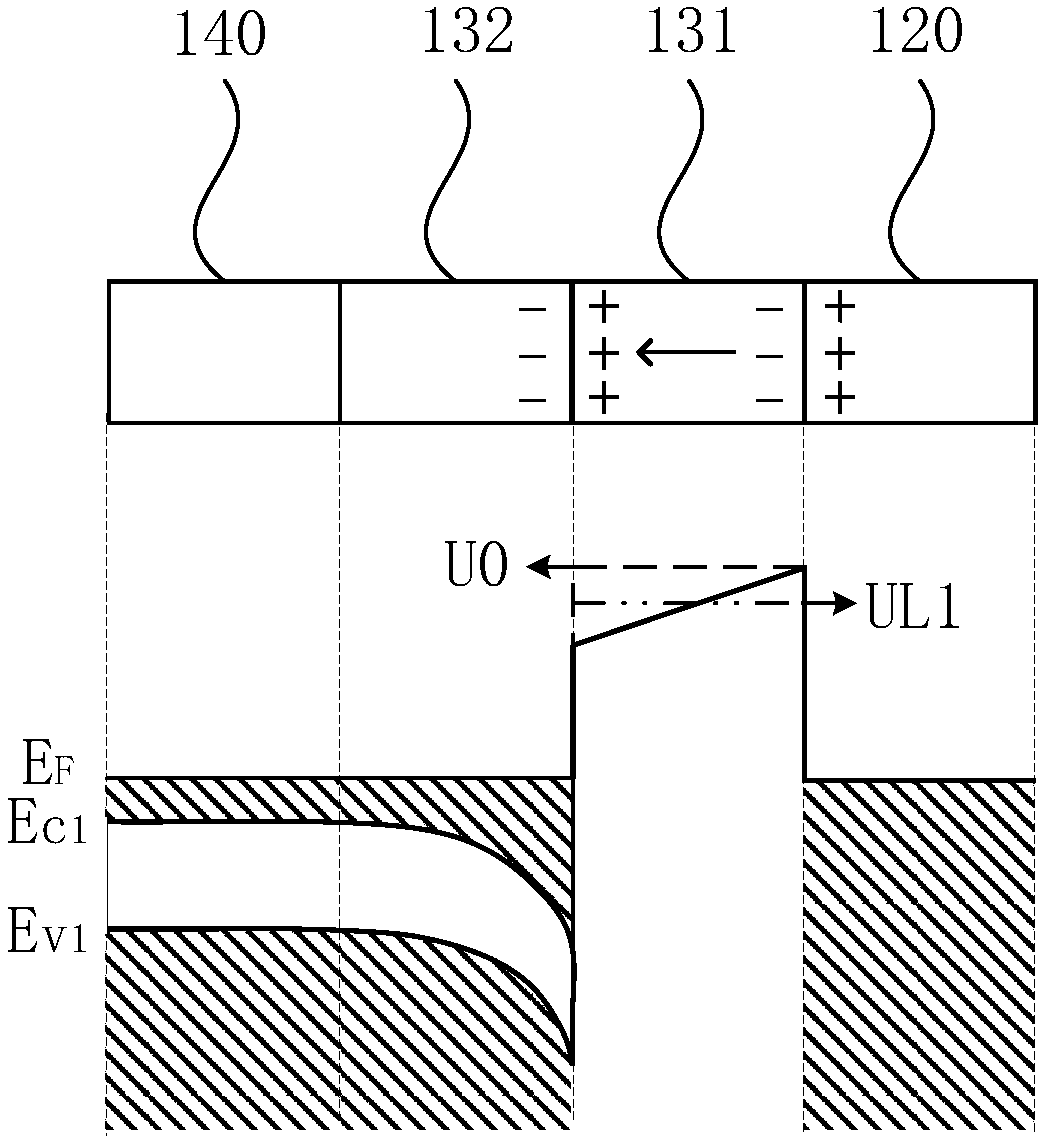

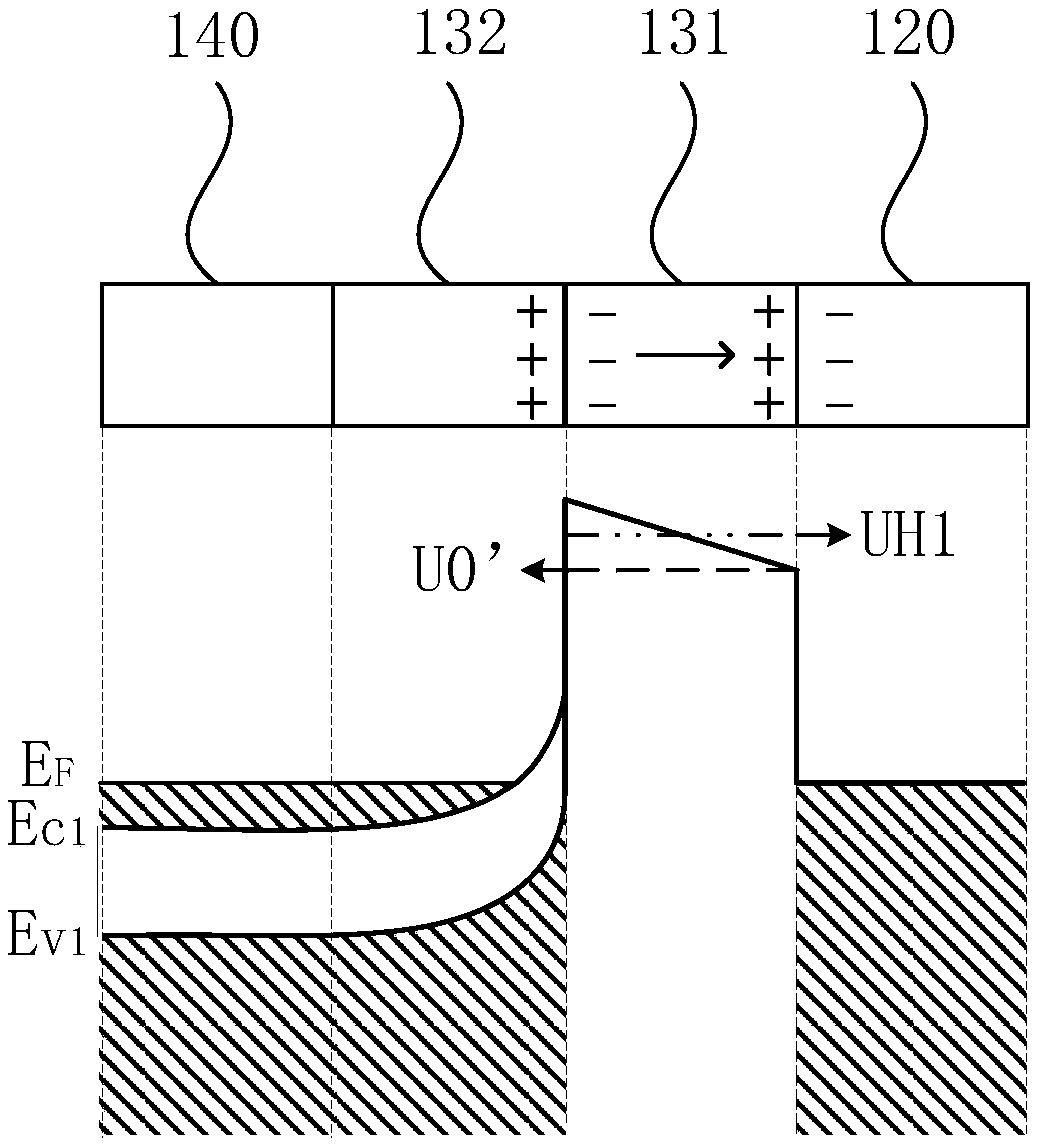

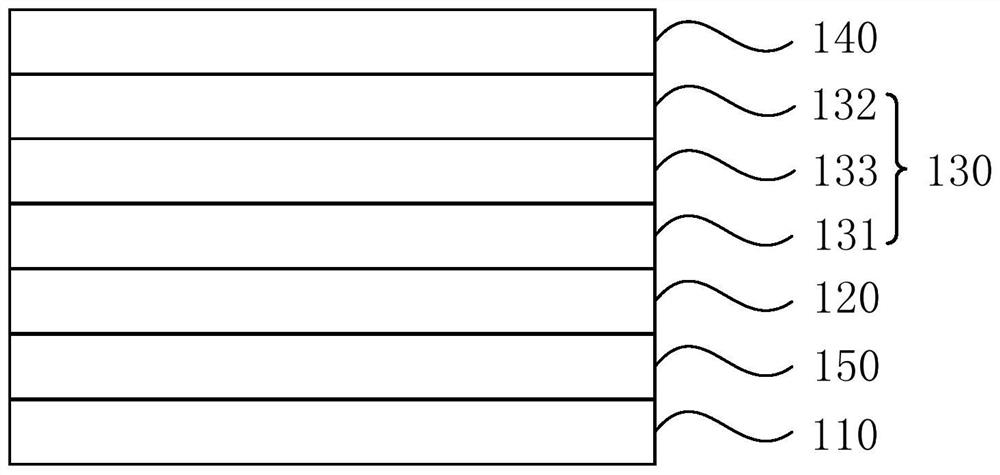

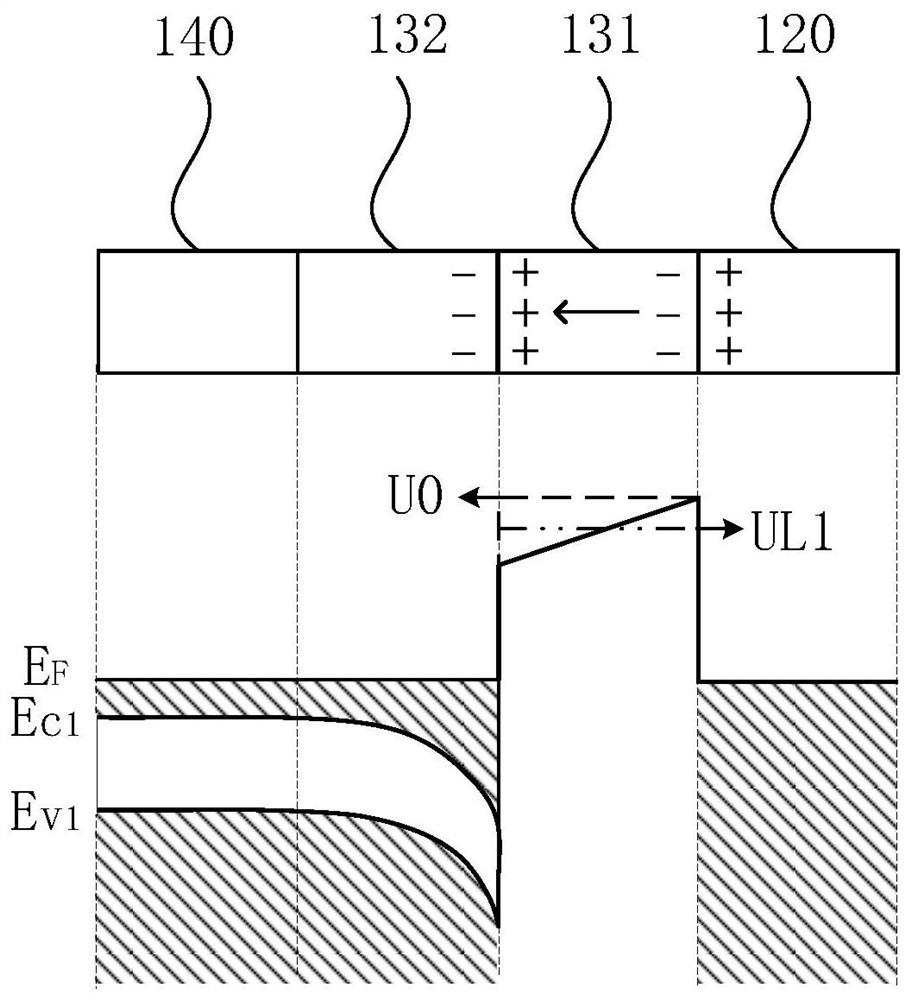

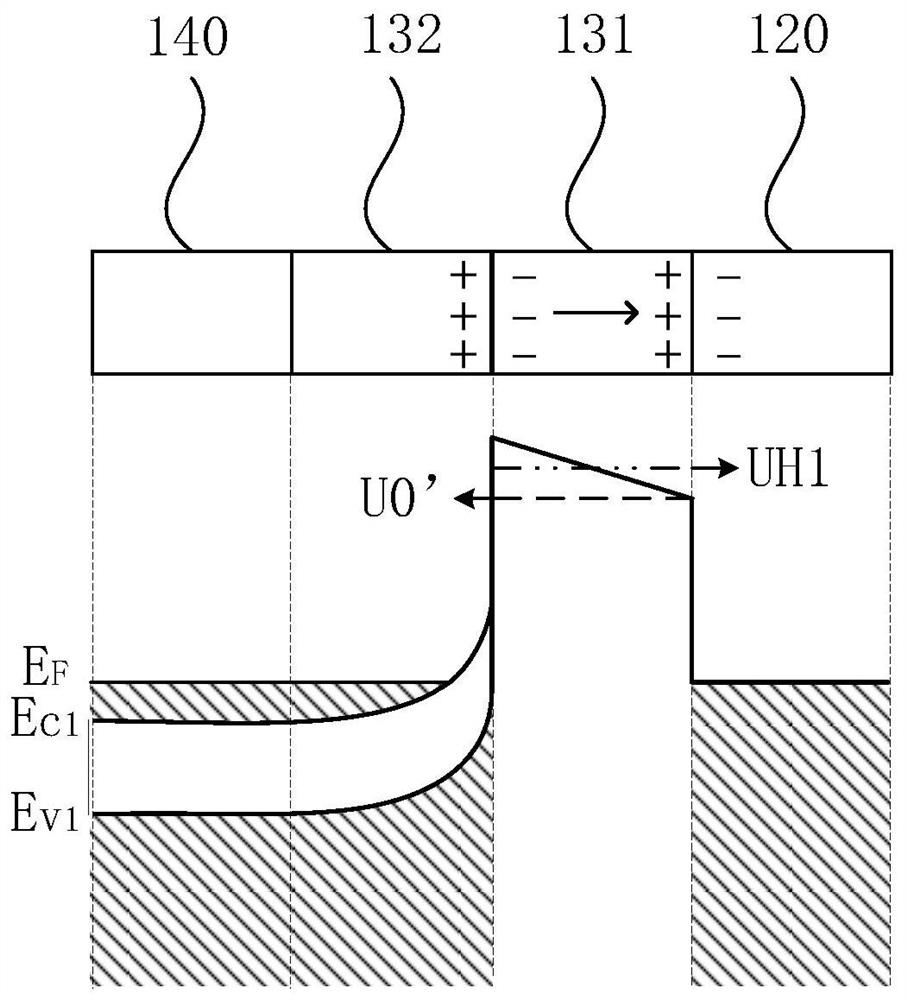

Ferromagnetic random access memory, writing method thereof, reading method thereof and preparation method thereof

ActiveCN107946461AIncrease the on-off ratioIncrease storage windowElectrical apparatusElectrical resistance and conductanceStatic random-access memory

The invention discloses a ferromagnetic random access memory, a writing method thereof, a reading method thereof and a preparation method thereof. The iron resistance variable memory includes a substrate layer, a bottom electrode, a switch layer and a top electrode which are successively stacked. The switch layer includes a ferroelectric layer and at least one semiconductor layer disposed adjacentto the ferroelectric layer. The ferroelectric layer is polarized under the effect of an electric field and is configured to change the potential barrier of the switch layer. By adding at least one semiconductor layer to the switch layer and disposing the semiconductor layer adjacent to the ferroelectric layer, a variable barrier layer is provided so as to increase the resistance ratio of the highand low resistance states of the switch layer under the effect of the electric field, that is, the storage window of the ferromagnetic random access memory is increased. Thus, the high-density storage of the ferromagnetic random access memory is realized, and the small storage window of the ferromagnetic random access memory is solved.

Owner:SOUTH UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA

A charge-trapping memory based on a single-layer barium strontium titanate thin film and its preparation method

ActiveCN106783863BStable hold characteristicGood retention propertiesSolid-state devicesSemiconductor devicesStrontium titanateSputtering

The invention discloses a charge-trapping memory based on a single-layer barium strontium titanate (BST) thin film, and its structure is a P-type Si substrate, a SiO 2 tunneling layer, barium strontium titanate capture barrier layer and Pd electrode layer. At the same time, the preparation method of the memory is also disclosed. The P-type Si substrate is washed and dried, and a barium strontium titanate capture barrier layer is formed on the Si substrate by magnetron sputtering. SiO 2 tunneling layer, and then a Pd electrode layer was formed on the barium strontium titanate capture barrier layer by magnetron sputtering. The present invention prepares p-Si substrate / SiO through specific materials and methods 2 A charge-trapping memory with a composite structure of tunneling layer / barium strontium titanate trapping layer / Pd electrode layer. Tests show that, compared with the existing memory of the same type, the memory provided by the present invention has a larger storage window and better data retention, and is a memory device that is fatigue-resistant, has a fast writing / erasing rate, and has wider application prospects. of memory.

Owner:HEBEI UNIVERSITY

A storage and gating dual-function device and its preparation method

ActiveCN108598257BIncrease storage windowReduce the degree of offsetElectrical apparatusElectrical resistance and conductanceCurrent limiting

The invention provides a dual-function device for storing and gating, which includes a bottom electrode, a conversion layer and a top electrode from bottom to top, the bottom electrode is TiN or conductive glass, the conversion layer is niobium oxide, and the The top electrode is tungsten. The invention uses niobium oxide as the conversion layer, uses TiN or conductive glass as the bottom electrode, and metal tungsten as the top electrode to form a device with dual functions of storage and gating. Experimental results show that the device provided by the present invention has gating performance when there is a large current limit, and has resistive switching performance (i.e. storage performance) when small current limiting; Simultaneously in the gating and resistive switching performance test, cycle test 100 circles, The deviation degree of the obtained curve is very small, indicating that it also has excellent stability; in the resistance switching performance test, the resistance value of the high-resistance state is greater than 10 than the resistance value of the upper low-resistance state, indicating that the device also has a large Storage window.

Owner:HUBEI UNIV

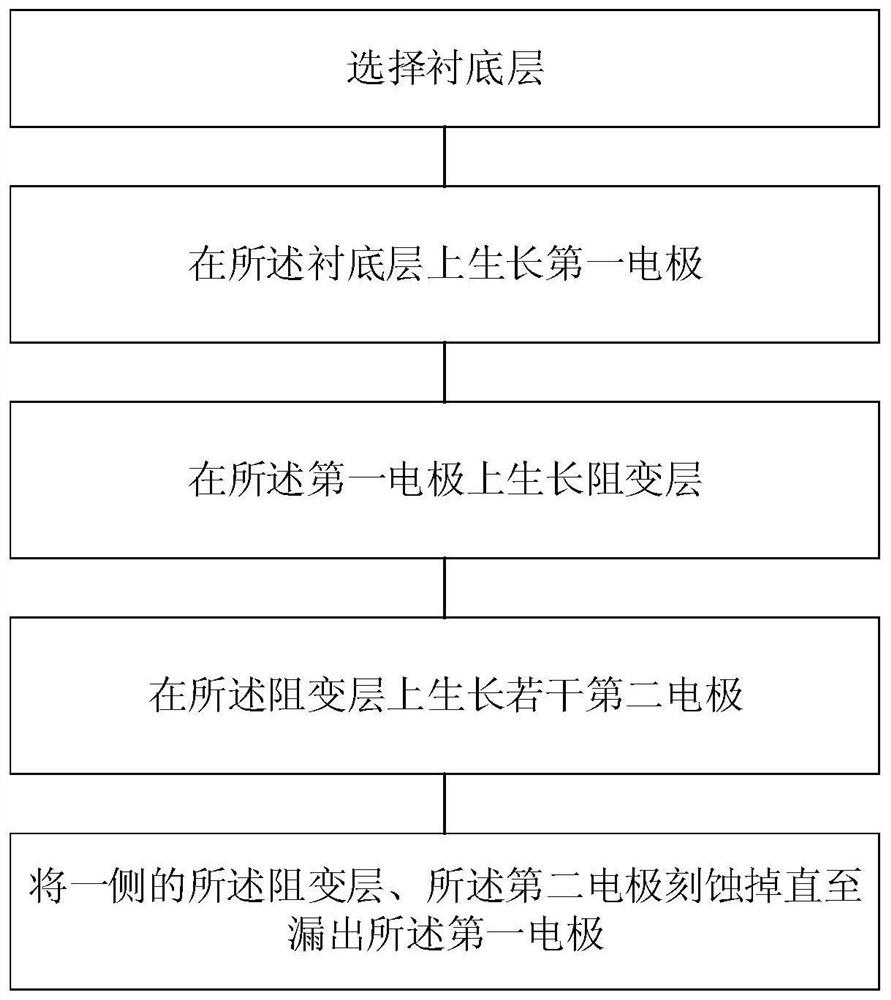

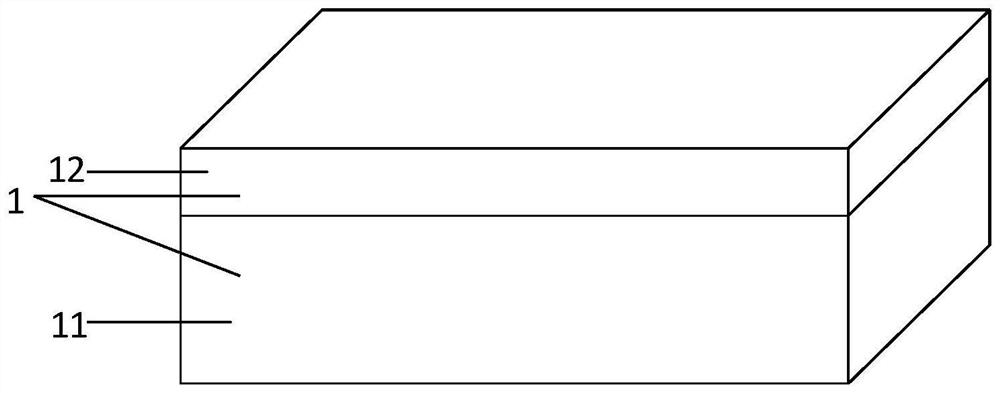

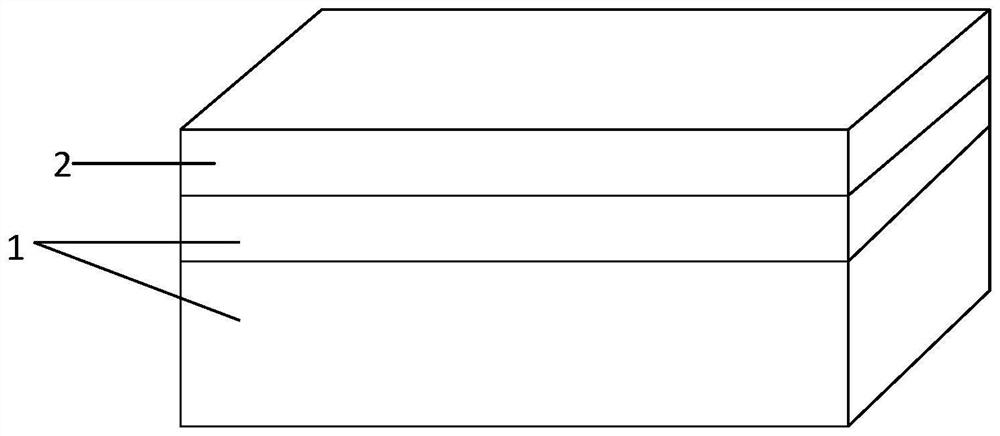

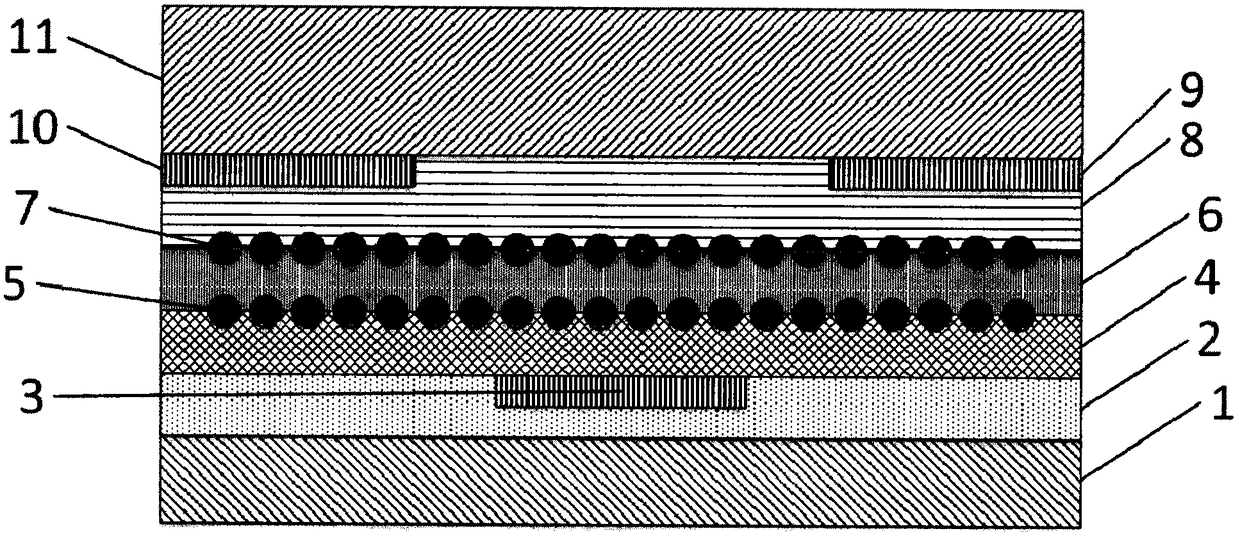

A kind of resistive memory and preparation method thereof

ActiveCN110379919BIncrease storage windowHas forming-free featuresElectrical apparatusDopantPhysical chemistry

The invention discloses a resistive variable memory and a preparation method thereof. The preparation method of the resistive variable memory comprises: selecting a substrate layer; growing a first electrode on the substrate layer; growing a resistive variable layer on the first electrode ; growing several second electrodes on the resistive variable layer; etching away the resistive variable layer and the second electrodes on one side until the first electrodes leak out, so as to complete the preparation of the resistive variable memory. In the preparation of the resistive variable memory, the present invention selects an appropriate dopant for the resistive variable layer, so that the storage window of the resistive variable memory is increased, and the resistive variable memory also has a forming-free characteristic.

Owner:XIDIAN UNIV

A double-layer floating gate flexible organic memory device and its preparation method

InactiveCN105576124BLarge storage capacityImprove stabilitySolid-state devicesSemiconductor/solid-state device manufacturingFlexible circuitsFemto second laser

Owner:CHINA JILIANG UNIV

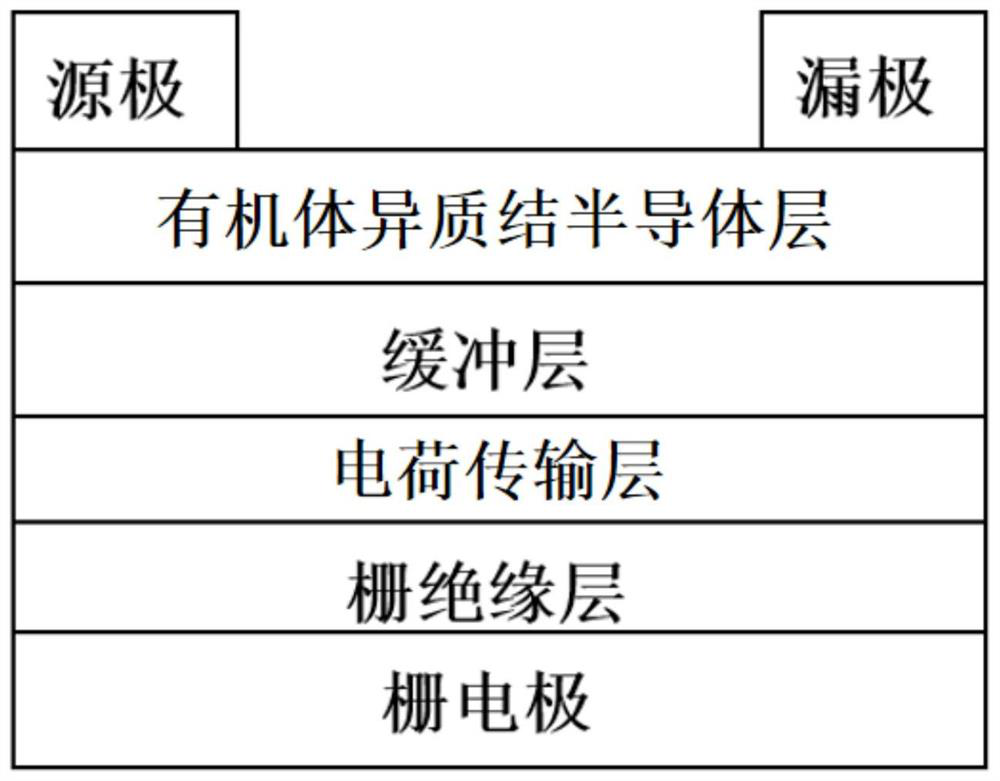

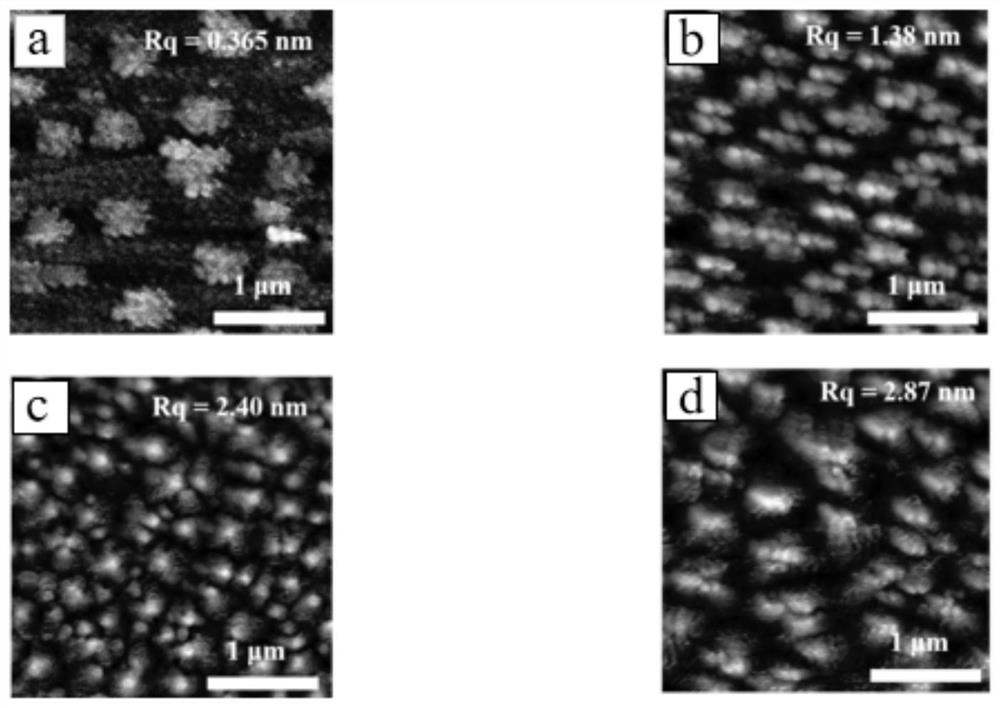

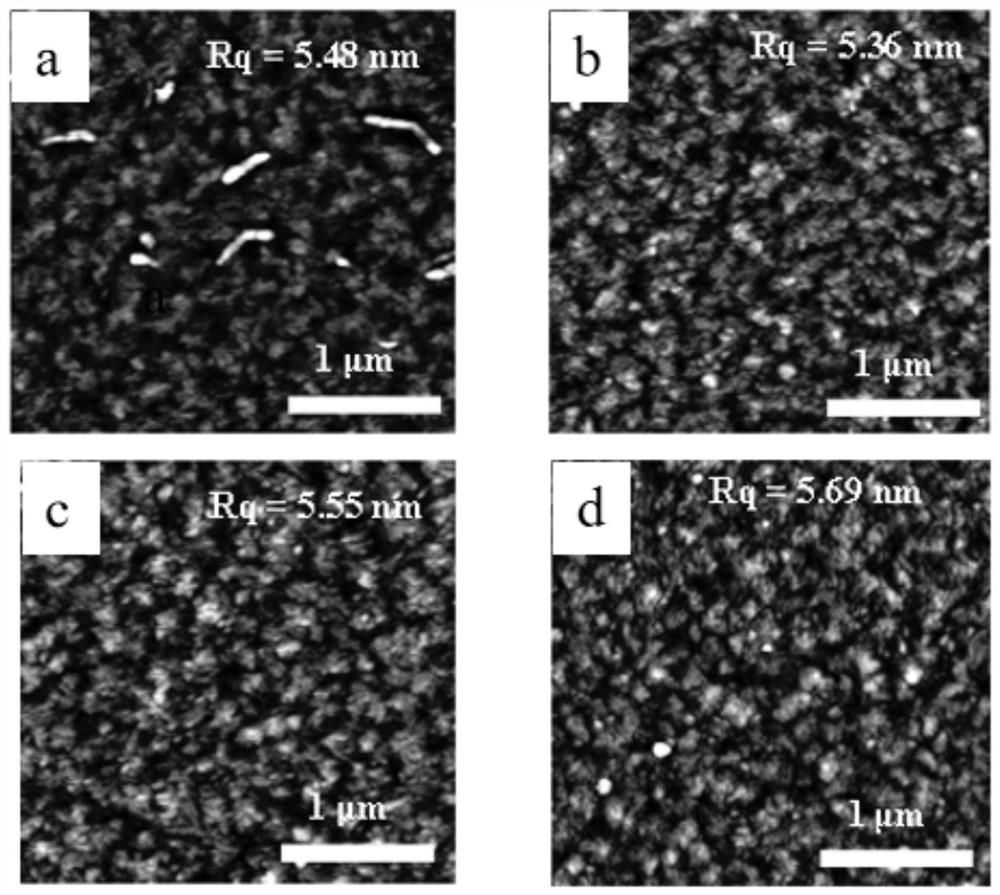

Bulk heterojunction organic field effect transistor memory and preparation method thereof

PendingCN113782565ALow priceEasy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionOrganic field-effect transistor

The invention discloses a bulk heterojunction organic field effect transistor memory. The memory comprises a gate electrode, a gate insulating layer, a charge transfer layer, a buffer layer and an organic heterojunction semiconductor layer sequentially distributed from bottom to top; a source electrode and a drain electrode are deposited on the organic heterojunction semiconductor layer; the organic heterojunction semiconductor layer comprises an n-type semiconductor and a p-type semiconductor, the n-type semiconductor and the p-type semiconductor are both organic materials; and the organic heterojunction semiconductor layer is prepared by cooperatively evaporating the n-type semiconductor and the p-type semiconductor. Compared with a multi-layer structure organic heterojunction device, the bulk heterojunction organic field effect transistor is simpler in preparation process; a bipolar storage characteristic can be achieved through electric programming, stable operation in the air can be achieved, limitation of the use environment is avoided, and the preparation cost is effectively reduced. The invention also discloses a method for preparing the bulk heterojunction organic field effect transistor.

Owner:LUDONG UNIVERSITY

A resistive memory based on organic/inorganic hybrid perovskite material and its preparation method

The invention discloses a resistive random access memory based on an organic / inorganic hybrid perovskite material and a fabrication method of the resistive random access memory. The resistive random access memory comprises a bottom electrode, a top electrode and a resistance changing functional layer material, wherein the resistance changing functional layer material is arranged between the bottom electrode and the top electrode and comprises one layer or multiple layers of organic / inorganic hybrid perovskite thin film materials. The fabrication method comprises the following steps of (1) cleaning a substrate; (2) depositing the bottom electrode on the substrate by employing a physical vapor deposition technique; (3) forming the organic / inorganic hybrid perovskite thin film material on the bottom electrode as a resistance changing functional layer by techniques such as spin coating, dip coating and vacuum evaporation; and (4) depositing the top electrode on the resistance changing functional layer by employing the physical vapor deposition technique. According to the resistive random access memory, the structure is simple, and low-temperature and low-cost fabrication can be carried out; and the fabricated device has the technical advantages of large memory window, low conversion voltage, high conversion speed, multi-value storage capability, favorable thermal stability and device durability and the like.

Owner:GRIMAT ENG INST CO LTD

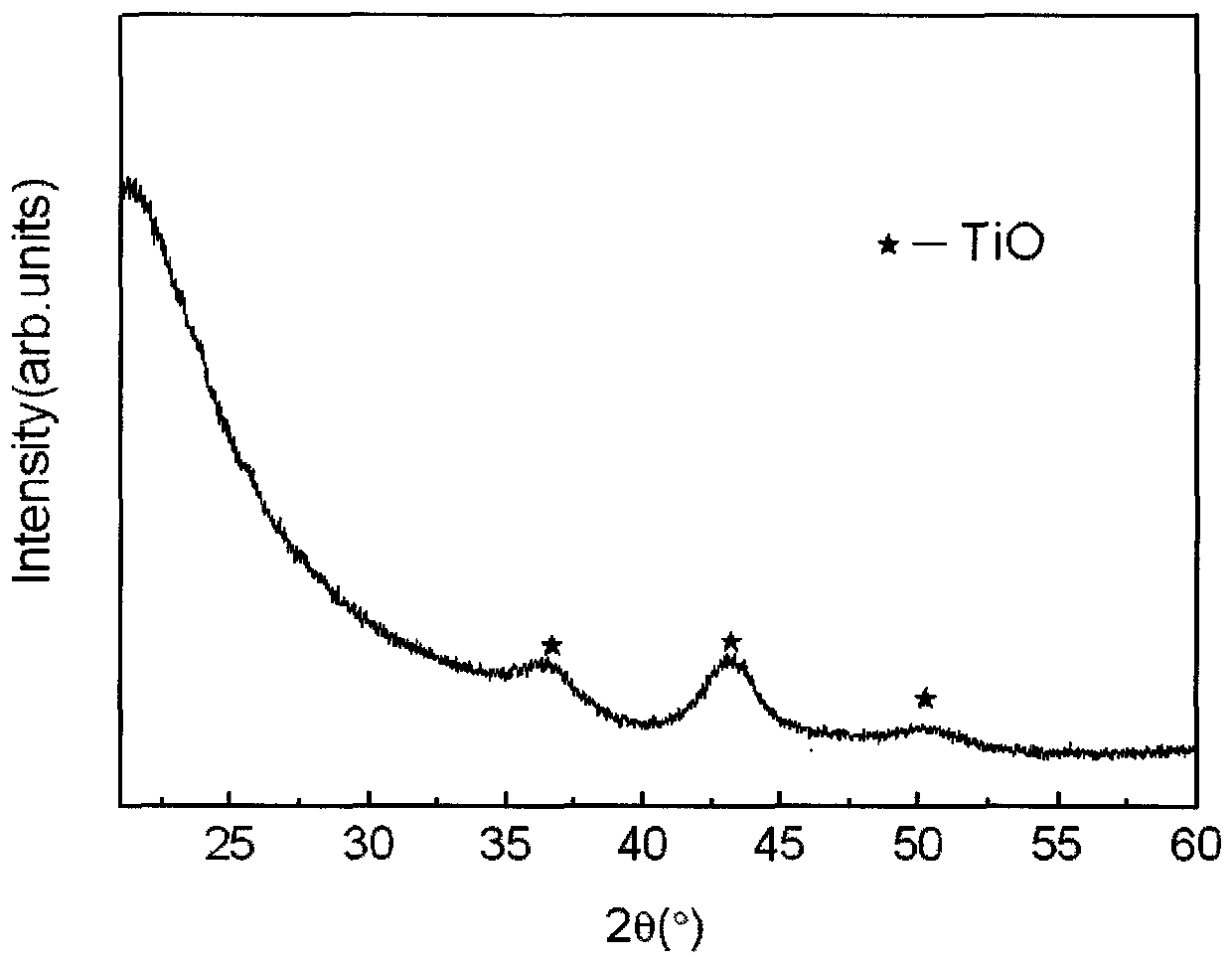

A multi-resistance state double-layer film structure resistive variable memory and its preparation method

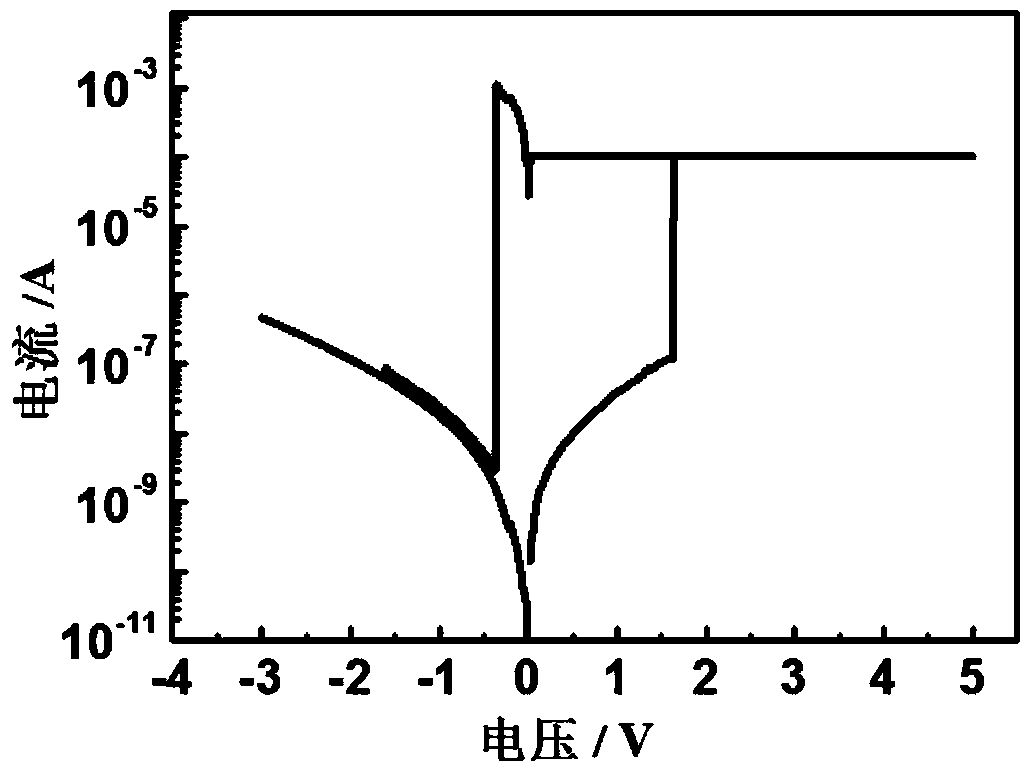

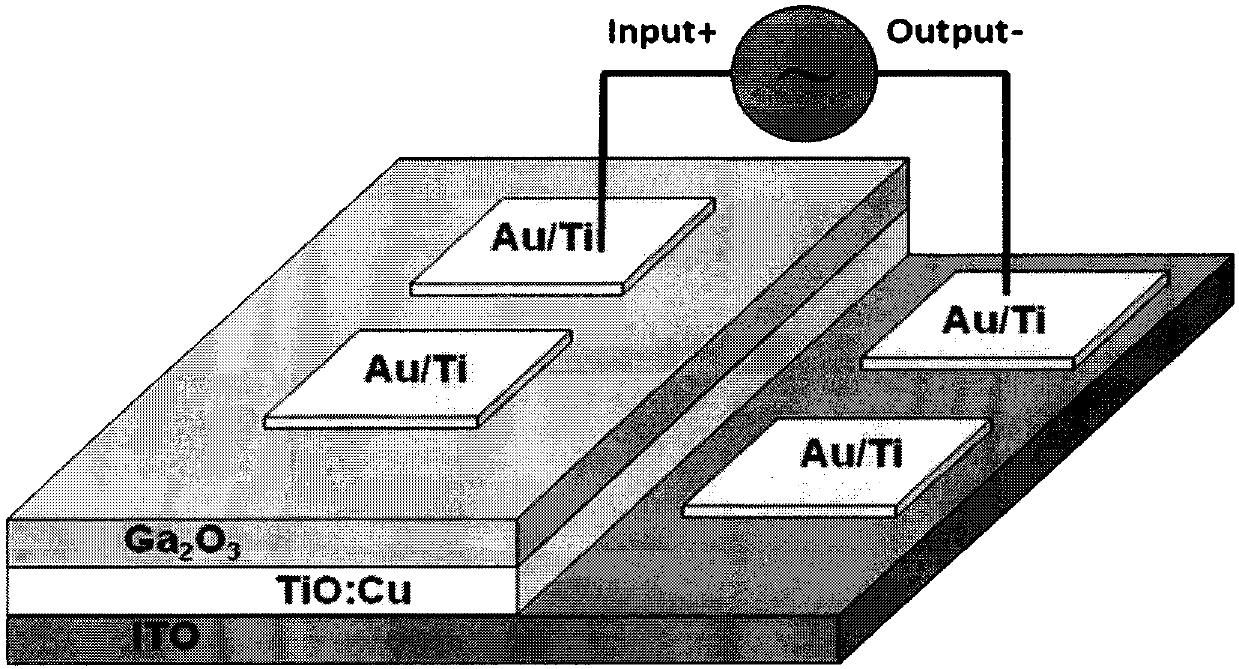

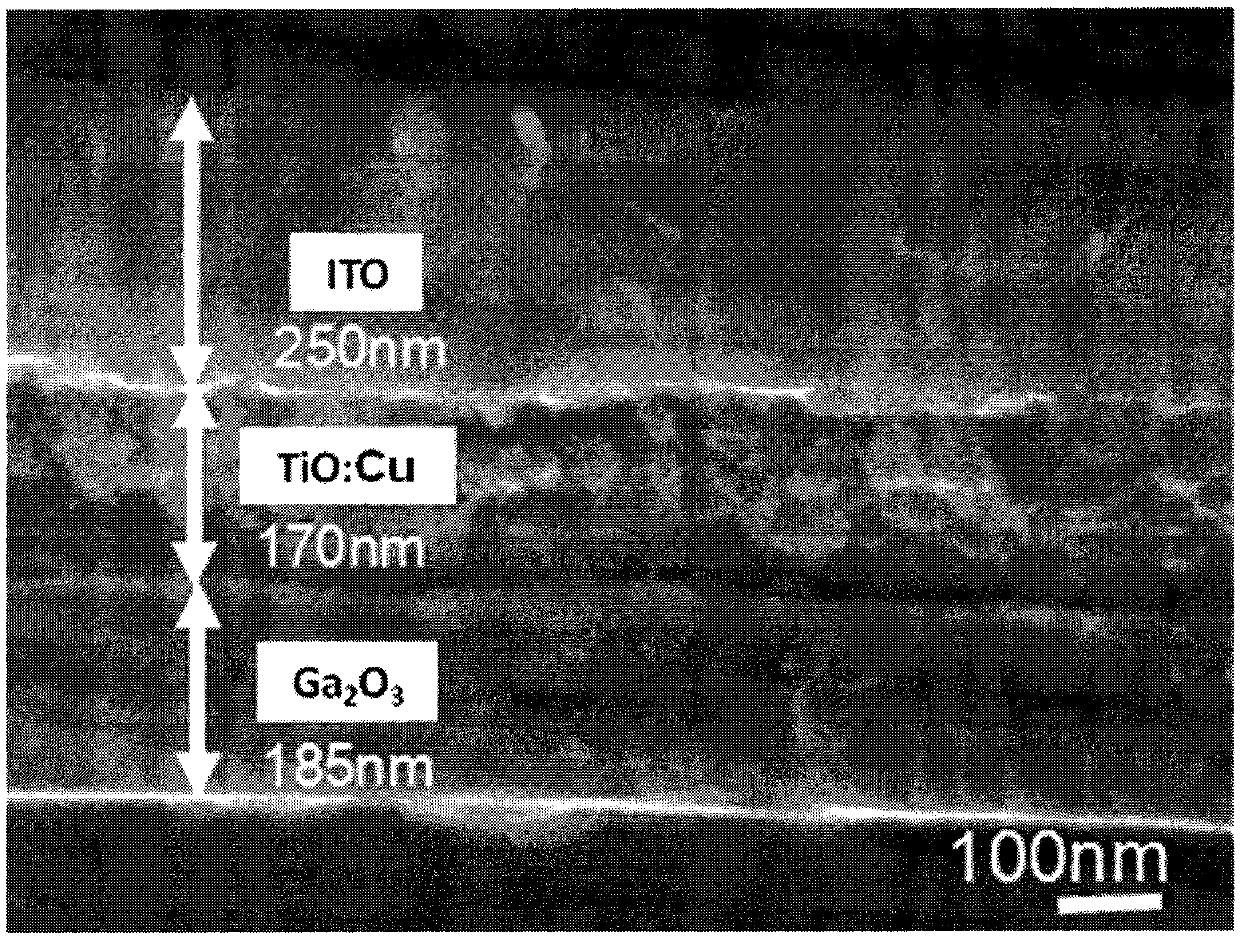

ActiveCN105185904BStable and uniform dense thicknessStable characteristicsSemiconductor/solid-state device manufacturingState variableTitanium

The invention discloses a multi-resistance state double-layer thin-film structure resistive variable memory and a preparation method thereof. The resistive variable memory has stable retention characteristics and multi-value storage performance. Specifically, it uses metal Ti / Au as the upper electrode, ITO as the substrate and the lower electrode, and uses radio frequency magnetron deposition technology to successively plate on the ITO substrate. TiO: Cu and Ga2O3 films to form a resistive layer, and then sputtering titanium (Ti) and gold (Au) films on the ITO substrate and the film that has been plated with gallium oxide to form ITO / TiO: Cu / Ga2O3 / Ti / Au structure memory device, and realize the multi-valued storage function. The advantage of the present invention is that single and bipolar resistive switching is generated through the movement of defects at the heterojunction interface, and the resistive switching memory device prepared has stable retention characteristics, cycle characteristics and multi-resistance state resistive switching storage performance, which improves the memory performance. storage capacity and service life.

Owner:江苏惠沣环保科技有限公司

A kind of resistive variable memory based on SRO and preparation method thereof

ActiveCN109273597BGood resistive propertiesImprove stabilityElectrical apparatusHigh densityEngineering

The invention relates to a resistive variable memory and a preparation method thereof, belonging to the technical field of information storage devices. In the metal-insulator-metal (MIM) sandwich structure of the resistive variable memory, the top electrode and the bottom electrode of the MIM structure are respectively metal electrodes, and the resistive variable medium between the metal electrodes is an amorphous strontium oxide thin film. The invention adopts the strontium oxide film as the resistive variable material, and can prepare the resistive variable memory with low power consumption, high storage window and good stability, thereby having the potential of multi-value storage and high-density storage.

Owner:陕西翱翔辐射探测科技有限公司

A SrO-based resistive memory and a preparation method thereof

ActiveCN109273597AGood resistive propertiesImprove stabilityElectrical apparatusHigh densityMetal electrodes

The invention relates to a resistive memory and a preparation method thereof, belonging to the technical field of information storage devices. The Resistive memory metal-insulator-metal (MIM) structure has a sandwich structure, wherein the top electrode and the bottom electrode of the MIM structure are respectively metal electrodes, and the resistance medium between the metal electrodes is an amorphous strontium oxide film. As that strontium oxide thin film is use as a resistive material, the resistive memory with low power consumption, high storage window and good stability can be prepare, thus having the potential of multi-value storage and high density storage.

Owner:陕西翱翔辐射探测科技有限公司

Programing method for ferroelectric dynamic random access single-tube unit array

InactiveCN100390901CThe range of programming voltages increasesReduce restrictionsDigital storageBit lineManufacturing technology

The present invention provides a programming method of ferro-electric dynamic random memory single-tube unit array, belonging to the field of semiconductor integrated circuit design and manufacture technology. In the course of programming true unit said method can apply the voltage for inhibiting programming to word line, bit line and source line of non-true unit so as to make the range of programming voltage which can be applied to said single-tube unit array be further increased, so that the larger storage window can be obtained.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

A kind of memory and its manufacturing method

ActiveCN102810541BIncrease the number of capturesHigh densitySolid-state devicesSemiconductor/solid-state device manufacturingGratingTrapping

The invention discloses a memory and a manufacturing method of the memory. The memory structurally comprises a semiconductor substrate, a channel region, a grating stack and a source region or a drain region, wherein the channel region is arranged on the semiconductor substrate; the grating stack is arranged on the channel region and comprises a tunneling layer, a charge trapping layer, a barrier layer and a gate electrode layer; the tunneling layer is arranged on the channel region; the charge trapping layer is arranged on the tunneling layer; the barrier layer is arranged on the charge trapping layer; the gate electrode layer is arranged on the barrier layer; the source region or the drain region is arranged on two sides of the channel region and is embedded in the semiconductor substrate; and the charge trapping layer comprises a first charge trapping layer and a second charge trapping layer(s), wherein the second charge trapping layers which are arranged above or / and below the first charge trapping layer.

Owner:ZHUHAI CHUANGFEIXIN TECH CO LTD

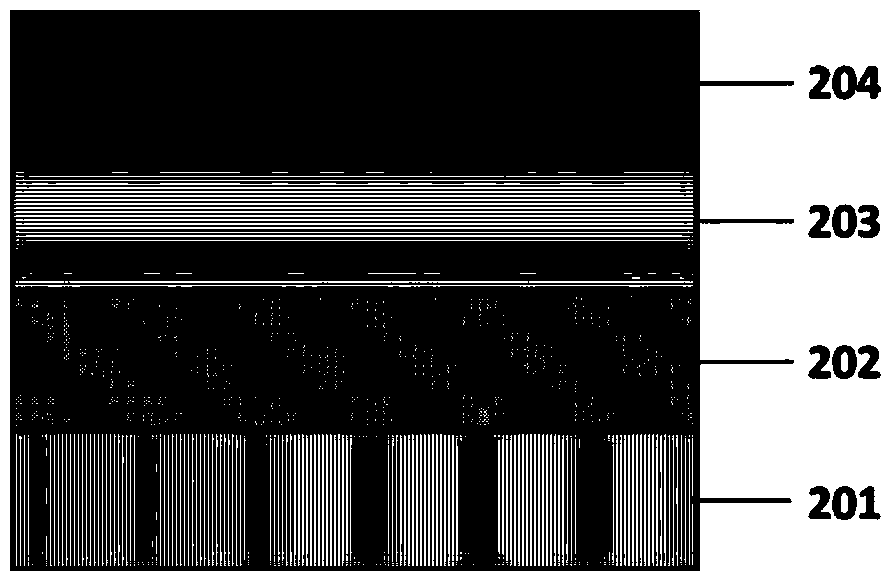

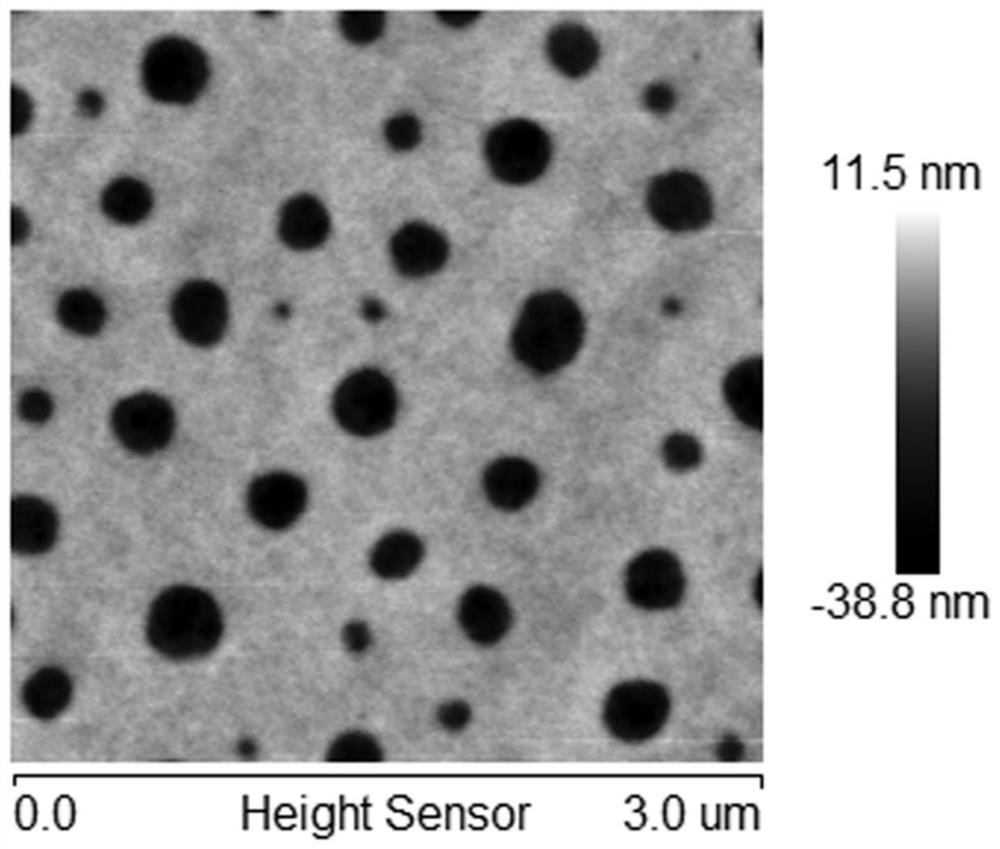

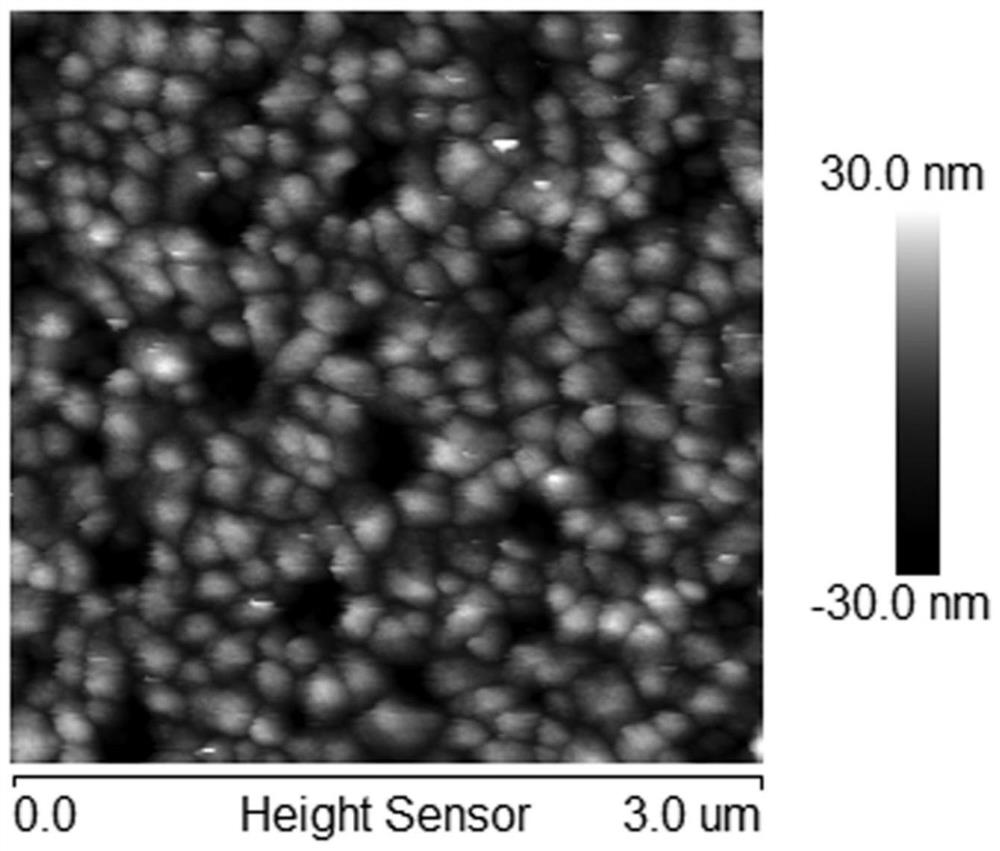

Nano tunnel and silver nanoparticle coexisting organic field effect transistor memory and preparation method thereof

PendingCN114512607AShape adjustableIncrease storage windowSolid-state devicesSemiconductor/solid-state device manufacturingOrganic field-effect transistorNanohole

The invention discloses a nano tunnel and silver nanoparticle coexisting organic field effect transistor memory and a preparation method thereof. The memory structurally comprises a source and drain electrode, an organic semiconductor layer, a charge storage layer, a gate insulating layer, a substrate and a gate electrode formed on the substrate from top to bottom in sequence, wherein the charge storage layer comprises two layers, the first layer is a polymer layer with a nano tunnel structure, and the second layer is a silver nanoparticle layer uniformly distributed on the polymer layer. The charge storage layer is prepared by adopting a secondary spin-coating solution processing method, the preparation process is simple, and large-area preparation can be realized. The film morphology of the nanopore can be regulated and controlled by simply adjusting the spin-coating rotating speed through primary spin-coating, and then the silver nanoparticles are uniformly distributed on the nanopore morphology through secondary spin-coating. The storage capacity, the high mobility and the switch ratio are achieved, the stability is greatly improved, the price is low, the cost is saved, and popularization and integrated commercial application are facilitated.

Owner:NANJING UNIV OF POSTS & TELECOMM

A ferro-resistance variable memory and its writing method, reading method and preparation method

ActiveCN107946461BIncrease the on-off ratioIncrease storage windowElectrical apparatusElectrical resistance and conductanceHigh density

The invention discloses a ferro-resistance variable memory, a writing method, a reading method and a preparation method thereof. The ferroelectric RRAM includes a substrate layer, a bottom electrode, a switch layer and a top electrode stacked in sequence; the switch layer includes a ferroelectric layer and at least one semiconductor layer adjacent to the ferroelectric layer; the iron The electric layer is polarized under the application of an electric field for changing the potential barrier of the switch layer. In the present invention, at least one semiconductor layer is added to the switch layer, and the semiconductor layer is adjacent to the ferroelectric layer, which is equivalent to adding a variable barrier layer, which increases the resistance ratio of the high and low resistance states of the switch layer under the action of an electric field , that is, the storage window of the ferro-resistive variable memory is increased, and the high-density storage of the ferro-resistive variable memory is realized, and the problem of a small storage window of the ferro-resistive variable memory is solved.

Owner:SOUTH UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA

A kind of all-inorganic perovskite resistive variable memory and its preparation method

ActiveCN108539012BImprove solubilityEasy to prepareElectrical apparatusPerovskite (structure)Thin membrane

Owner:HUBEI UNIV

A kind of three-dimensional structure nand ferroelectric storage unit and its preparation method

ActiveCN112164699BIncrease storage windowImprove interface performanceSolid-state devicesSemiconductor devicesMemory cellFerroelectric thin films

A three-dimensional structure NAND ferroelectric storage unit and its preparation method, wherein the ferroelectric storage unit comprises: an oxide insulating layer, a channel layer, a channel buffer layer, a ferroelectric layer and a gate arranged in sequence from the inside to the outside A buffer layer and a gate; a channel buffer layer is arranged between the channel layer and the ferroelectric layer; and / or, a gate buffer layer is arranged between the ferroelectric layer and the gate. In the storage unit of the present invention, the buffer layer has the following effects: 1. It can induce the crystallization of the ferroelectric thin film to generate a ferroelectric phase; 2. It can reduce the adverse effects caused by the different crystallization characteristics of the channel layer and the ferroelectric layer during unified annealing and crystallization, and improve The quality and uniformity of the deposited film; 3. The buffer layer can improve the interface performance of the channel layer, reduce the leakage current, and improve the fatigue resistance of the device. Therefore, the buffer layer can improve the storage performance and uniformity of the storage unit in the three-dimensional structure as a whole, increase the storage window of the storage unit, improve the fatigue performance of the storage unit, and improve the uniformity of storage performance of multiple transistors.

Owner:XIANGTAN UNIV

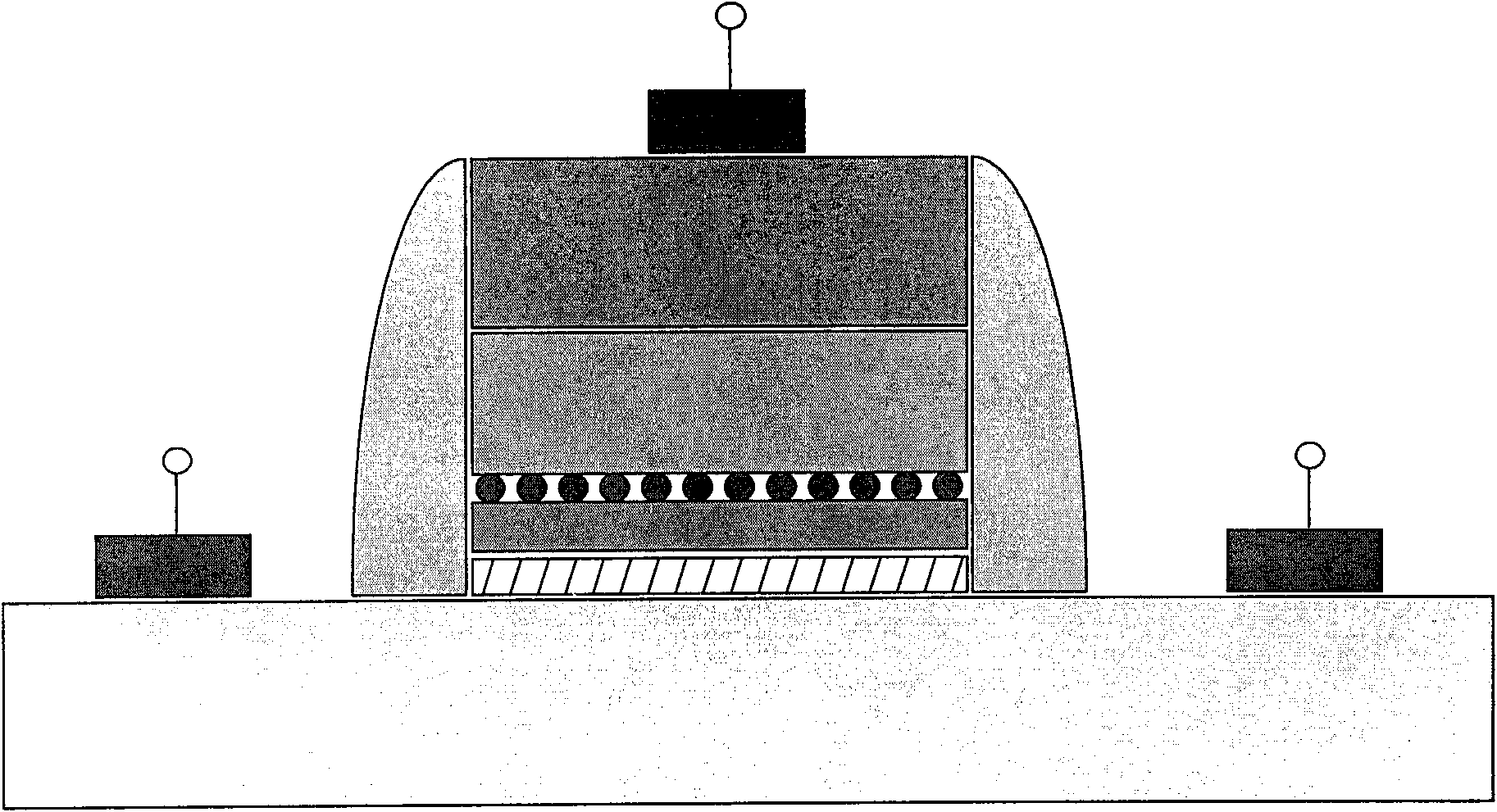

Multiple-valued non-volatile memory and preparation method thereof

ActiveCN102693984BImprove performanceReduce thicknessSolid-state devicesSemiconductor/solid-state device manufacturingBit lineGate dielectric

The invention relates to a multiple-valued non-volatile memory and a preparation method thereof. The memory comprises a semiconductor substrate, wherein both ends of the semiconductor substrate include a source electrode and a drain electrode respectively along the direction of a memory bit line and both ends of the semiconductor substrate include a shallow tunnel isolation structure respectively along the direction of a memory sub-line. A tunneling dielectric layer, a charge storage layer, a charge blocking layer, and a gate electrode are sequentially arranged on the semiconductor substrate, wherein the charge storage layer is a combination of two different storage materials which are alternatively arranged along the direction of the memory sub-line. The multiple-valued non-volatile memory of the invention adopts the storage layer formed by alternatively arranging the two different materials, which increases the storage density, promises a large window while reducing the thickness of a gate dielectric layer greatly,. Therefore, multiple-valued storage and high-density storage are realized the cost is reduced in turn.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Ferroelectric double-annealing process capable of enhancing storage window

PendingCN113889406AIncrease storage windowLarge storage window valueSolid-state devicesSemiconductor/solid-state device manufacturingMetallurgyDevice material

The invention discloses a ferroelectric double-annealing process capable of enhancing a storage window. According to the method, pre-annealing is carried out before a functional layer is grown on a ferroelectric memory, and post-annealing is carried out after an upper electrode is grown; the pre-annealing means that the memory on which the functional layer is to be grown is placed in an annealing furnace, the temperature is raised at the speed of V1 in the atmosphere of nitrogen, when the temperature reaches 200-500 DEG C, the temperature is kept for T1, after T1, rapid annealing is carried out, and when the temperature is reduced to 40-60 DEG C, the memory on which the functional layer is to be grown is taken out; and the post-annealing refers that the memory on which the upper electrode is grown is placed into an annealing furnace, the temperature is raised at a speed of V2 in a nitrogen atmosphere, the temperature for T2 is kept when the temperature reaches 400-700 DEG C, quick annealing is performed after T2, and the memory on which the upper electrode is grown is taken out when the temperature reaches 40-60 DEG C. Compared with a functional layer which is not pre-annealed, the semiconductor device has a larger storage window.

Owner:SHANDONG UNIV