Semiconductor structure and forming method thereof

A technology of semiconductor and channel structure, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., to reduce damage, improve uniformity, and reduce process difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

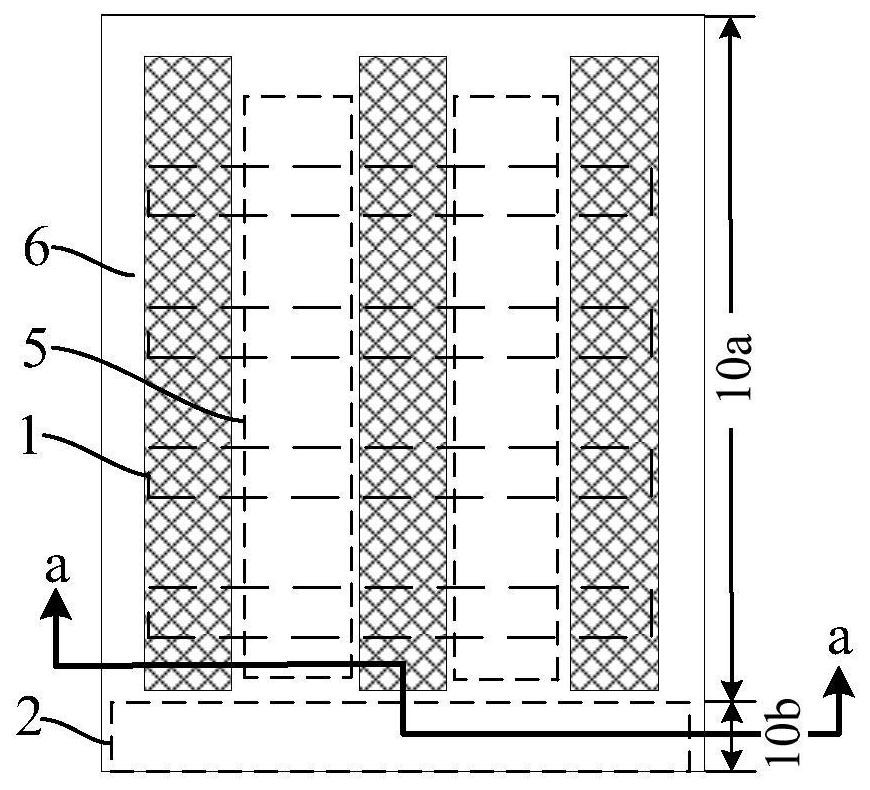

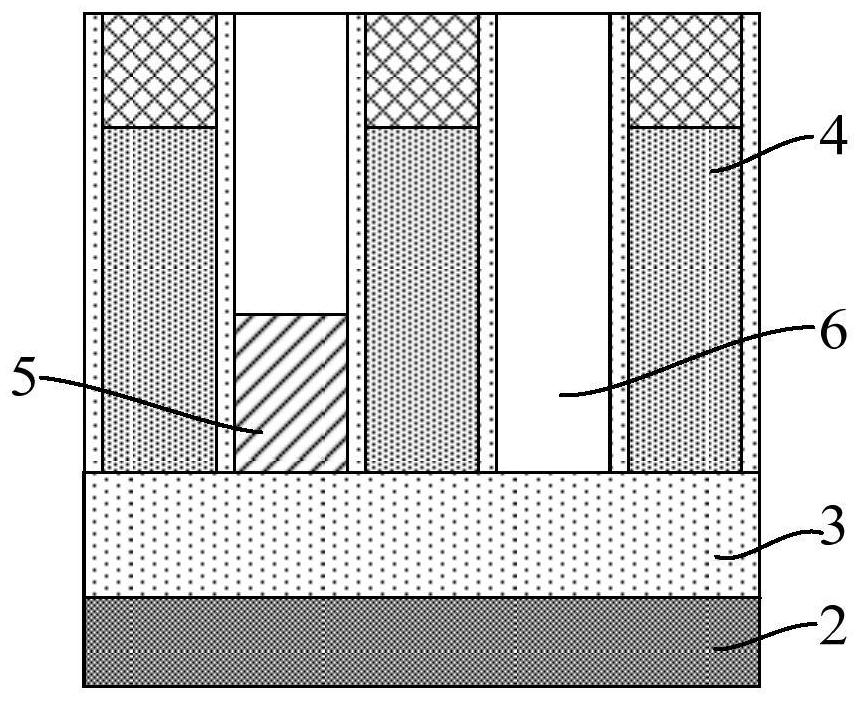

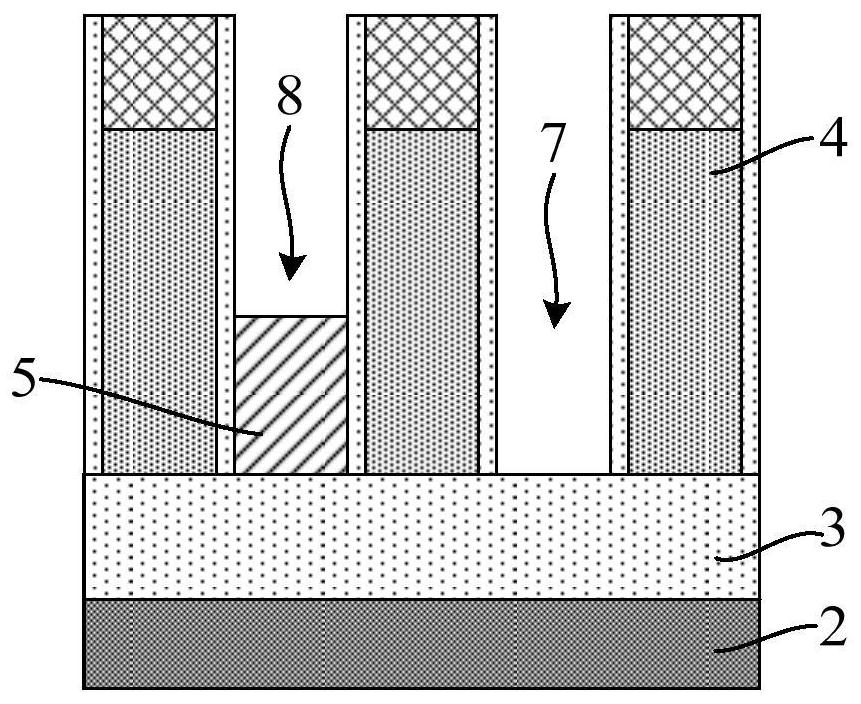

[0014] It can be seen from the background art that currently, forming a conductive plug (Via-BPR) for connecting buried power rails is a big challenge. The reason why forming a conductive plug (Via-BPR) is relatively challenging is now analyzed in combination with a method for forming a semiconductor structure. Figure 1 to Figure 5 It is a structural schematic diagram corresponding to each step in a method for forming a semiconductor structure.

[0015] refer to figure 1 with figure 2 , figure 1 for top view, figure 2 yes figure 1 A cross-sectional view along the aa direction provides a substrate (not shown), including a device region 10a and a power rail region 10b. A discrete channel structure 1 is formed on the substrate of the device region 10a, and a discrete channel structure 1 is formed on the substrate of the power rail region 10b. There are power track lines 2, the extension direction of the power track lines 2 is parallel to the extension direction of the c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More