Pier type structure for diode on-chip test and preparation method thereof

A diode and bridge pier type technology is applied in the field of "bridge pier type" structure and its preparation, which can solve the problems that affect the accuracy of extraction parameters and cannot be eliminated, and achieve the effects of perfecting diode modeling, improving differences and improving accuracy.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The technical solutions provided by the present invention are further described below in conjunction with the examples.

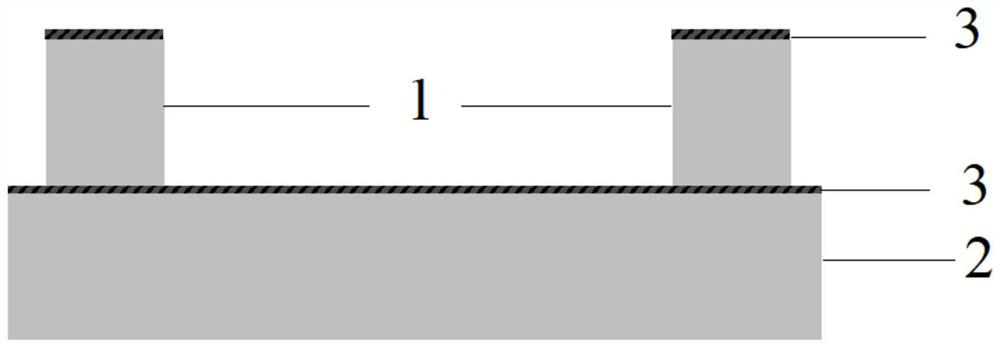

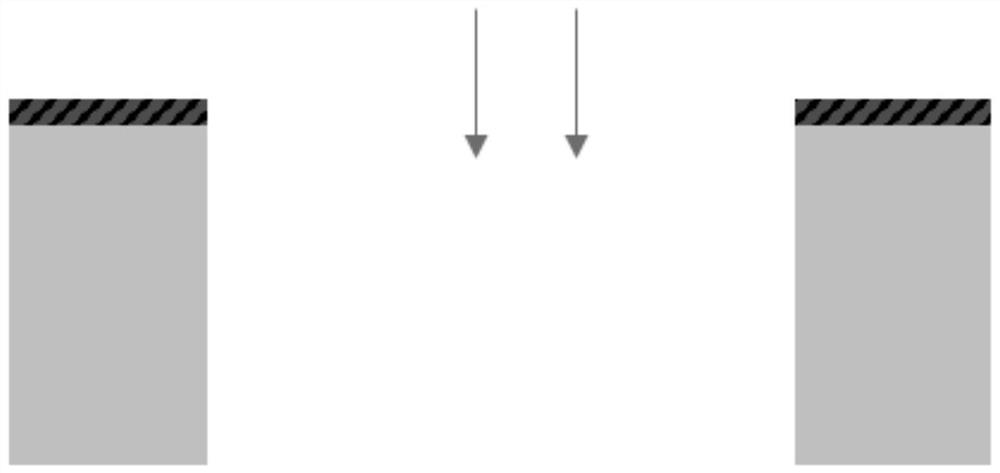

[0035] Such as figure 1 As shown, it is a schematic cross-sectional view of the "bridge pier" structure used for diode on-chip testing according to the present invention. The structure of the present invention includes: a "bridge pier" structure 1 arranged on a silicon gasket 2, and the "bridge pier" "Formula" structure 1 includes two pillars or platforms such as cuboids, which are used to support the monolithic circuit to be tested and bear the pressure of the probes during the test. There is a layer of photoresist 3 on the surface of the "bridge pier" structure 1. When assembling the monolithic circuit to be tested, an alignment structure is provided on the front side to realize the alignment between the monolithic circuit to be tested and the "bridge pier" structure 1. alignment, so that the monolithic circuit to be tested is assembled on the pho...

PUM

| Property | Measurement | Unit |

|---|---|---|

| height | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More