Global layout method of clock-driven fpga chip based on multi-electric field model

A global layout, clock-driven technology, applied in electrical digital data processing, instrumentation, computing and other directions, can solve the problems affecting the quality of layout results, can not achieve good layout quality, poor results, etc., to achieve good computing efficiency and layout results quality effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention is further described by example, but does not limit the scope of the present invention in any way.

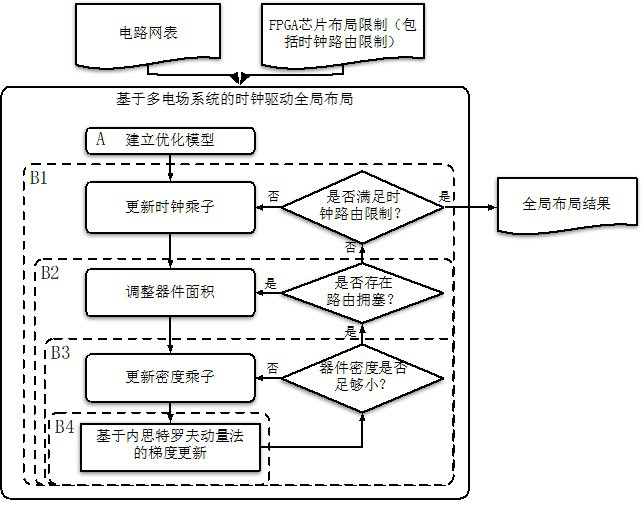

[0029] The present invention provides an efficient clock-driven FPGA global layout algorithm based on a multi-electric field system, the input includes a circuit netlist and FPGA chip layout limitations, the output takes into account the clock routing limitations of the FPGA global layout results.

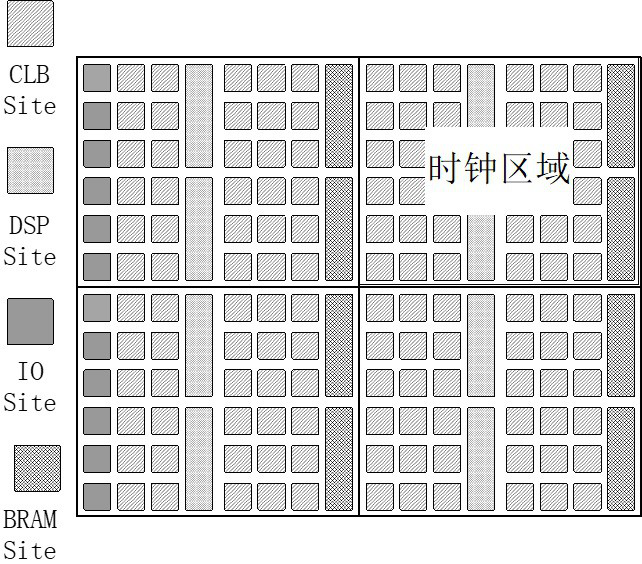

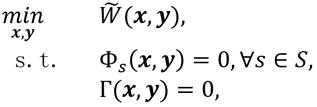

[0030] The following first provides a description of the input of the present invention. In the present invention, the circuit netlist is used represents, where Represents a collection of devices, Represents a collection of hyper-edges between devices. Note In FPGA layout issues, a hyper-edge Multiple devices can be connected at the same time. Each device has its own type, in this embodiment, the device may be typed as a look-uptable (Look-upTable, hereinafter referred to as LUT), flip-flop (Flip Flop, hereinafter referred to as FF), digital signal proce...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More