Method of realizing router chip of group exchange network with FPGA device

A technology for switching networks and devices, applied in the direction of logic circuits using specific components, logic circuits using basic logic circuit components, electrical components, etc. The problem of high development cost is easy to set up and expand, the communication bandwidth is improved, and the communication protocol is simplified.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] Compared with ASIC devices, FPGA devices have the advantages of field programming. With the continuous improvement of production technology, the integration and working speed of FPGA devices have been greatly improved. The logic resources provided inside them, such as digital clock managers , block memory, multiplexer, double-rate flip-flop, etc., can fully meet the requirements of routing chips for logic resources and clock frequency. Using FPGA devices to realize routing chips has the advantages of short design cycle, easy design improvement, and high performance-price ratio. Mature logic implemented with FPGA can also be easily converted into ASIC.

[0020] The present invention will be described in detail below in conjunction with the accompanying drawings.

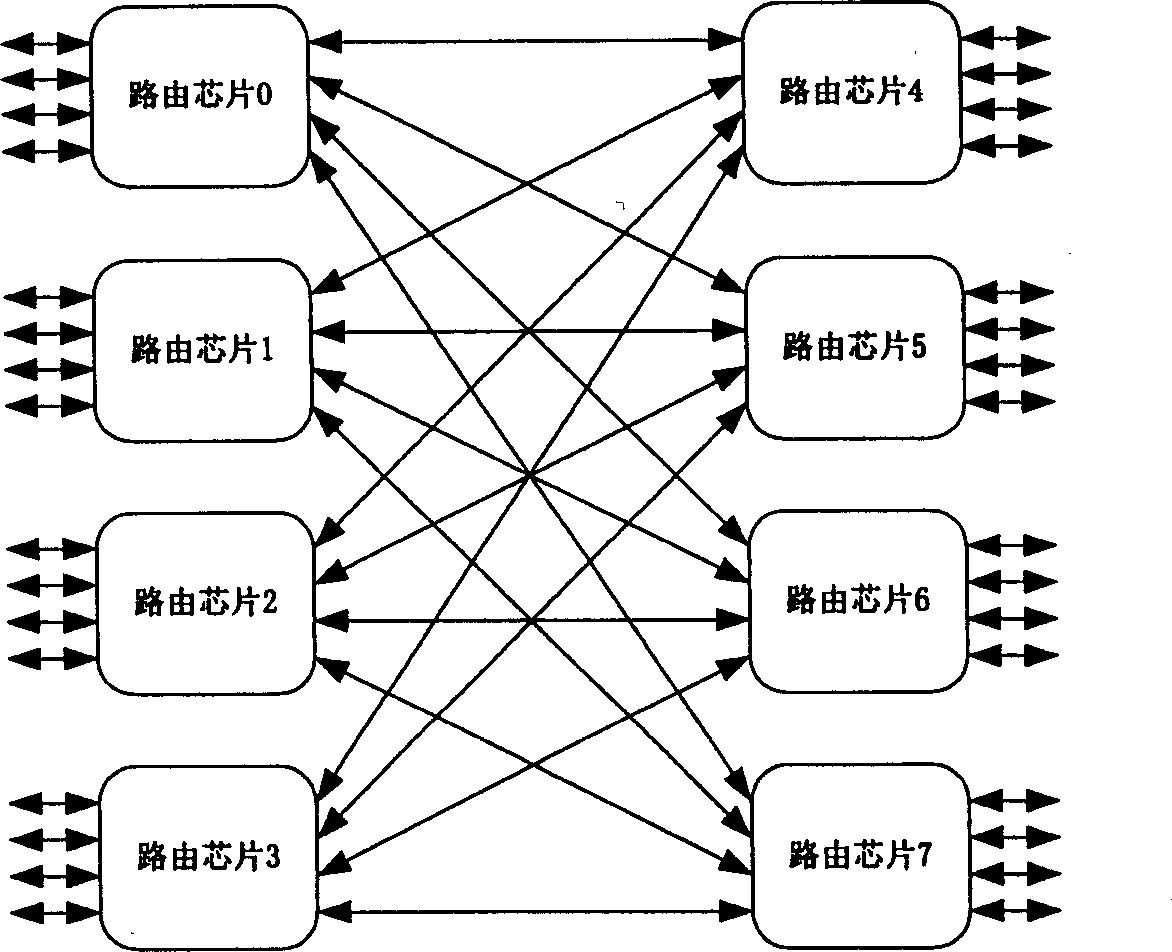

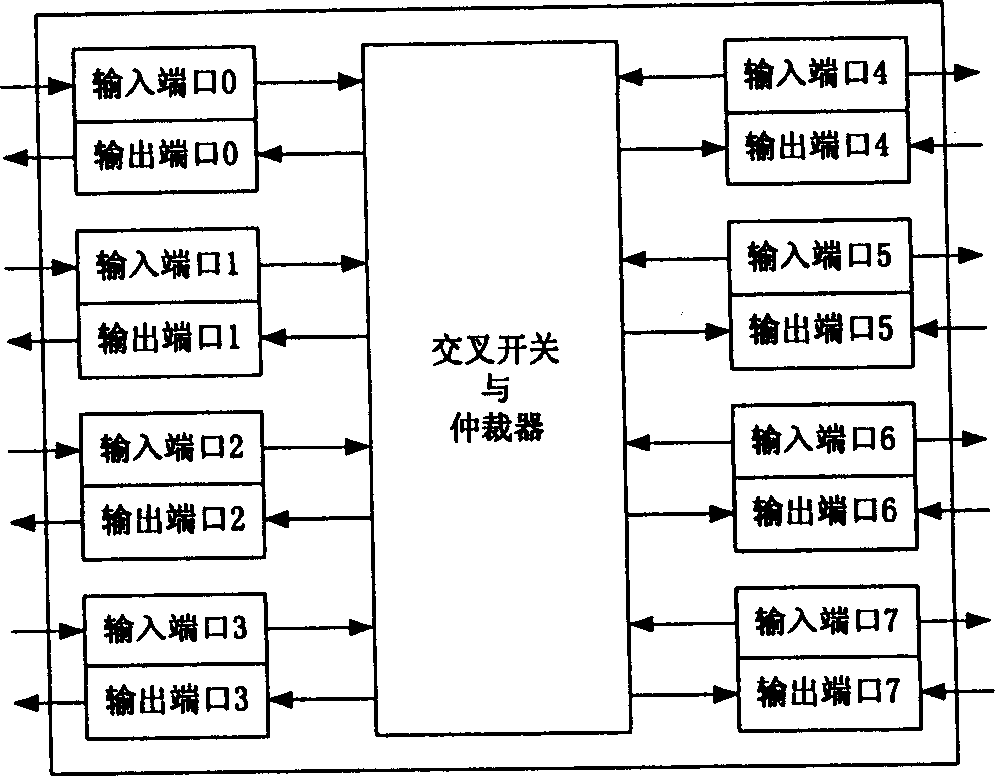

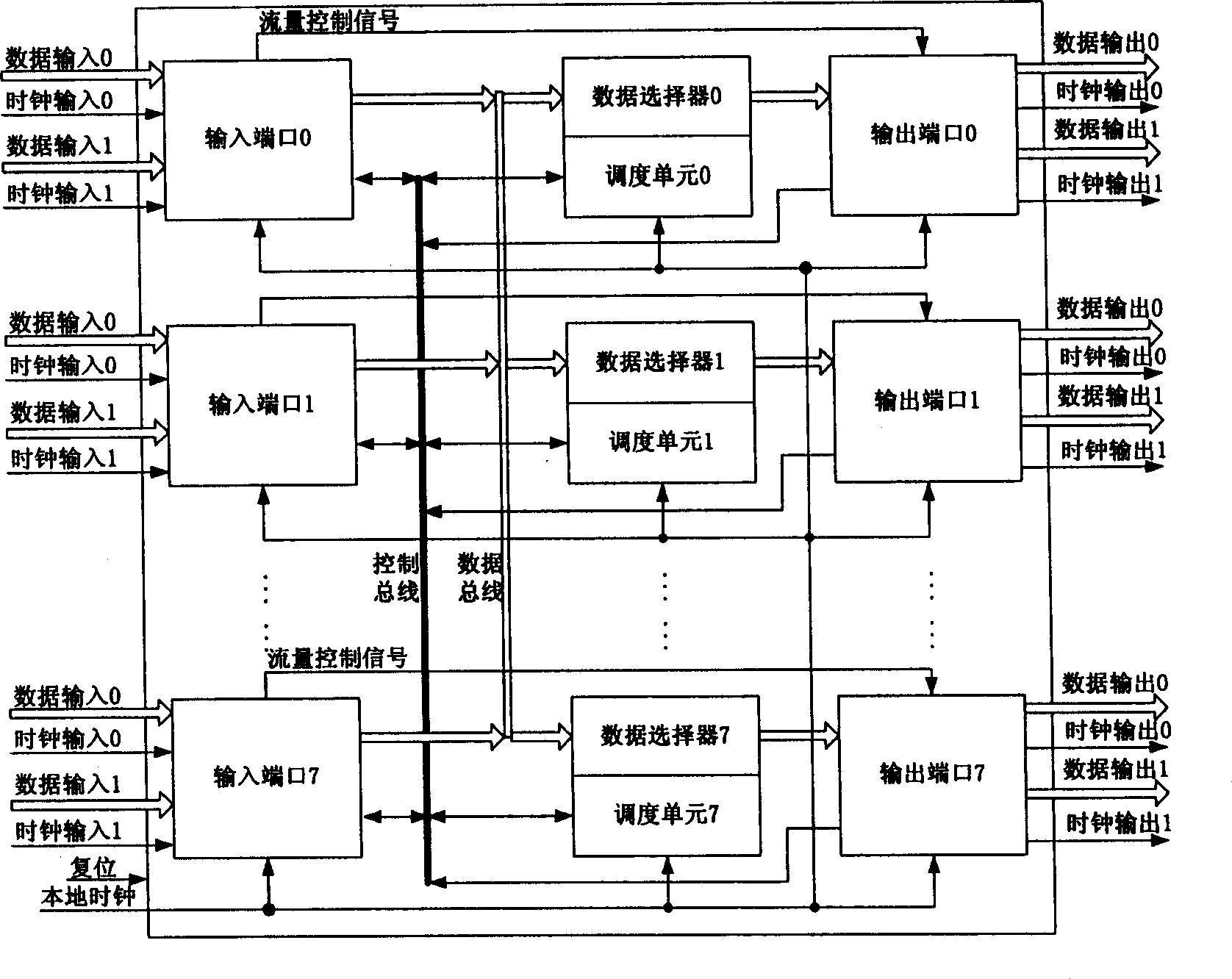

[0021] Such as figure 2 As shown, the method realizes a routing chip with 8 duplex ports, and the unidirectional transmission bandwidth of each port reaches 4Gbit / S. A scalable cluster switching network can...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More