System and method for fabricating diodes

a diode and diode technology, applied in the field of system and method for fabricating diodes, can solve the problems of preventing the commercialization of semiconductors, affecting the manufacturing of semiconductor/solid-state devices, and exhibiting a constant forward current density degraded forward voltage drop in current technology of sic pin and pn diodes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

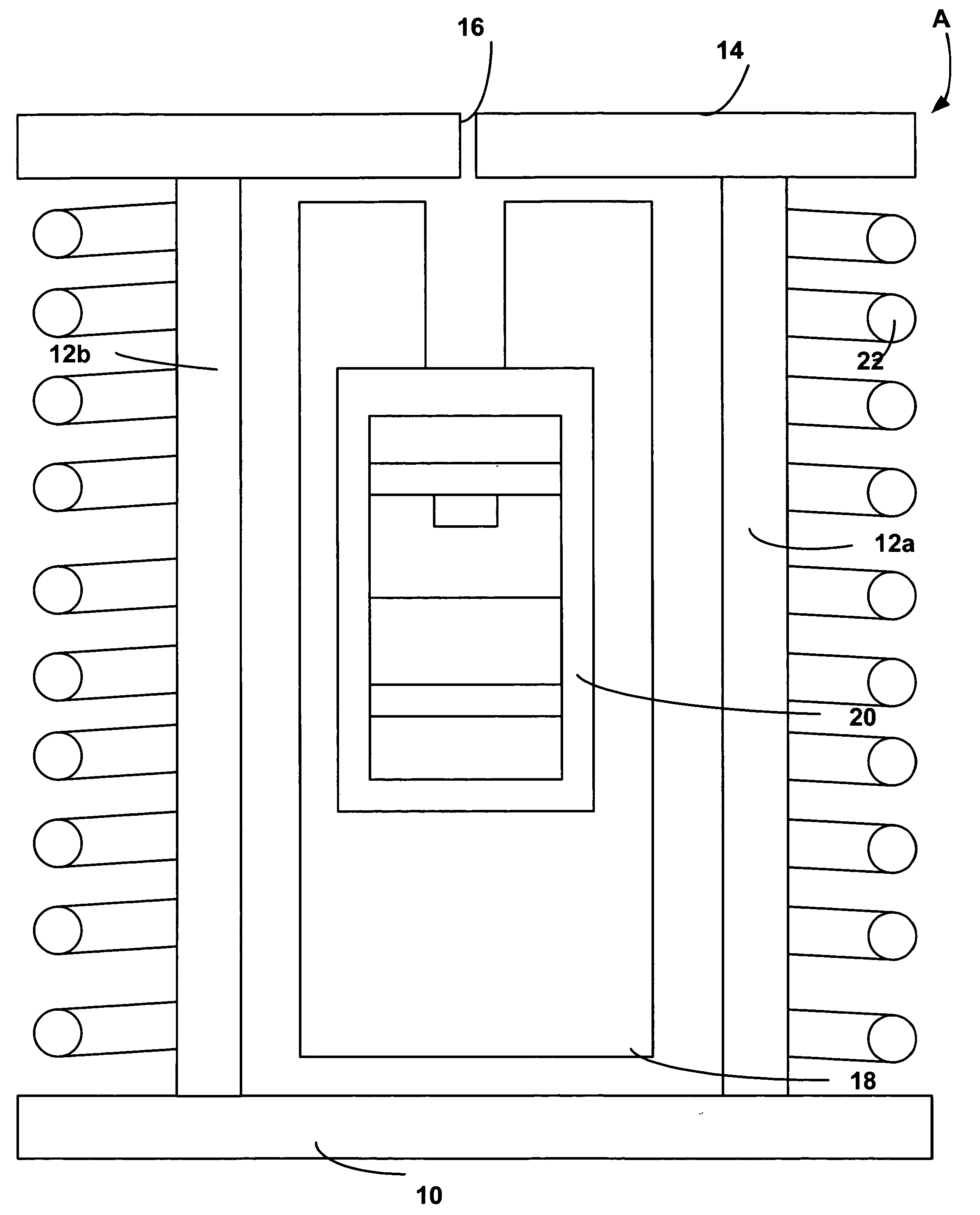

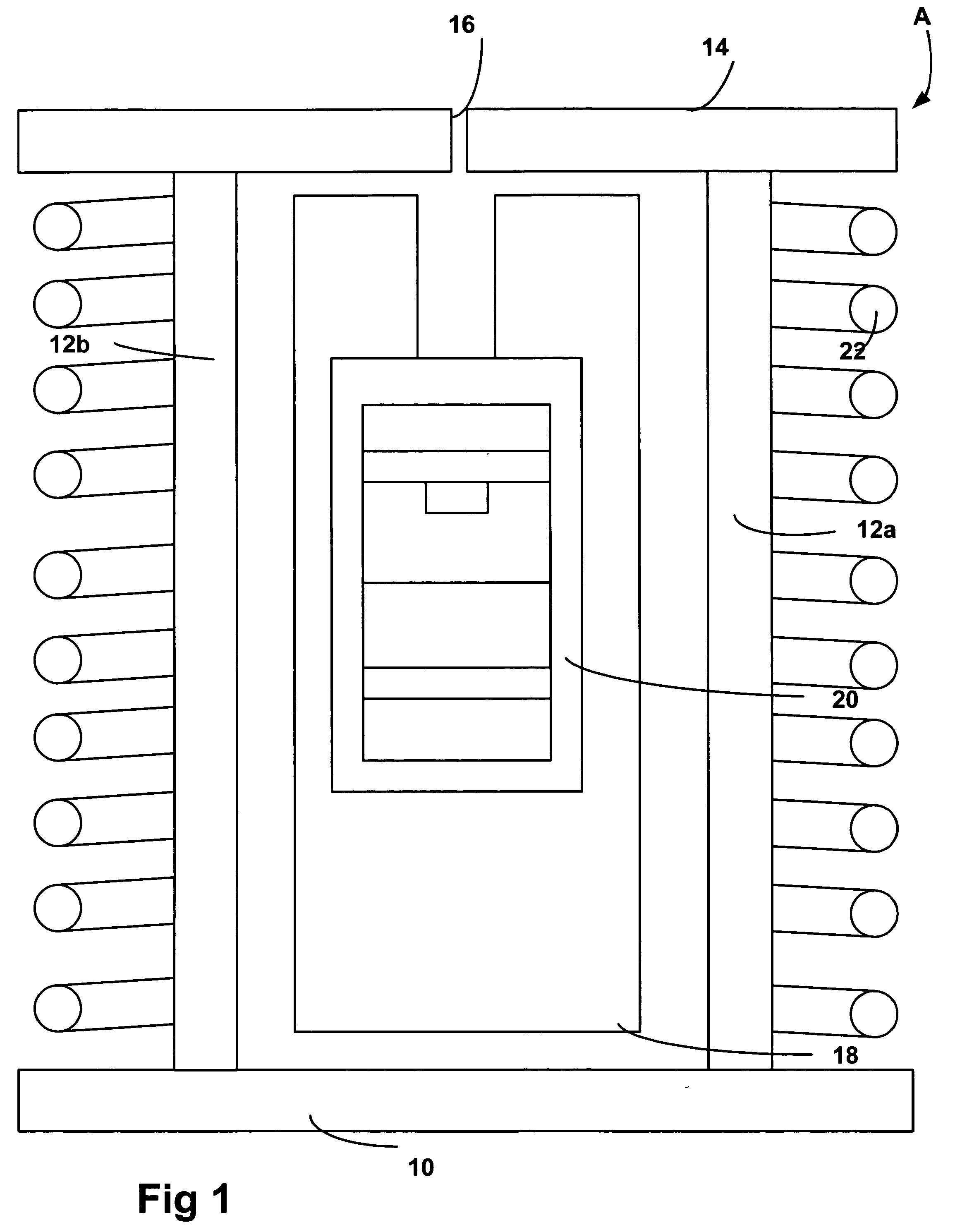

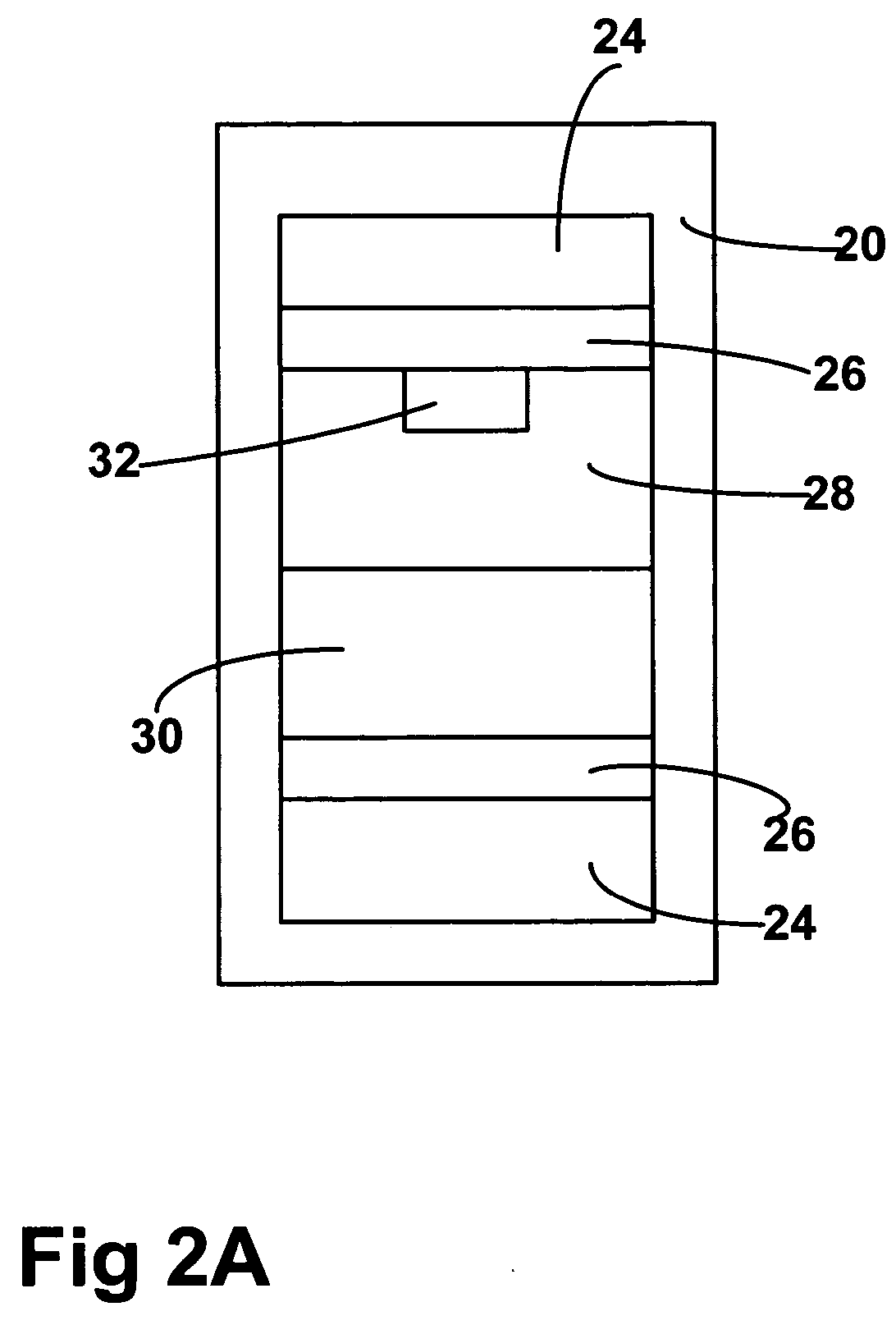

[0038] This invention is a novel system and method for PN and PiN diode fabrication, that results in operation of the diodes without voltage drift. This new process involves the formation of a graded, deep pn junction resulting from diffusion of acceptor impurity into a substrate, particularly a SiC substrate. It is advantageous to form a deep and graded doping concentration profile in the pn junction region to avoid the degradation of forward voltage drop. Deep pn junctions are advantageous to make sure that the pn junction is of sufficient distance from the near-surface p+ region to prevent adverse effects from any generation of structural defects. For example, when the p+ layer is Aluminum-doped, the effect of generated defects on the diode performance is not significant since the pn junction is located much deeper than the p+ Al surface layer.

[0039] By using diffusion, an acceptor impurity atom, such as Boron, penetrates much deeper into the substrate and forms a graded concent...

PUM

| Property | Measurement | Unit |

|---|---|---|

| pressure | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| pressure | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More