Preparation method of enhanced high-electron-mobility transistor

A high electron mobility, transistor technology, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve the problem of low carrier concentration in the p-type layer, achieve weakening passivation effect, and increase carrier concentration , the effect of increasing the ionization rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

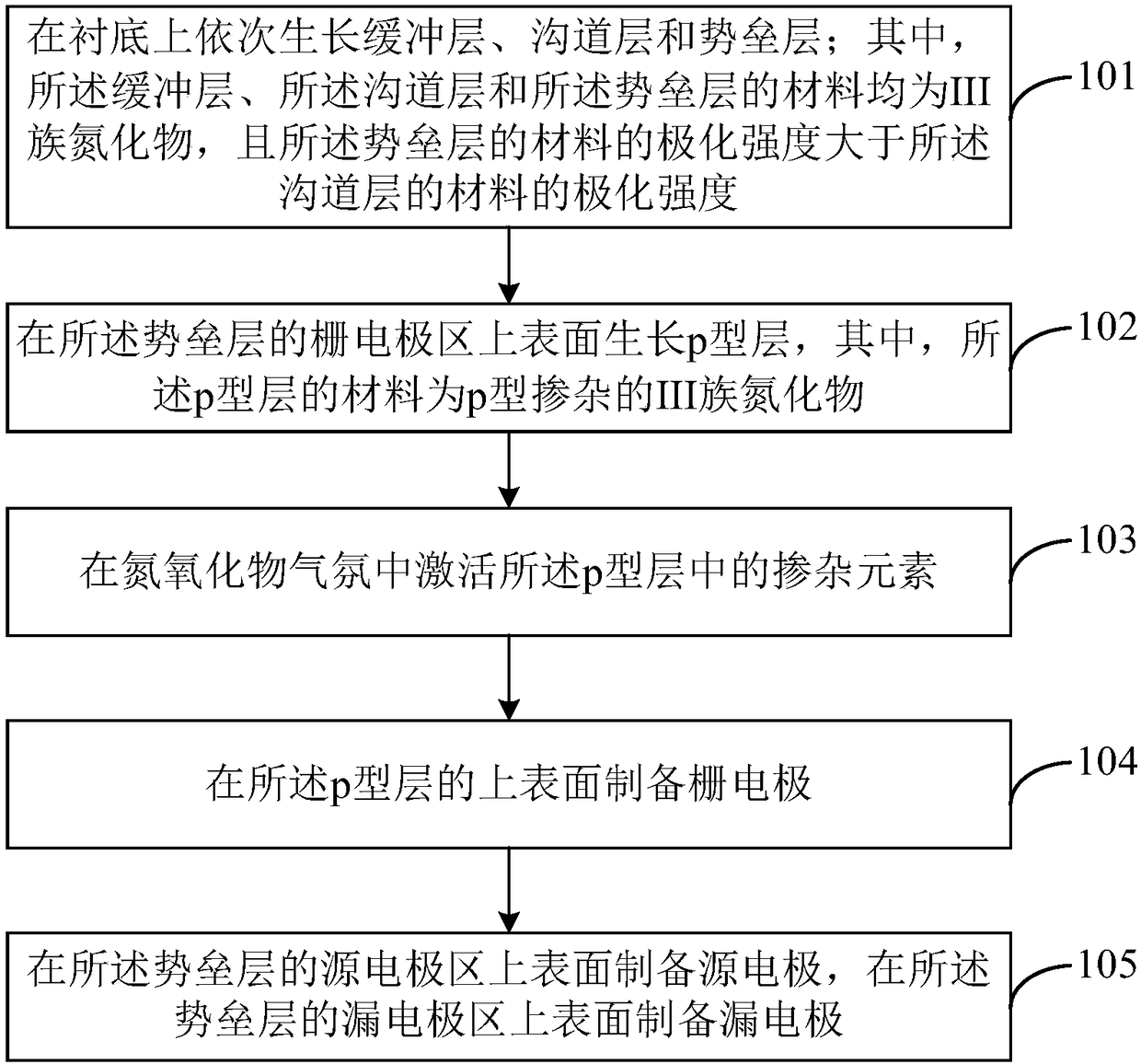

[0031] Please refer to figure 1 , a method for preparing an enhanced high electron mobility transistor, comprising:

[0032] Step S101, sequentially growing a buffer layer, a channel layer, and a barrier layer on a substrate; wherein, the materials of the buffer layer, the channel layer, and the barrier layer are all Group III nitrides, and the The polarization of the material of the barrier layer is greater than the polarization of the material of the channel layer.

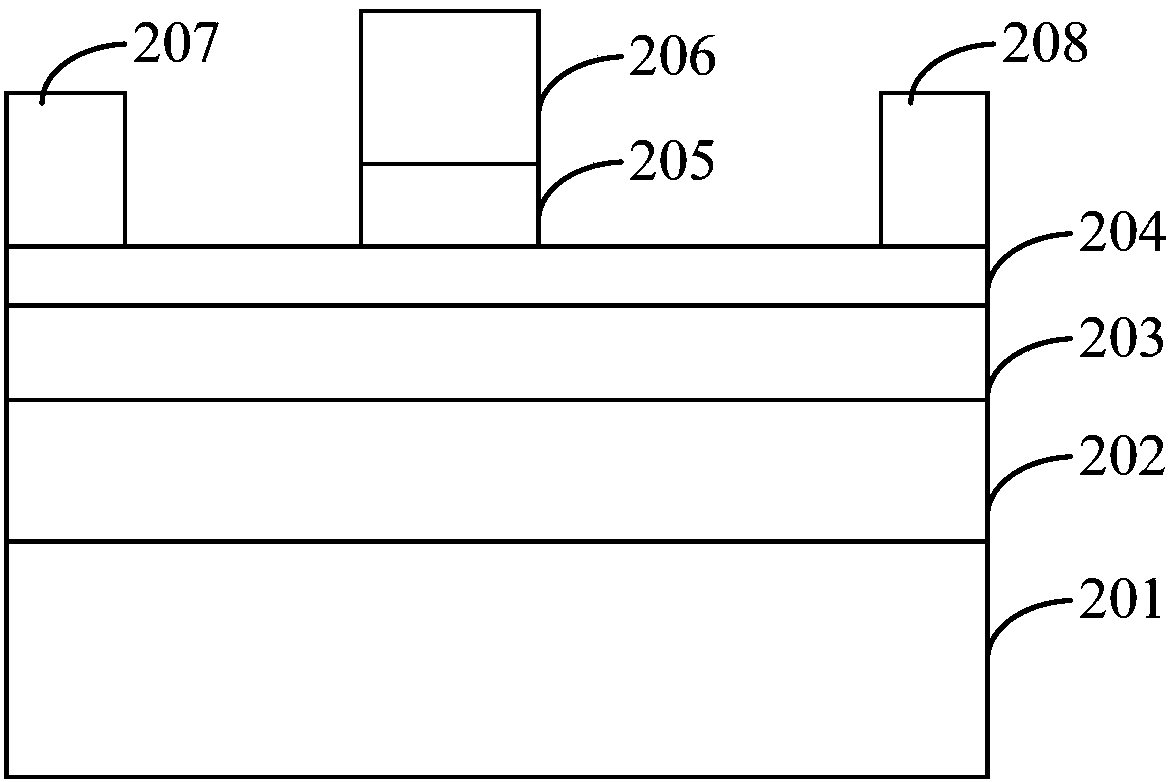

[0033] In the embodiment of the present invention, please refer to figure 2 , epitaxially epitaxially group III nitride buffer layer 202 , group III nitride channel layer 203 and group III nitride barrier layer 204 on the substrate 201 by an epitaxial process. Epitaxial processes include, but are not limited to, metal organic chemical vapor deposition, molecular beam epitaxy deposition, pulsed laser deposition, magnetron sputtering deposition, electron beam evaporation deposition, and chemical vapor depositio...

Embodiment 2

[0058] The preparation method of the enhanced high electron mobility transistor includes: first, a 1.5 μm GaN buffer layer, a 200 nm GaN channel layer, and a 20 nm Al 0.2 Ga 0.8 N barrier layer and 200nm GaN p-type layer, wherein the doping element in the p-type layer is Mg, and the doping concentration is 10 18 cm -3 , and then, put the substrate after growing the p-type layer into the magnetron sputtering chamber, and evacuate to 10 -6 mbar, N is passed into the magnetron sputtering chamber 2 O and O 2 , where N 2 The volume fraction of O is 40%, O 2 The volume fraction is 60%, the chamber pressure is controlled at 1mbar, and the atmosphere is stabilized for 2 minutes. After the atmosphere is stabilized, the magnetron sputtering power is set to 1W, and the Mg-doped p-type layer is plasma treated at room temperature. The processing time is 10s, and then use the photolithography process and the electron beam evaporation process to evaporate Ni / Au on the upper surface of ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More