Ferroelectric memory device and method of manufacturing the same

a technology of ferroelectric memory and ferroelectric technology, which is applied in the direction of digital storage, semiconductor devices, instruments, etc., can solve the problems of ferroelectric crystallinity impairment, electrical characteristics deterioration to a considerable extent, and hydrogen to be generated as a reaction by-produ

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

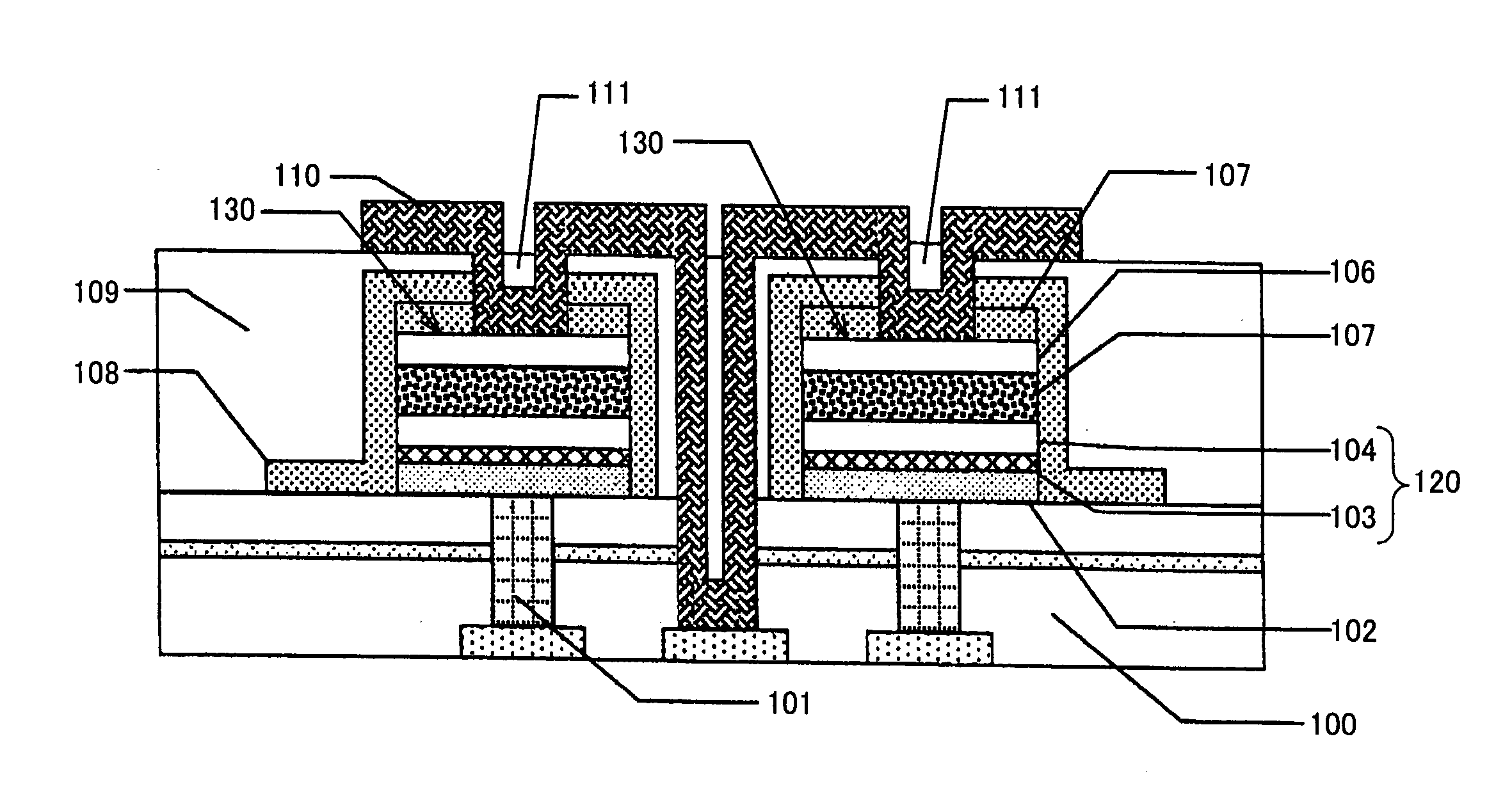

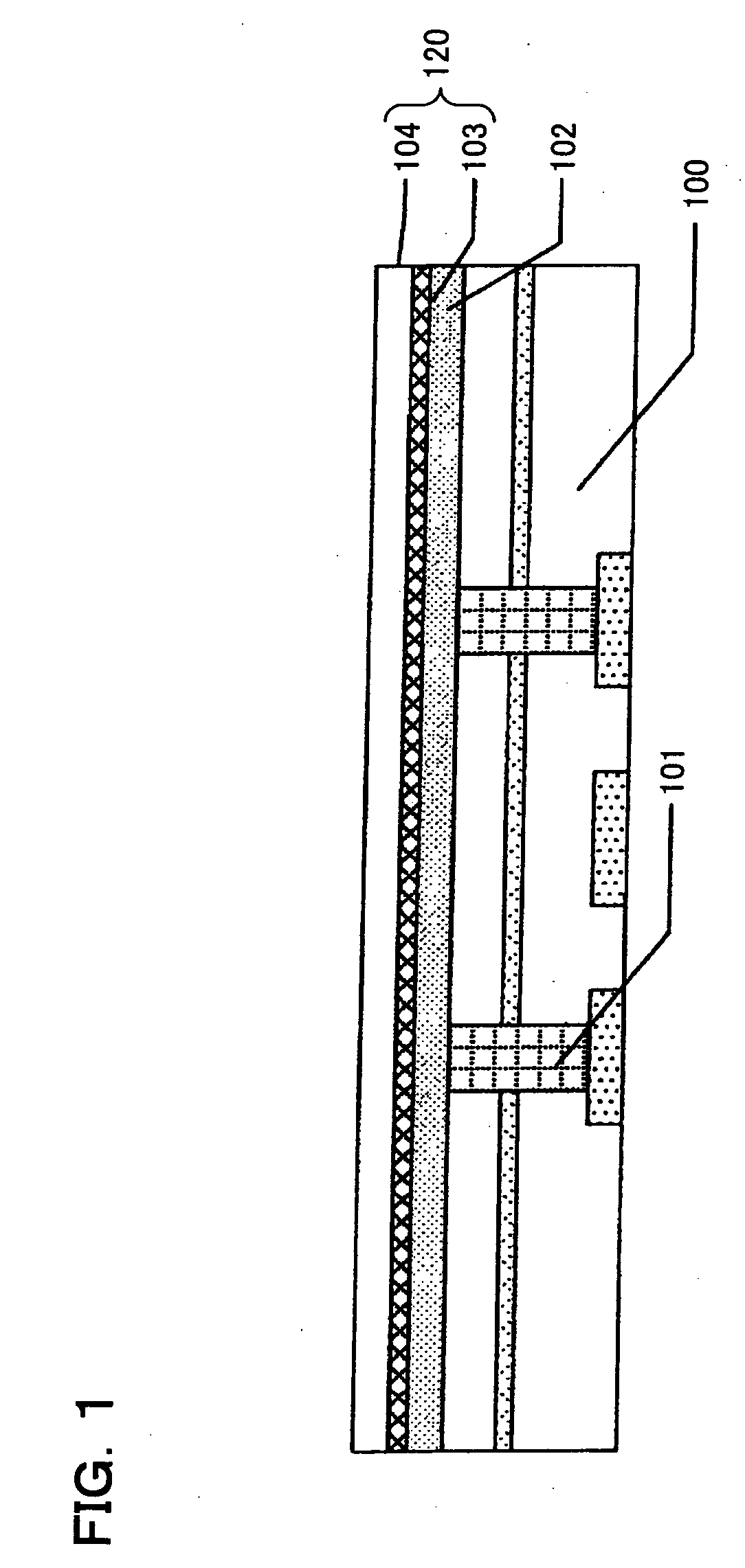

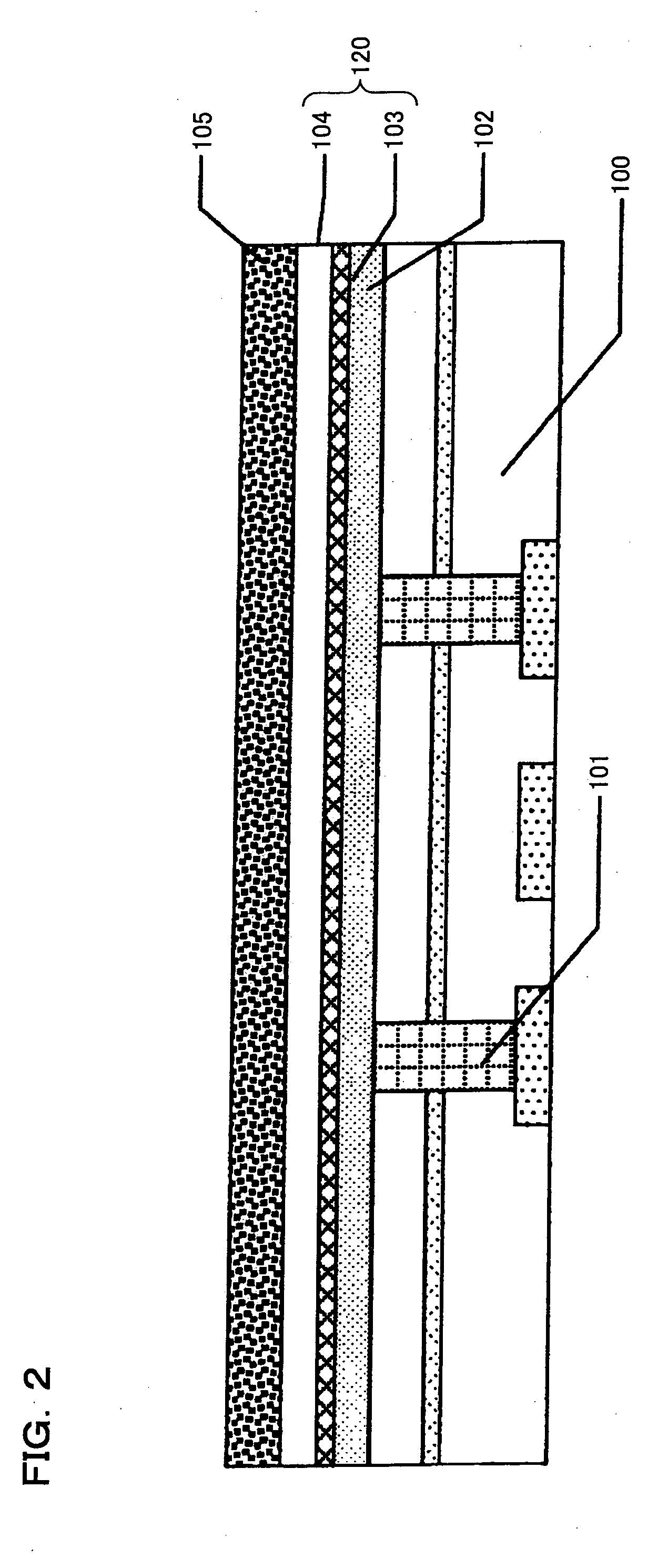

[0133] FIGS. 1 to 11 schematically show a method of manufacturing a ferroelectric memory device according to a first embodiment of the present invention.

[0134] (1) As shown in FIG. 1, a plug 101 is formed in a substrate 100, and a barrier metal layer 102 and a lower electrode 120 are formed on the plug 101.

[0135] A resist pattern for forming a contact hole is formed by a lithographic step on the substrate 100 on which a switching transistor is formed, and a contact hole is formed by using a dry etching method. After depositing a conductive film (tungsten film, for example) by using a chemical vapor deposition (CVD) method, the conductive film is ground by chemical mechanical polishing to form the plug (tungsten plug, for example) 101 in the contact hole. The substrate 100 includes a semiconductor substrate and an interlayer dielectric formed on the semiconductor substrate.

[0136] A titanium aluminum nitride (TiAlN) film is deposited as the barrier metal layer 102 by using a sputte...

second embodiment

[0171] FIGS. 16 to 26 schematically show a method of manufacturing a ferroelectric memory device according to a second embodiment of the present invention. In this embodiment, the patterning step of the upper electrode 206 is separately performed from the patterning step of the ferroelectric film 204, the lower electrode 220, and the barrier metal layer 202.

[0172] (1) As shown in FIG. 16, a plug 201 is formed in a substrate 200, and a barrier metal layer 202 and a lower electrode 220 are formed on the plug 201. The details are the same as described for the first embodiment. The lower electrode 220 may be formed by stacking an iridium (Ir) thin film 203 and a platinum (Pt) film 204.

[0173] (2) As shown in FIGS. 17 to 19, a ferroelectric film 205 and an upper electrode 206 are formed on the lower electrode 220.

[0174] The material and the deposition method for the ferroelectric film 205 and the upper electrode 206 are the same as described for the first embodiment. However, in this e...

third embodiment

[0198] FIGS. 29 to 41 schematically show a method of manufacturing a ferroelectric memory device according to a third embodiment of the present invention. In this embodiment, a third hydrogen barrier film 309 is formed in addition to first and second hydrogen barrier films 307 and 308.

[0199] (1) As shown in FIG. 29, a plug 301 is formed in a substrate 300, and a barrier metal layer 302 and a lower electrode 320 are formed on the plug 301. The details are the same as described in the first embodiment. The lower electrode 320 may be formed by stacking an iridium (Ir) thin film 303 and a platinum (Pt) film 304.

[0200] (2) As shown in FIGS. 30 and 31, a ferroelectric film 305 and an upper electrode 306 are formed on the lower electrode 320. The material and the deposition method for the ferroelectric film 305 and the upper electrode 306 are the same as described in the first embodiment.

[0201] (3) As shown in FIG. 32, the first hydrogen barrier film 307 is formed on the upper electrode...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More