Group III nitride semiconductor substrate and manufacturing method thereof

a technology of nitride and semiconductor substrate, which is applied in the direction of polycrystalline material growth, crystal growth process, chemically reactive gas growth, etc., can solve the problems of insufficient stability of electric characteristic and/or optical characteristic, difficult control of resistivity, and large in-plane distribution of resistivity, etc., to achieve low dislocation density and control the effect of resistivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

example 1

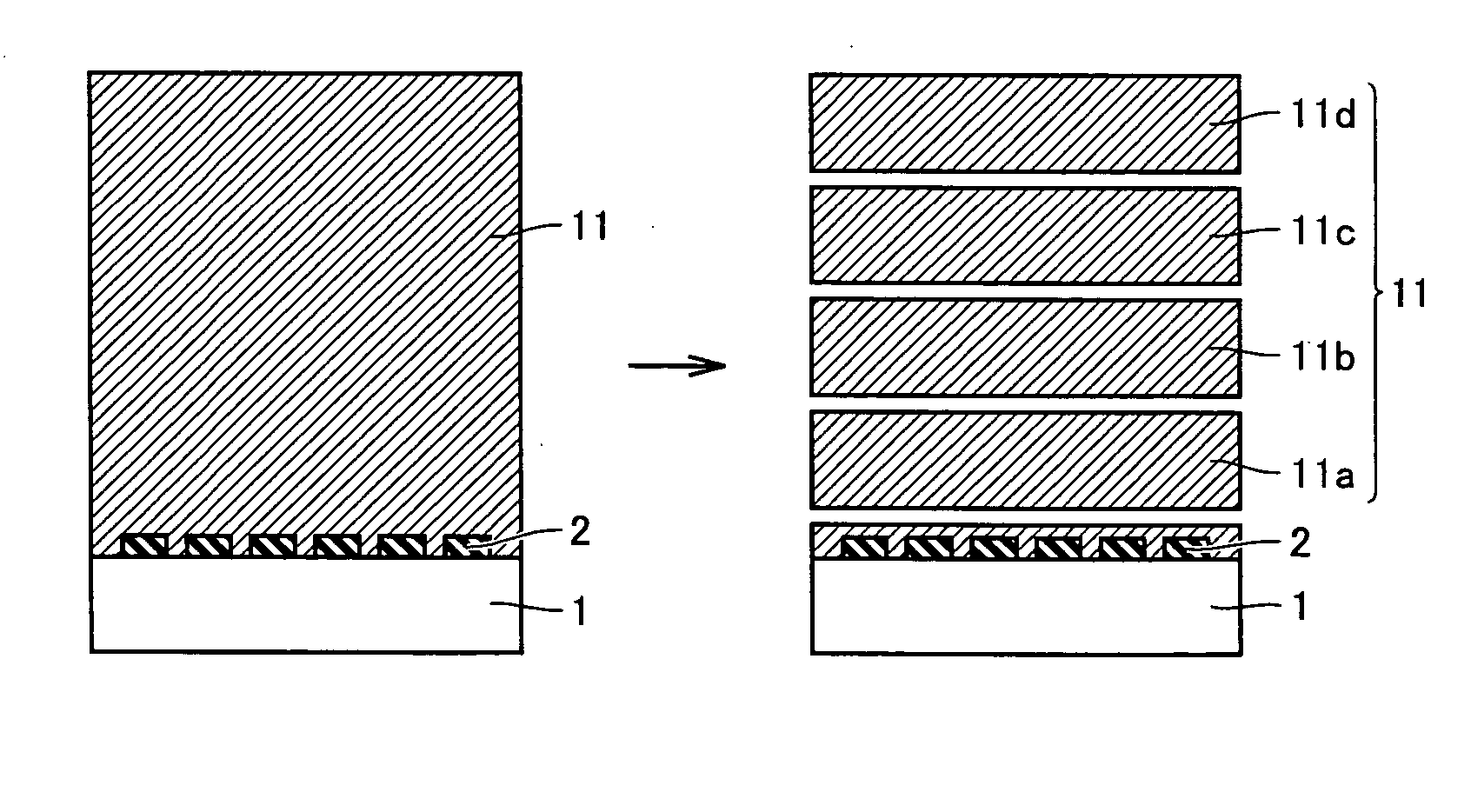

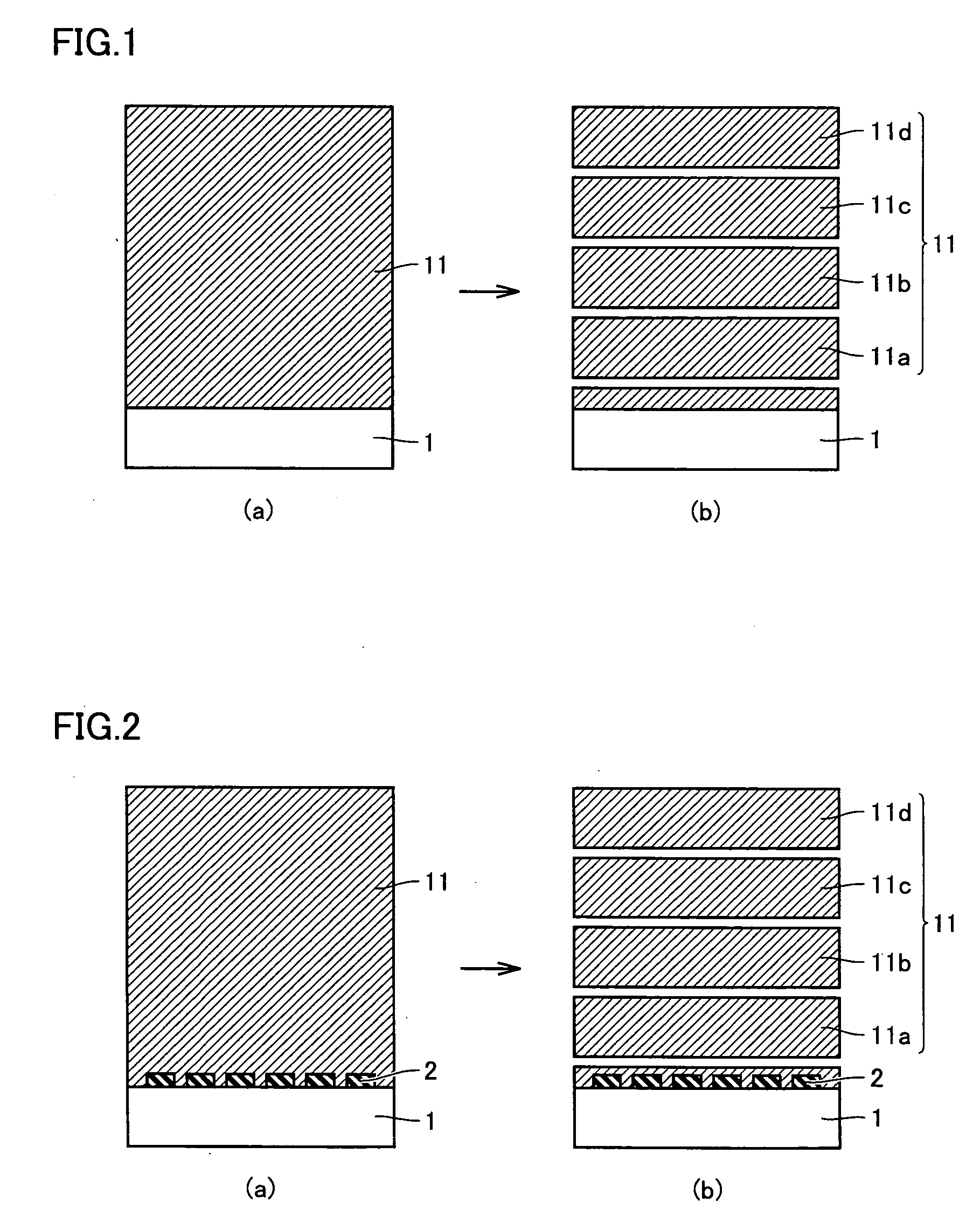

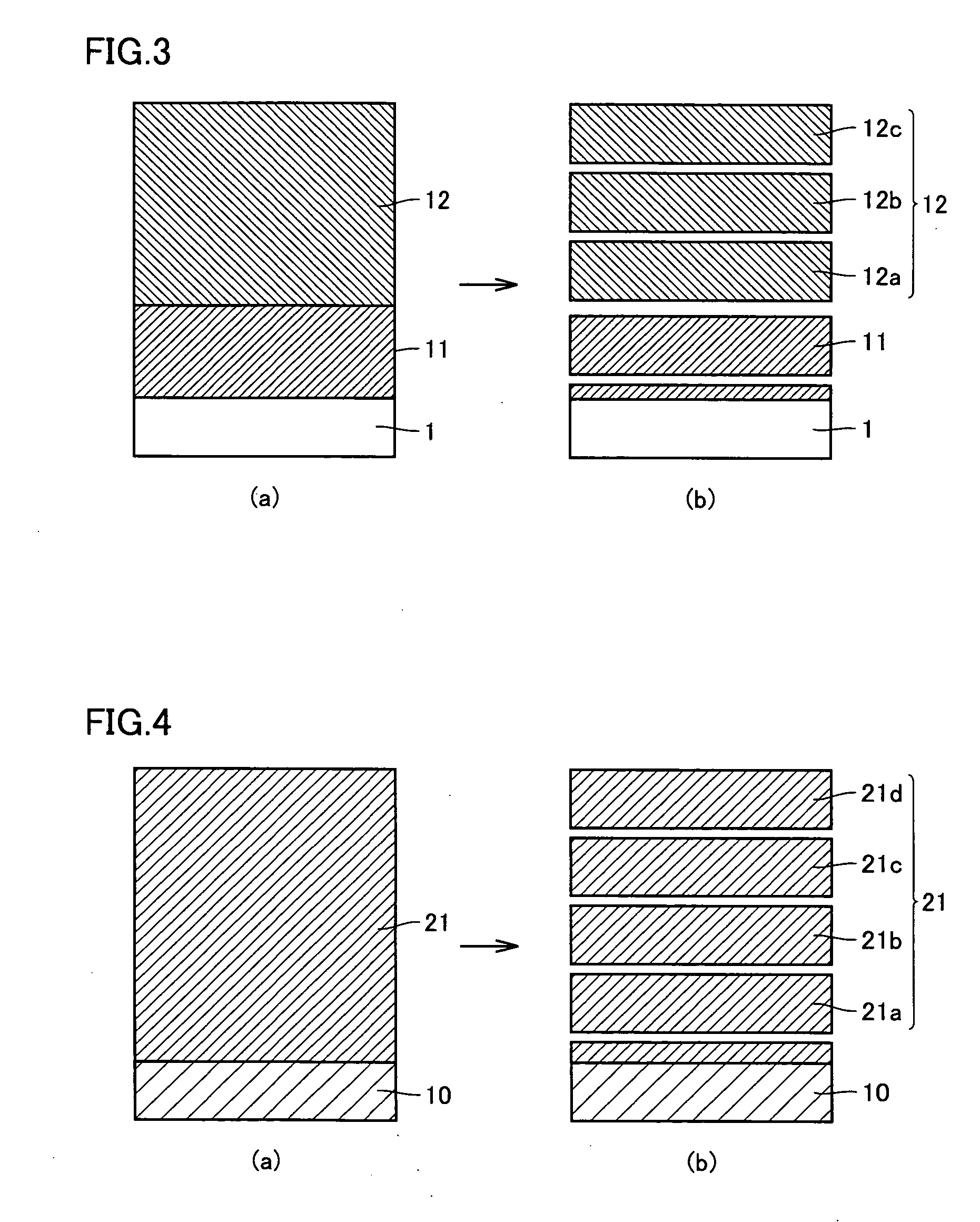

[0066] Referring to FIG. 1(a), the GaN substrate (the main surface of the substrate is at an angle of 1° in a direction of {1-100} surface with respect to (0001) surface) grown with the facet growth method (the method described in Patent Document 1) in the HVPE method was used as underlying substrate 1, and the high-resistivity GaN layer was grown as first group III nitride semiconductor layer 11 to a thickness of 2000 μm, using the HVPE method. A GaCl gas obtained by bringing an HCl gas in contact to gallium metal at 800° C. was used as the Ga source, and an NH3 gas was used as the N source. In addition, a methane gas was used as the impurity element raw material for adding C representing the impurity element. Moreover, an H2 gas was used as the carrier gas.

[0067] Here, the condition for epitaxial growth of the GaN layer using the HVPE method was set as follows: growth temperature (temperature of the underlying substrate) of 1050° C.; total pressure of 100 kPa (1.0 atmospheric pre...

example 2

[0070] The high-resistivity GaN substrate was obtained in a manner the same as in Example 1, except for using magnesium chloride (MgCl2) as the impurity element raw material. The minimum concentration of impurity element Mg in the obtained GaN substrate was 1×1018 cm−3, the in-plane distribution of the concentration of Mg 5 (maximum concentration / minimum concentration) was 2.5, the resistivity was not lower than 1×105 Ω·cm, the average dislocation density was 1×106 cm−2, the surface density of the dislocation-concentrated region was not higher than 1 cm−2, the half-width of the rocking curve in X-ray diffraction was 80 arcsec, the carrier density was not higher than 1×1015 cm−3, and the absorption coefficient for light of a wavelength of 450 nm was not smaller than 50 cm−1. Table 1 summarizes the result.

example 3

[0071] The high-resistivity GaN substrate was obtained in a manner the same as in Example 1, except for using an iron chloride (FeCl2) gas generated as a result-of reaction of iron and hydrochloric gas as the impurity element raw material. The 15 minimum concentration of impurity element Fe in the obtained GaN substrate was 1×1018 cm−3, the in-plane distribution of the concentration of Fe (maximum concentration / minimum concentration) was 2.0, the resistivity was not lower than 1×107 Ω·cm, the average dislocation density was 1×106 cm−2, the surface density of the dislocation-concentrated region was not higher than 1 cm−2, the half-width of the rocking curve in X-ray diffraction was 80 arcsec, the carrier density was not higher than b 1×1015 cm−3, and the absorption coefficient for light of a wavelength of 450 nm was not smaller than 50 cm−3. Table 1 summarizes the result.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| resistivity | aaaaa | aaaaa |

| angle | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More