Semiconductor device and method of forming the same

a technology of semiconductor devices and semiconductors, applied in the direction of semiconductor devices, basic electric elements, electrical appliances, etc., can solve the problems of unfavorable jfet resistance increase, high cost of sic wafers in comparison with sic wafers, and high cost of sic wafers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

first embodiment

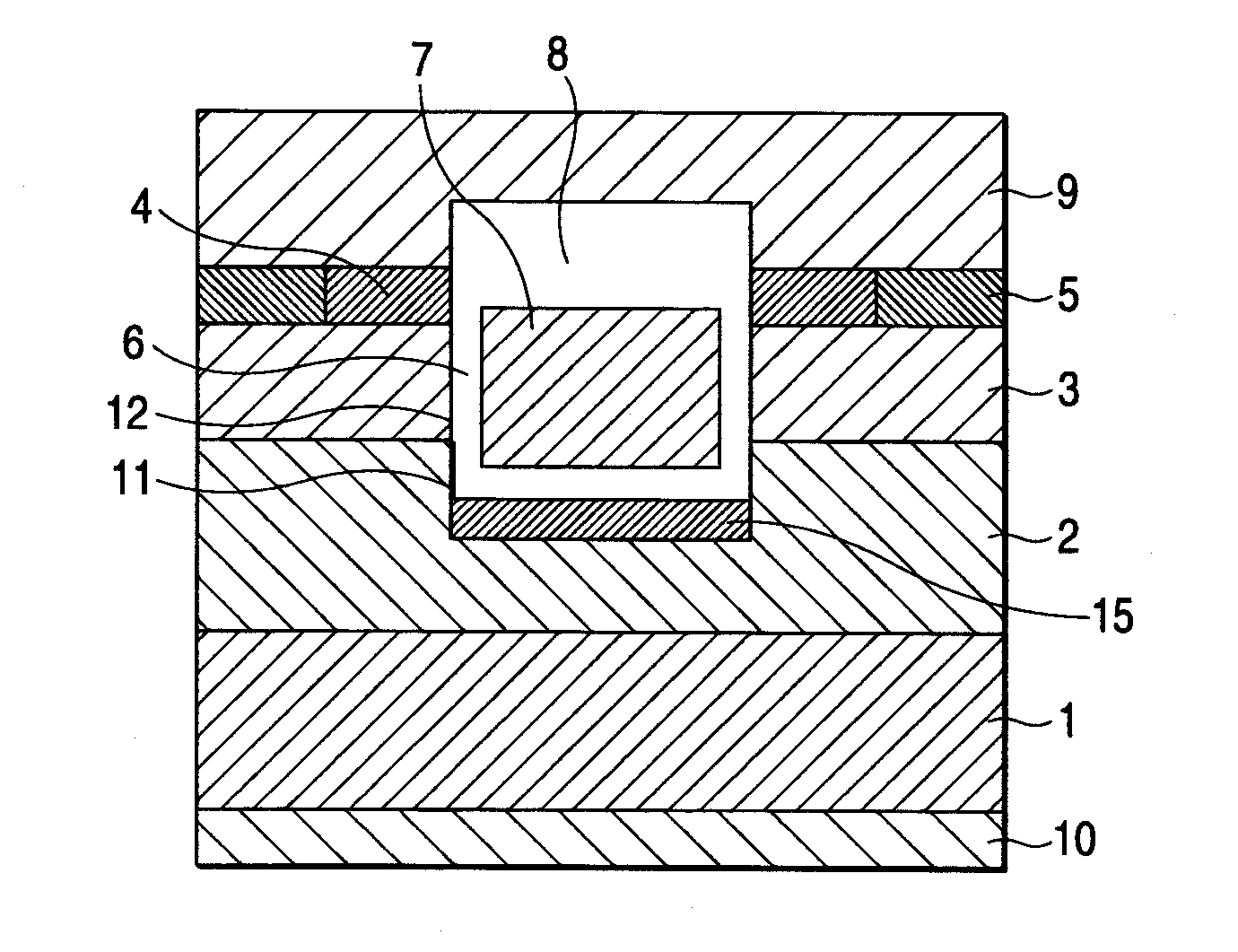

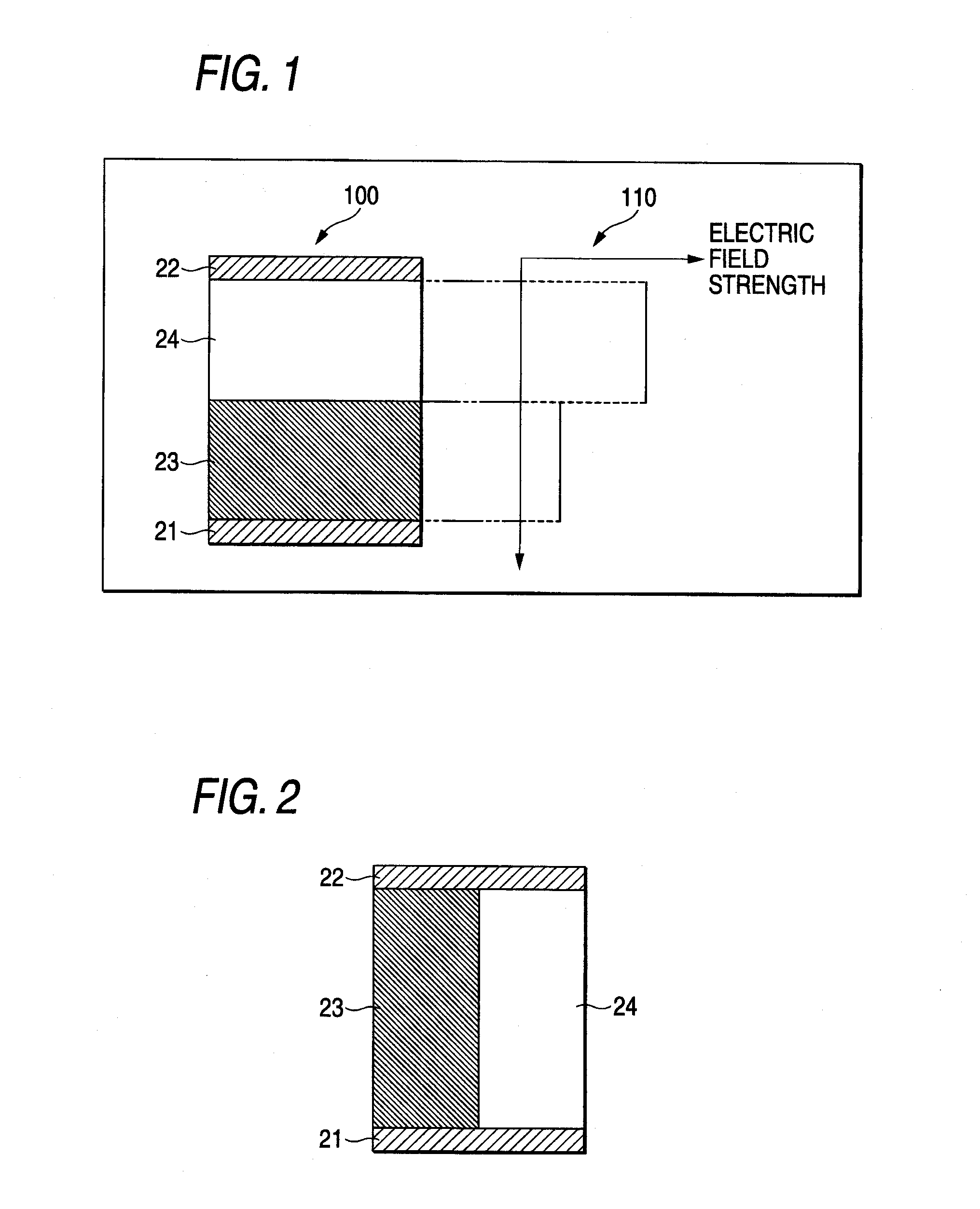

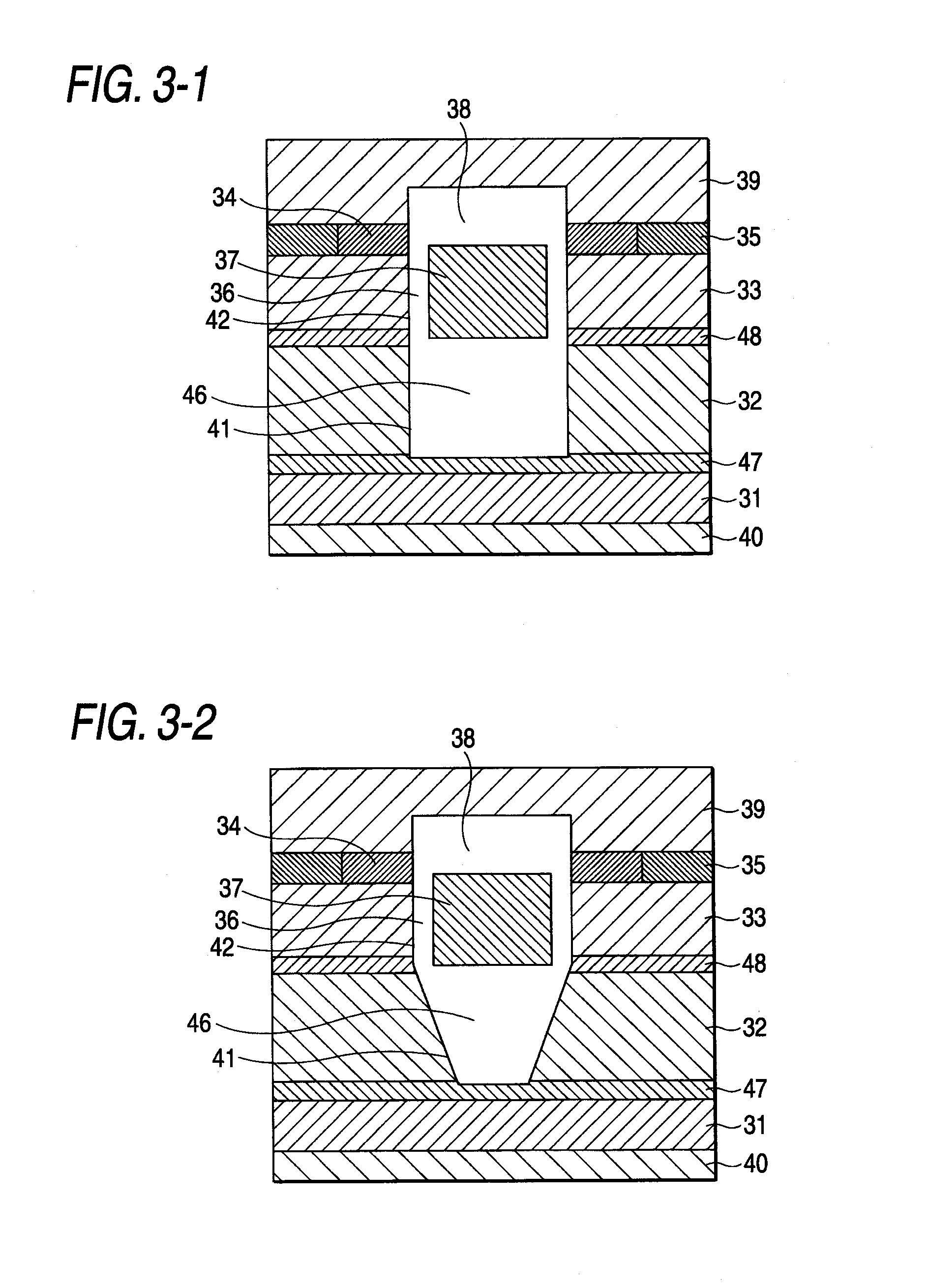

[0080] Normally, in a vertical MISFET, a highly doped layer known as a field stopping layer is provided on the drain side. After the drift layer is completely made depleted, the electric field strength abruptly reduces in the field stopping layer to almost zero. The section deeper than this, like becomes part of the drain electrode. Therefore, as shown in, for example, FIG. 3-1, in a semiconductor device according to the present invention, the depth of the trench 41 is configured so that the electric field strength therein becomes approximately zero, at least the insulation breakdown voltage on the semiconductor side. Moreover, in the section of the trench in the vicinity of a MIS channel 42, i.e., a section deeper than a gate electrode 37, an insulator 46 is kept buried. Such a structure enables realization of the electrical properties shown in FIG. 2.

[0081] Moreover, when the normal insulation breakdown electric field strength of the insulator 46 buried in a deep section in the tr...

second embodiment

[0197] Referring to FIG. 14, which shows an arrangement of a principal part of a trench MOSFET according to the present invention, as shown by the cross-sectional view 1400 the trench 41 is formed to penetrate through the field stopping layer 47 and reach a deeper section in the substrate 31. Moreover, as shown in the side cross sectional view 1410, the bottom surface side of the substrate 31 is further partly cut out (not shown) to reduce the on-state-resistance. Furthermore, from the part of the bottom surface having been cut out, there is formed a back trench 51 that is not parallel with the trench 41. By making the back trench 51 and the trench 41 cross each other, an opening is provided at the bottom surface of the trench 41. Through the opening, the inner wall surface of the trench 41 is continuously linked with the inner wall surface of the back trench 51. Thus, the inner wall surface of the trench 41 is connected to the bottom surface of the substrate 31 through the inner w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More