Array-Processed Stacked Semiconductor Packages

a technology of stacked semiconductors and array processing, which is applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of increasing the complexity of the product, the cost per functional unit should drop, and the increase of the functional complexity paralleled by the equivalent increase in the reliability of the product, so as to improve the strength of the package

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

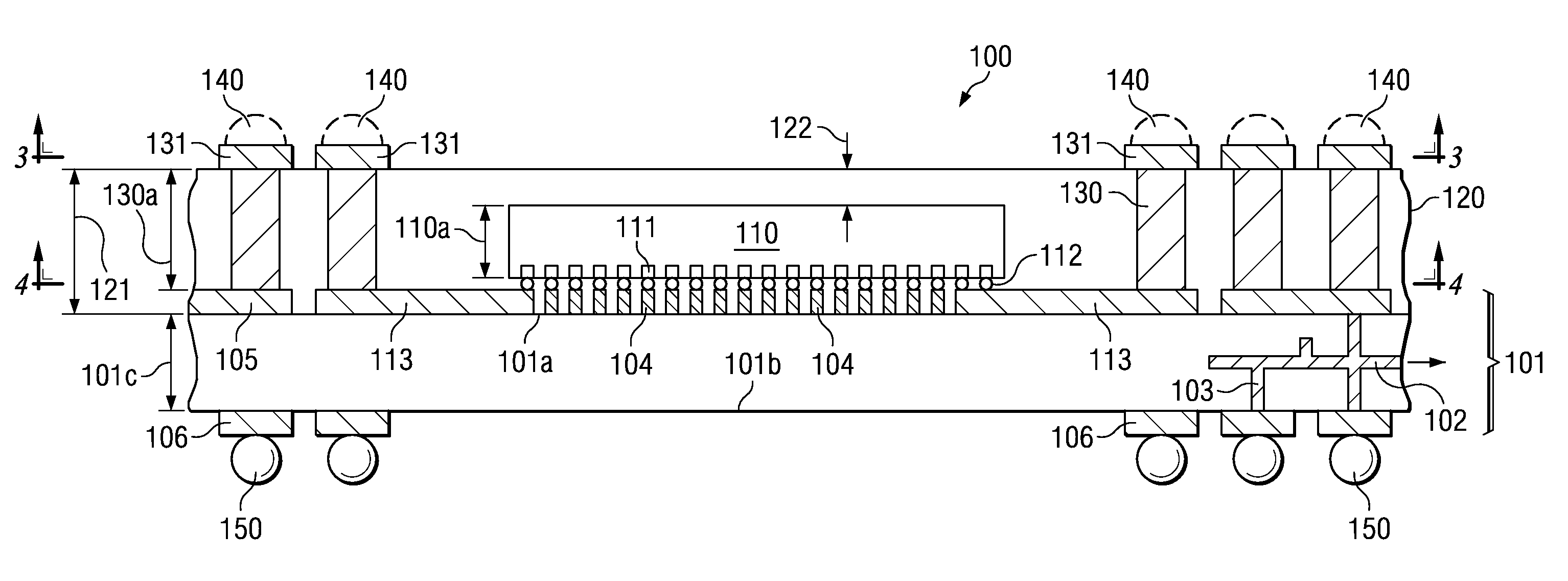

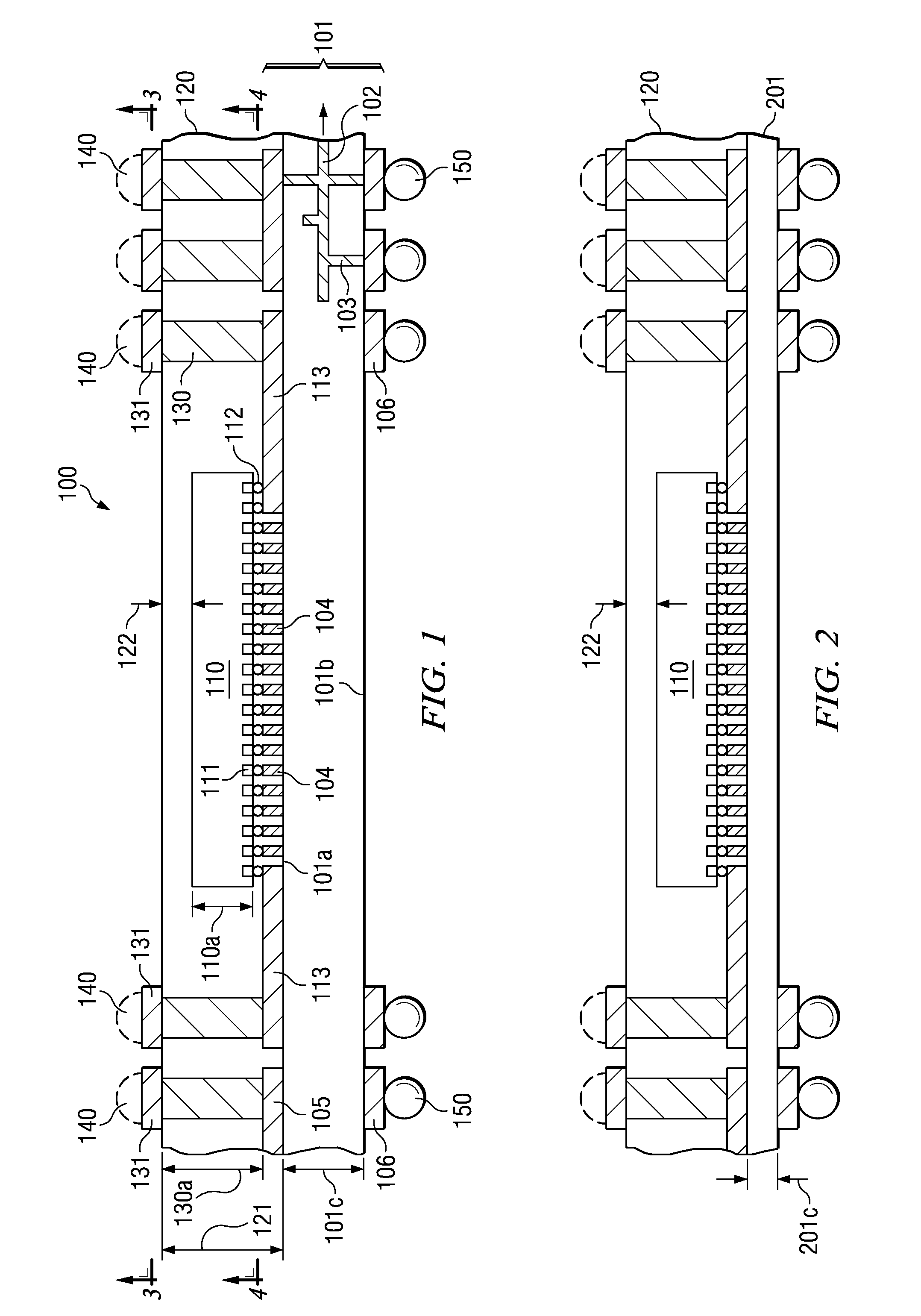

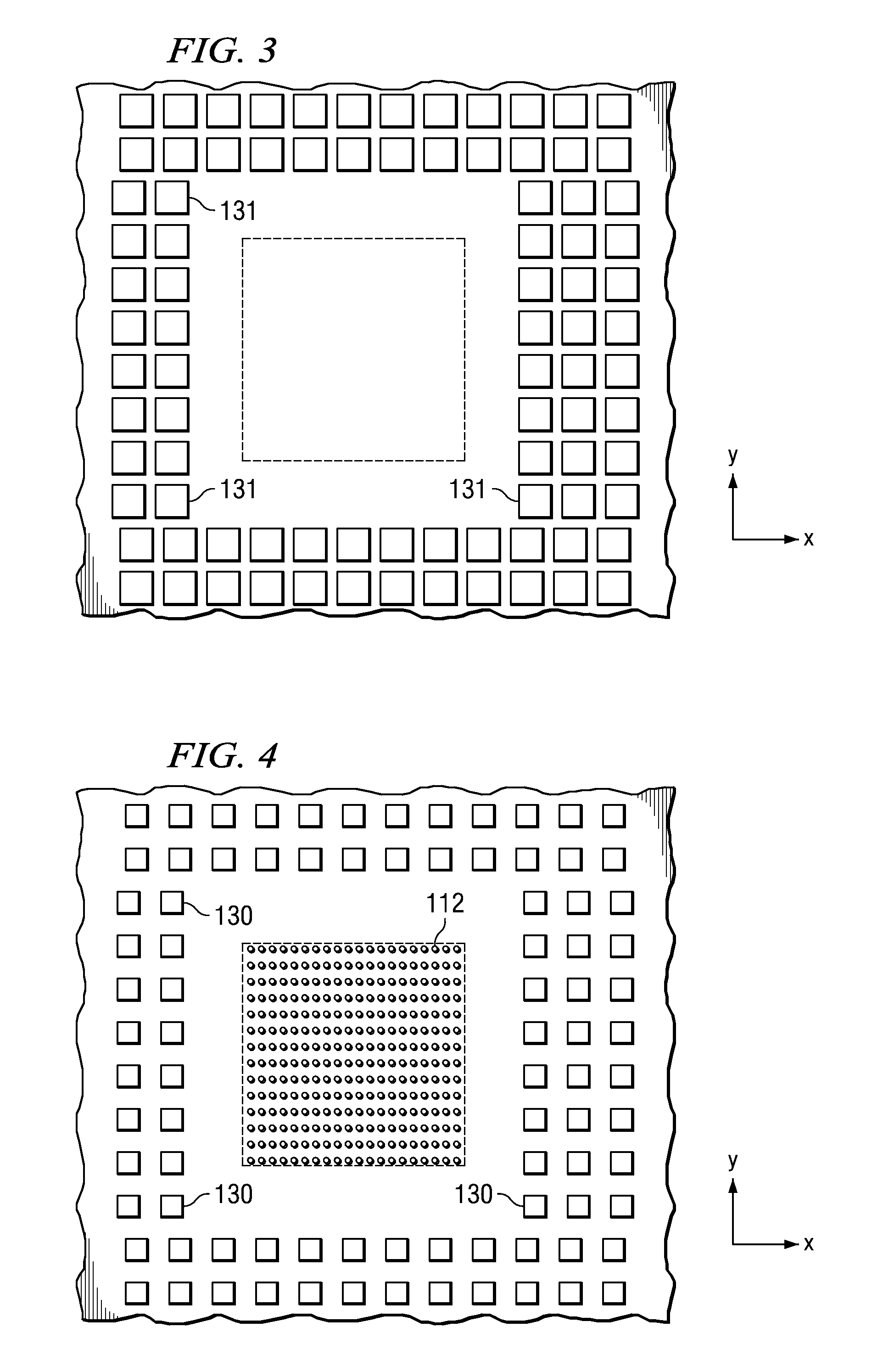

[0029]FIG. 1 illustrates a portion, generally designated 100, of an array shown more fully in FIG. 5. Actually it is, in FIG. 5, the first array of several arrays, which together form a semiconductor system. The first array consists of one or more assembly sites as depicted in FIG. 1; in FIG. 5, each array includes four assembly sites; arrays with considerably higher number of assembly sites can be manufactured. In addition, the sites may be arranged in x-direction as well as in y-direction; the number of sites may be different in x- and y-direction.

[0030]The assembly site depicted in FIG. 1 shows a substrate 101, which has a first surface 101a and a second surface 101b. The substrate is preferably made of a sheet-like insulating material such as polyimide- and / or epoxy-based compounds and has a thickness 101c in the range from about 10 to 1000 μm. Between surfaces 101a and 101b are layers 102 of conductive horizontal lines (preferably copper), and extending from surfaces 101a to su...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More