Method for measuring interface traps in thin gate oxide MOSFETs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023]The following description of the embodiment below is merely an example and is in no way intended to limit the invention or its application or uses. The present invention discloses a method for measuring interface traps in thin gate oxide MOSFET devices.

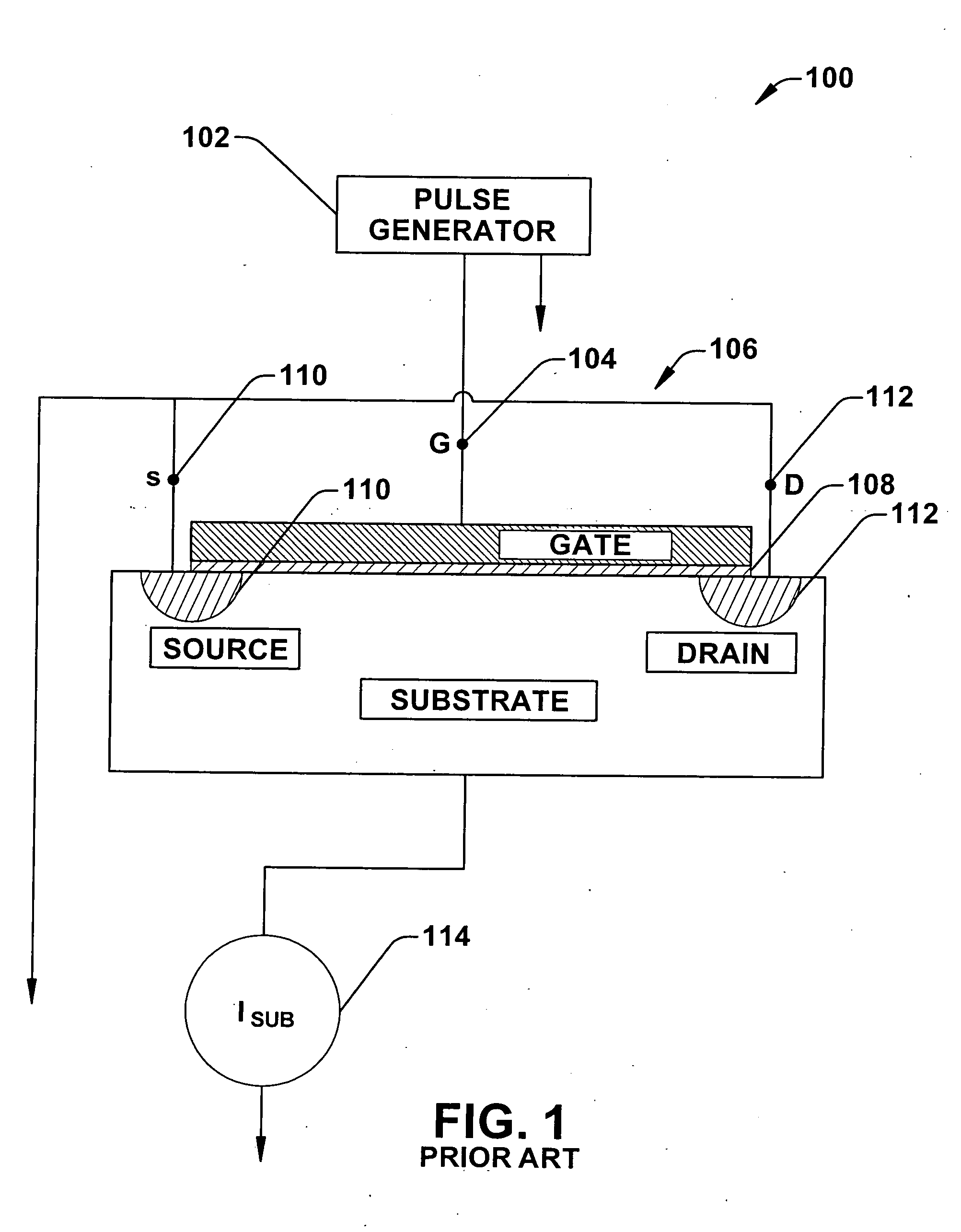

[0024]As semiconductor devices get smaller, hot carrier induced degradation of those devices is apt to occur. In order to make the MOSFET devices or Ultra-Large-Scale Integration (ULSI) components more reliable, it is critical to understand and quantify this degradation condition. The technique mentioned supra to accomplish this utilizes a charge pumping method, which is a measurement technique that can evaluate the substrate surface conditions at the Si—SiO2 interface, for example.

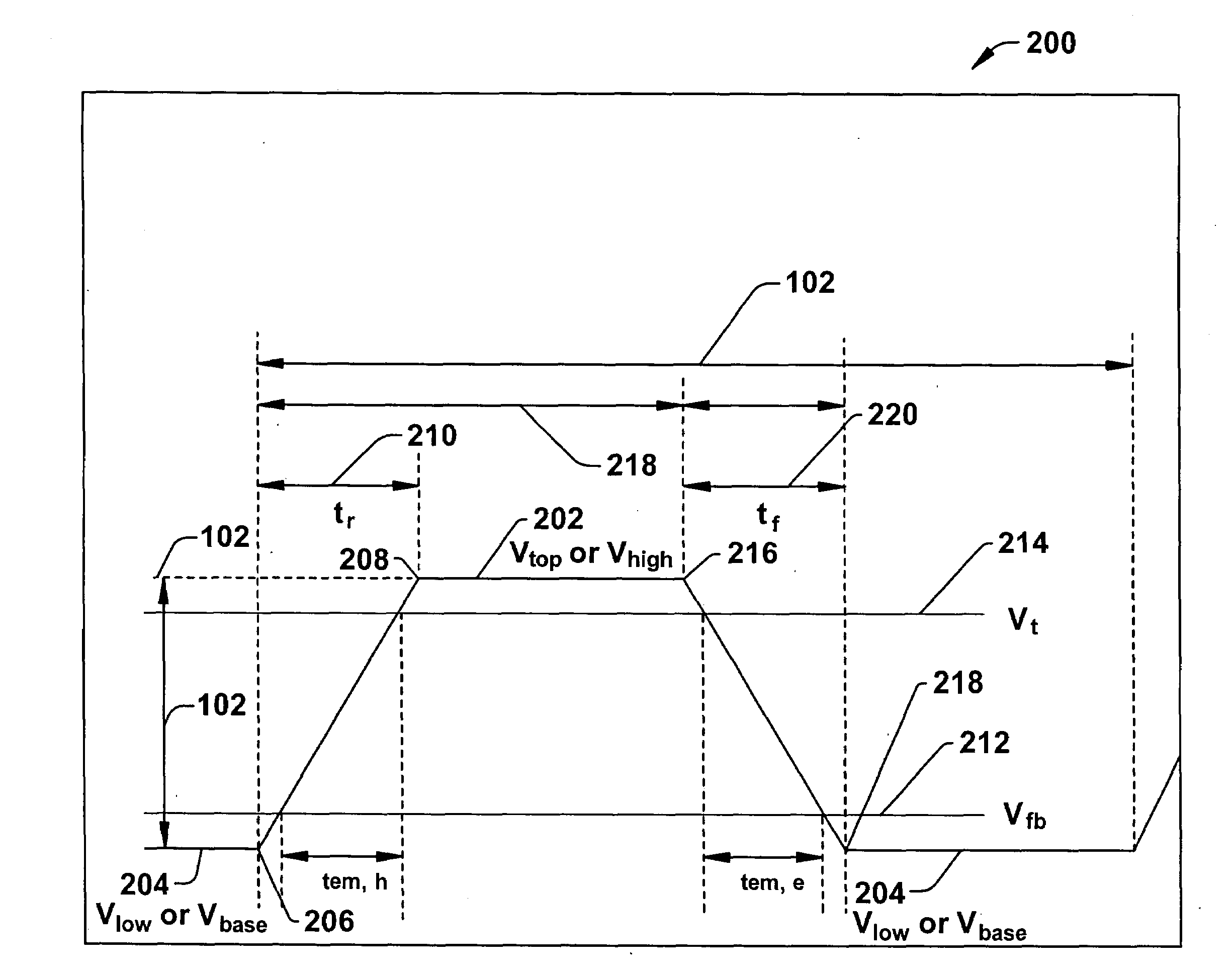

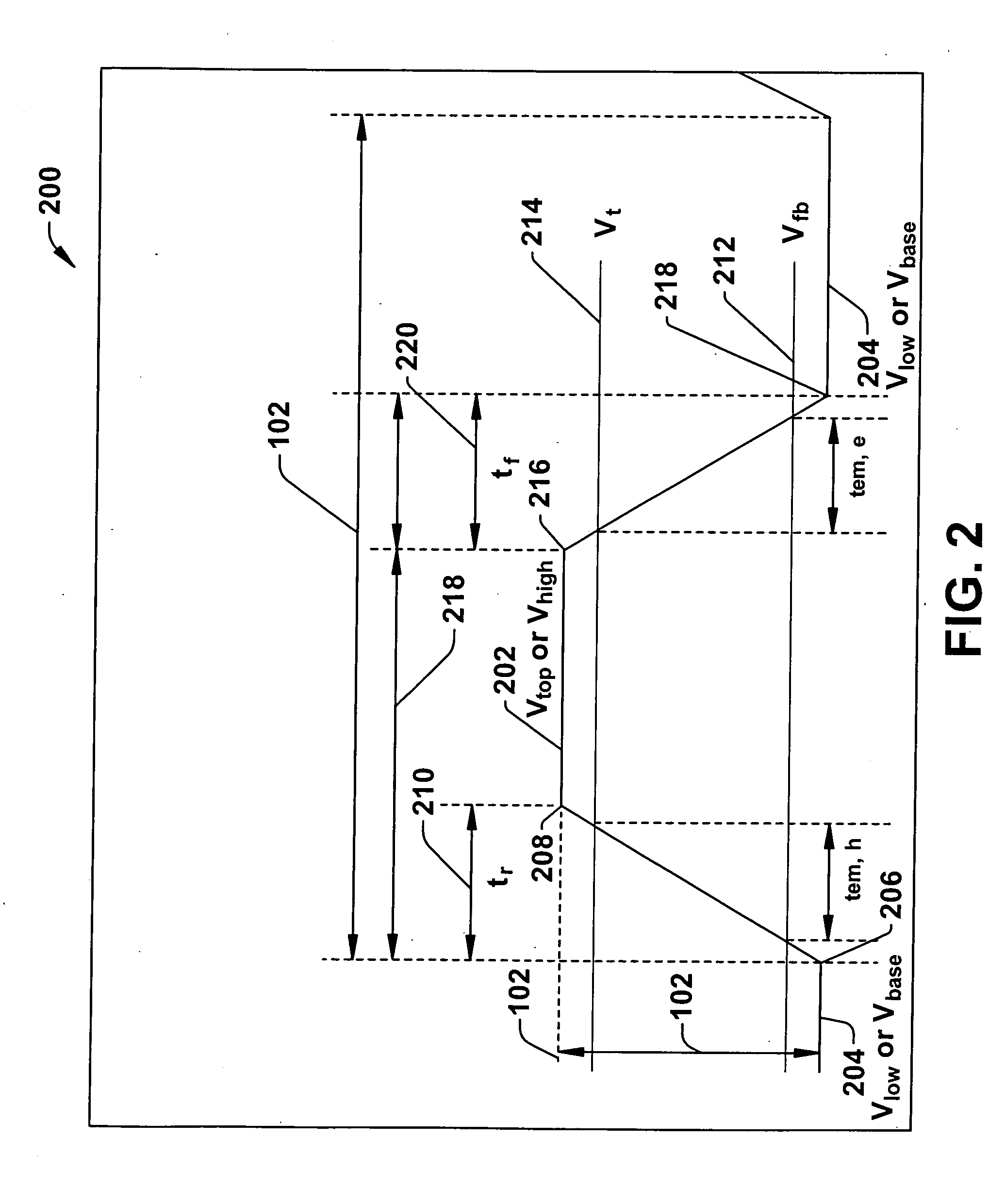

[0025]Turning now to the figures, FIG. 2 illustrates a trapezoidal wave pulse according to an aspect of the present invention. The interface traps between the Si and SiO2 layers that recombine with inversion or accumulation charges will constitute a n...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More