Application Specific Instruction Set Processor for Digital Radio Processor Receiving Chain Signal Processing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

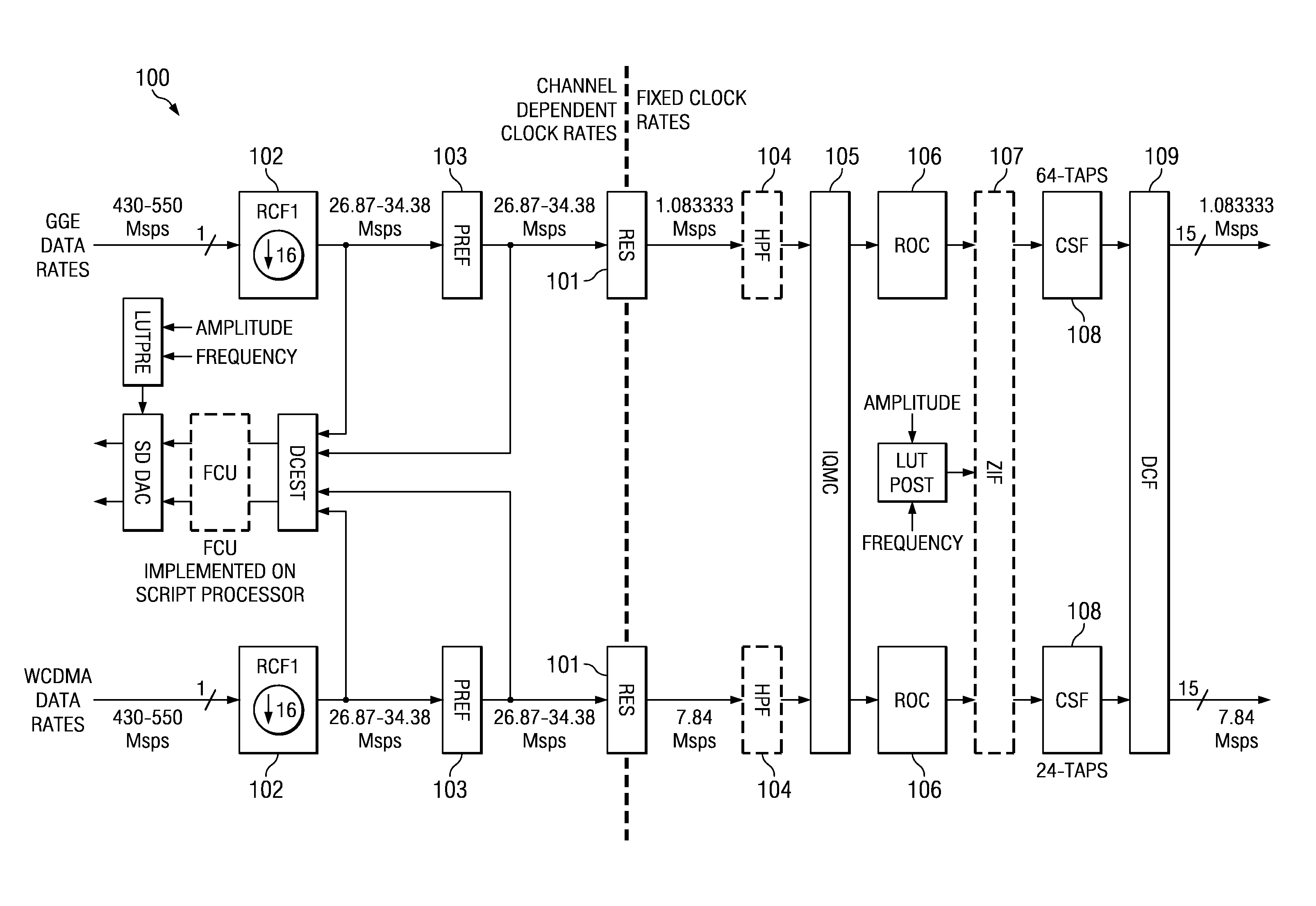

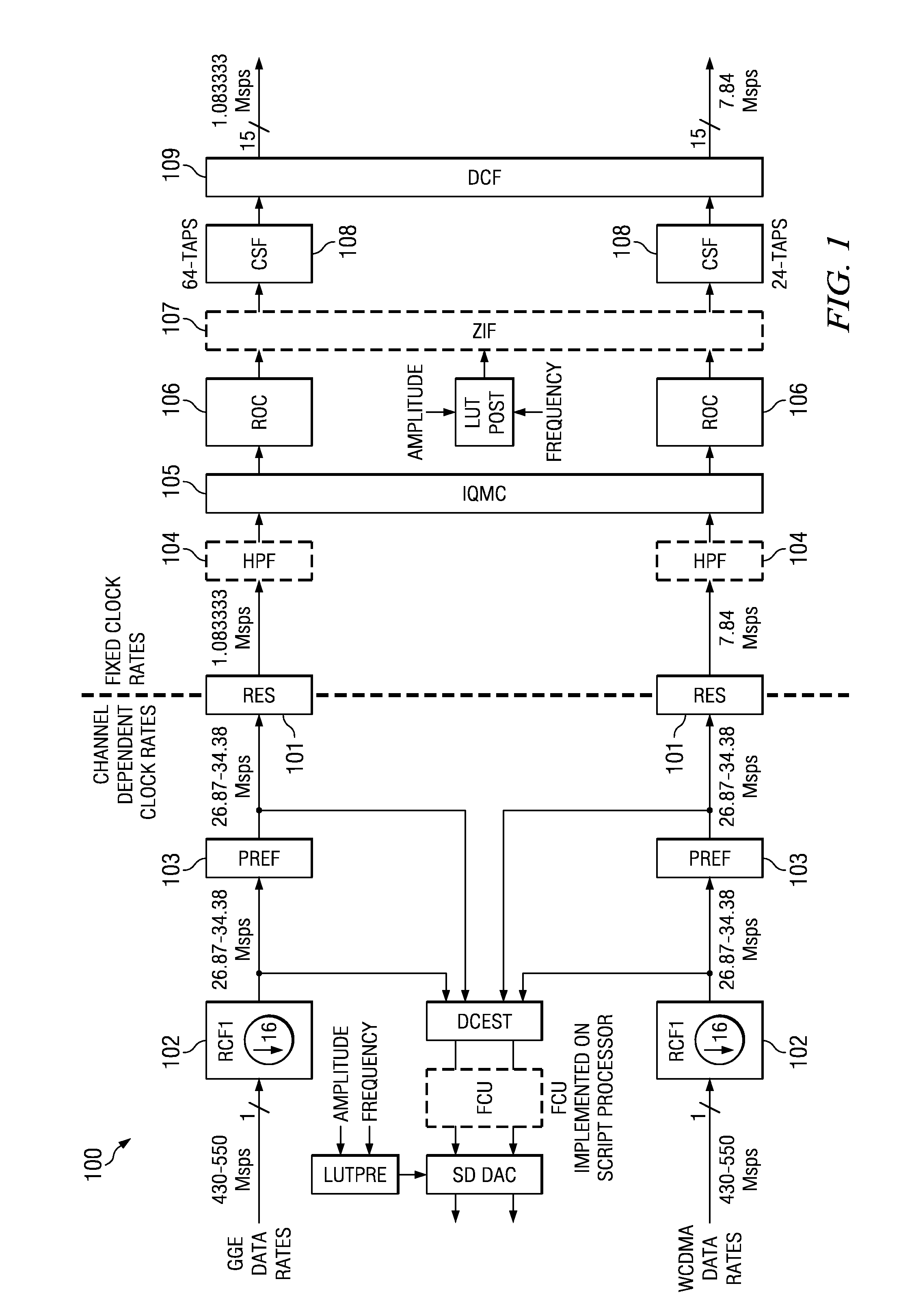

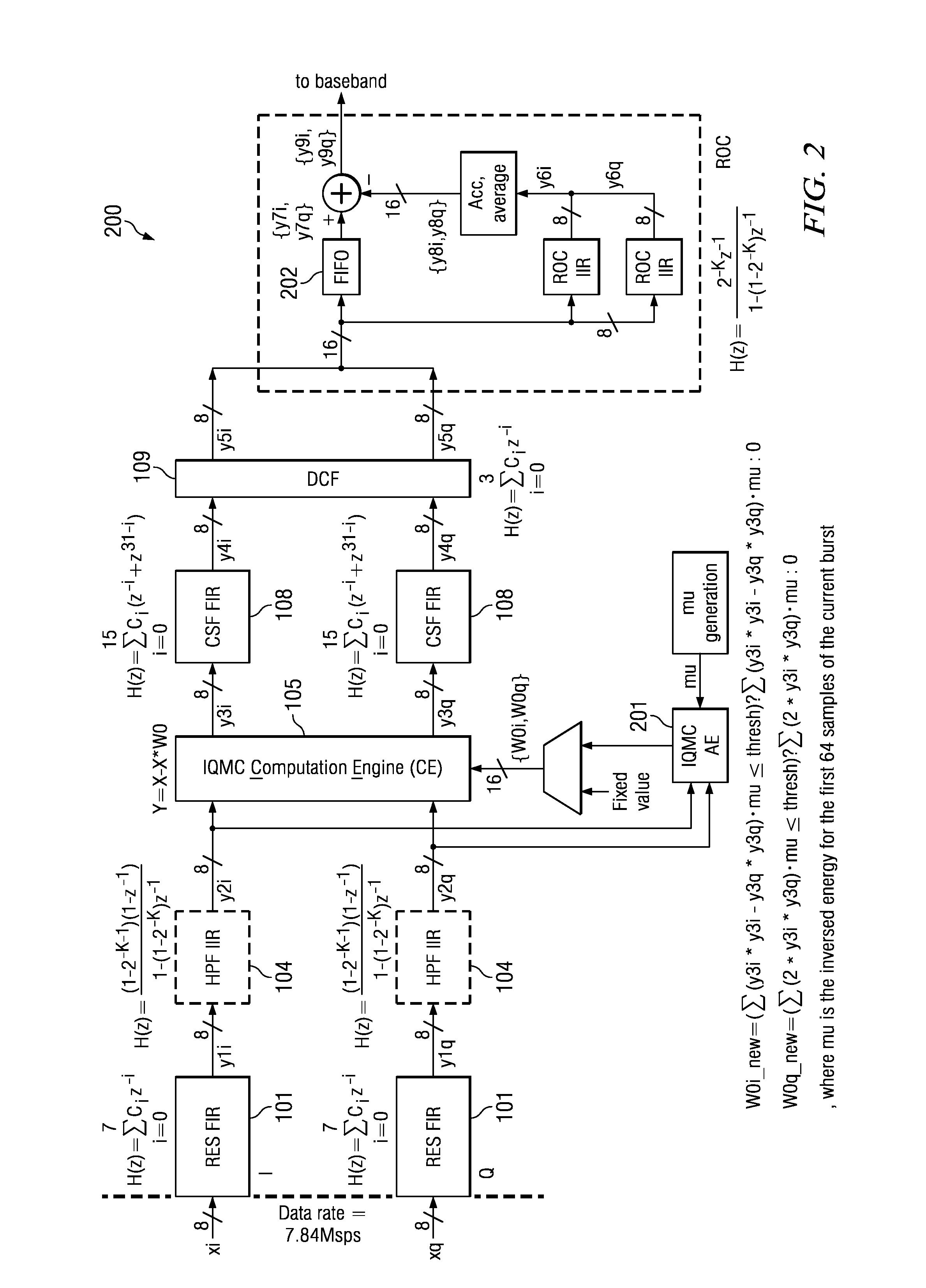

[0044]FIG. 2 illustrates the full FDRX for 8-bit WCDMA. FIG. 3 illustrates the full FDRX for 16-bit GGE. Both FIG. 2 and FIG. 3 include the additional two functional blocks: IQMC_AE (IQ Mismatch Adaptive Engine) 201 and 301; and ROC (Residual Offset Cancellation) 202 and 302. Since the data paths are highly reconfigurable, FIGS. 2 and 3 show one worst case in WCDMA and GGE where all blocks are present. The formula on each block shows the corresponding transfer function in the z-domain for is a digital filter (FIR or IIR). For IQMC_CE 105 and IQMC_AE 201 and 301, the algorithms are expressed in the time domain with complex computations.

[0045]Assume the input to the FDRX is a vector {xi, xq} and each component is represented by 8-bit signed integer. The output on each of the ten blocks is labeled on FIG. 2. The computation on each block is presented in the time domain in the following:

[0046](1) RES 101 performs the 8-tap decimation real FIR for both I and Q channels:

y1i[n]=∑i=07cixi[7...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More