Memory cell and manufacturing method

A memory unit cell and polysilicon technology, which is applied in semiconductor/solid-state device manufacturing, transistors, electrical components, etc., can solve the problems of excessive component size and insufficient charge storage period, and achieve the effect of size reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0072] In order to further explain the technical means and effects of the present invention to achieve the intended purpose of the invention, below in conjunction with the accompanying drawings and preferred embodiments, the specific implementation, structure, manufacturing method, steps, Features and their functions are described in detail below.

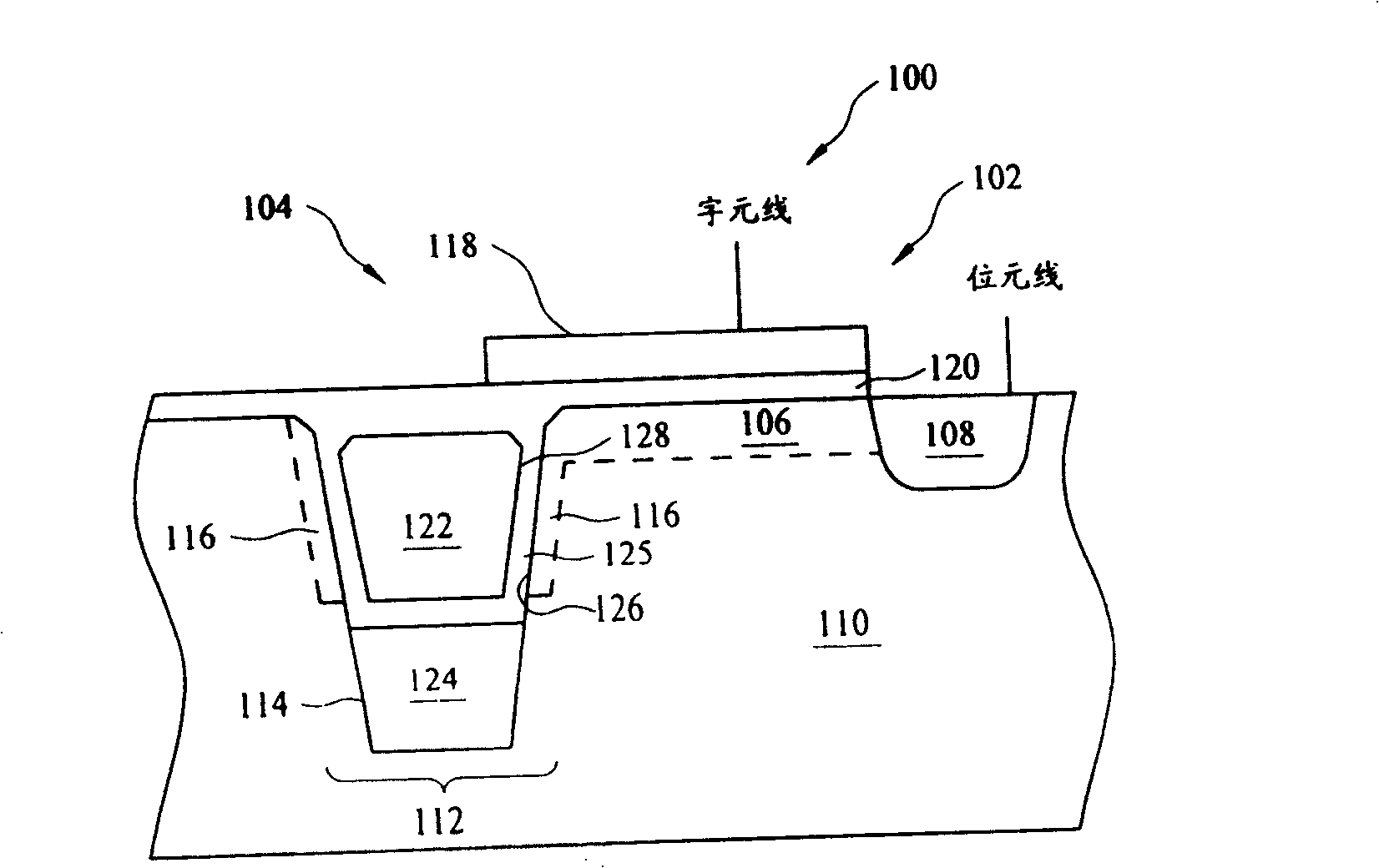

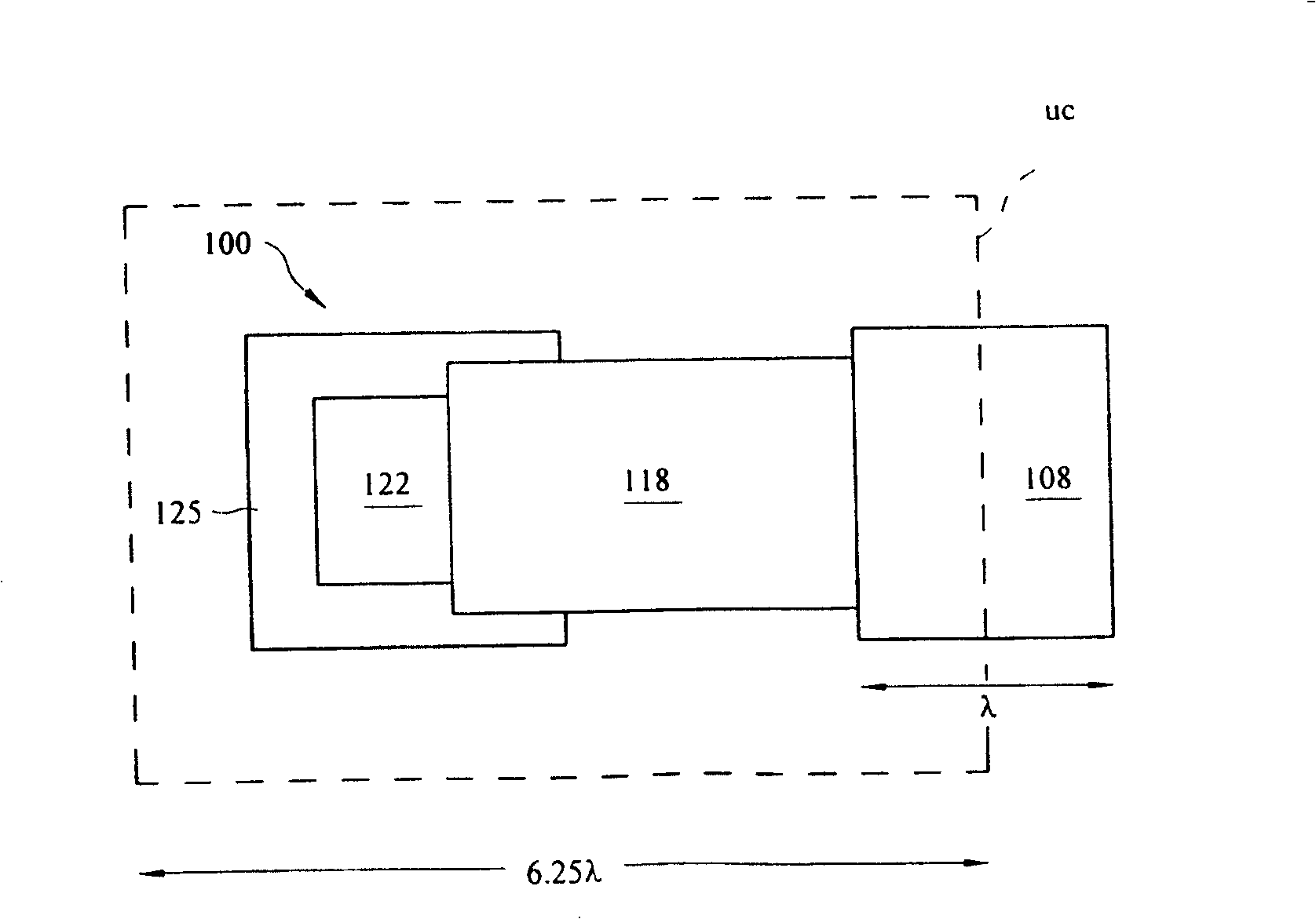

[0073] see figure 1Shown is a cross-sectional view of a DRAM unit cell 100 according to the present invention. The DRAM unit cell 100 mainly includes an NMOS switching transistor 102 and a storage region 104. The switching transistor 102 is provided with a doped n-type channel 106 on a p-type substrate 110 (for example, a p-type silicon wafer having a crystallographic orientation) and heavy Doping n + Drain junction 108 . The switch transistor 102 also includes n + The polysilicon gate structure 118 and the gate oxide layer 120, the source of the transistor 110 are disposed in the storage region 104, as described below.

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More