Matrix multiplication parallel computing system based on multi-FPGA

A matrix multiplication and parallel computing technology, applied in the field of FPGA technology and parallel computing, can solve the problems of difficult to guarantee system electromagnetic compatibility, deterioration of signal integrity, increase of power consumption, etc., to achieve improved computing performance, low hardware resource requirements, The effect of low communication overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

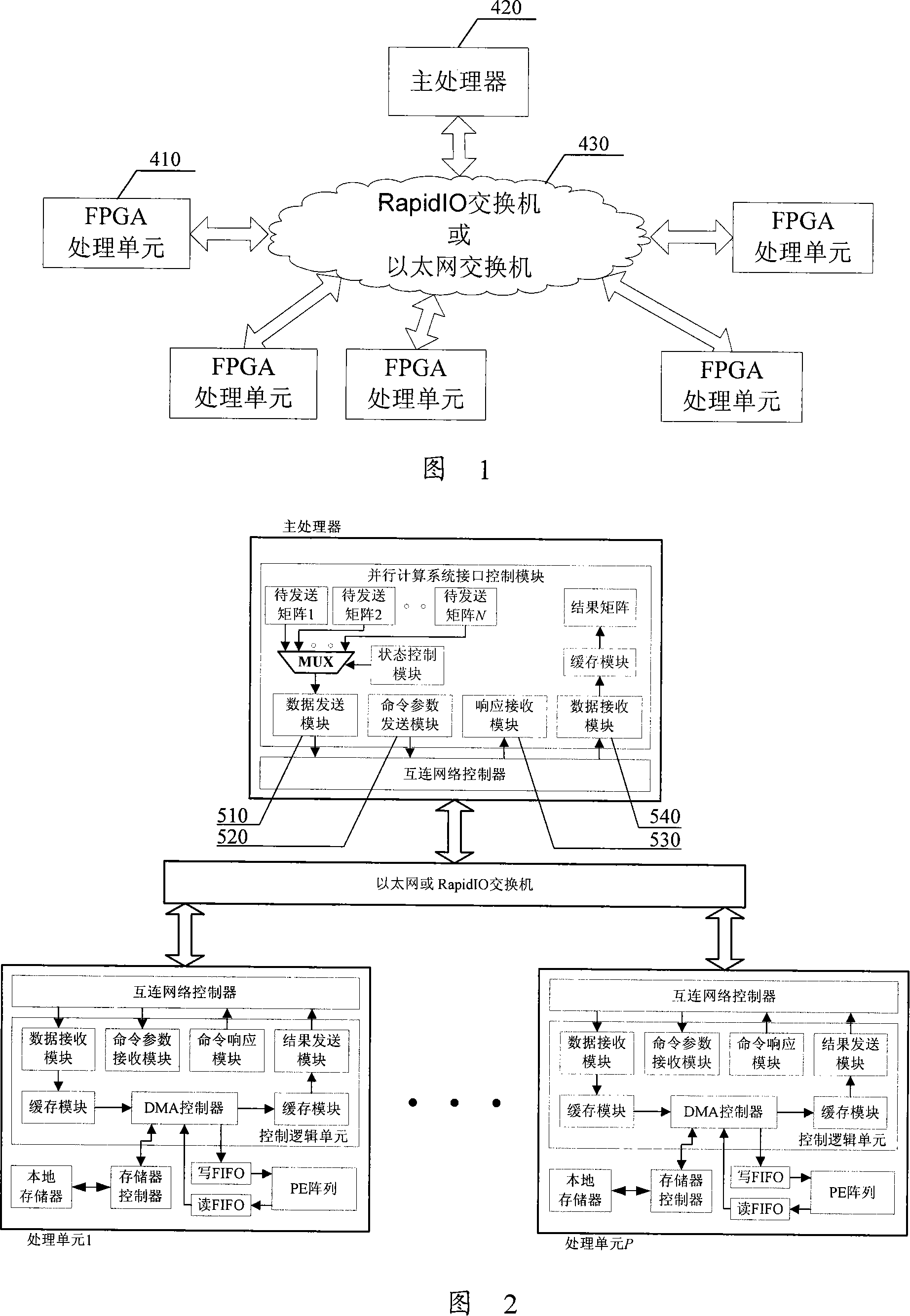

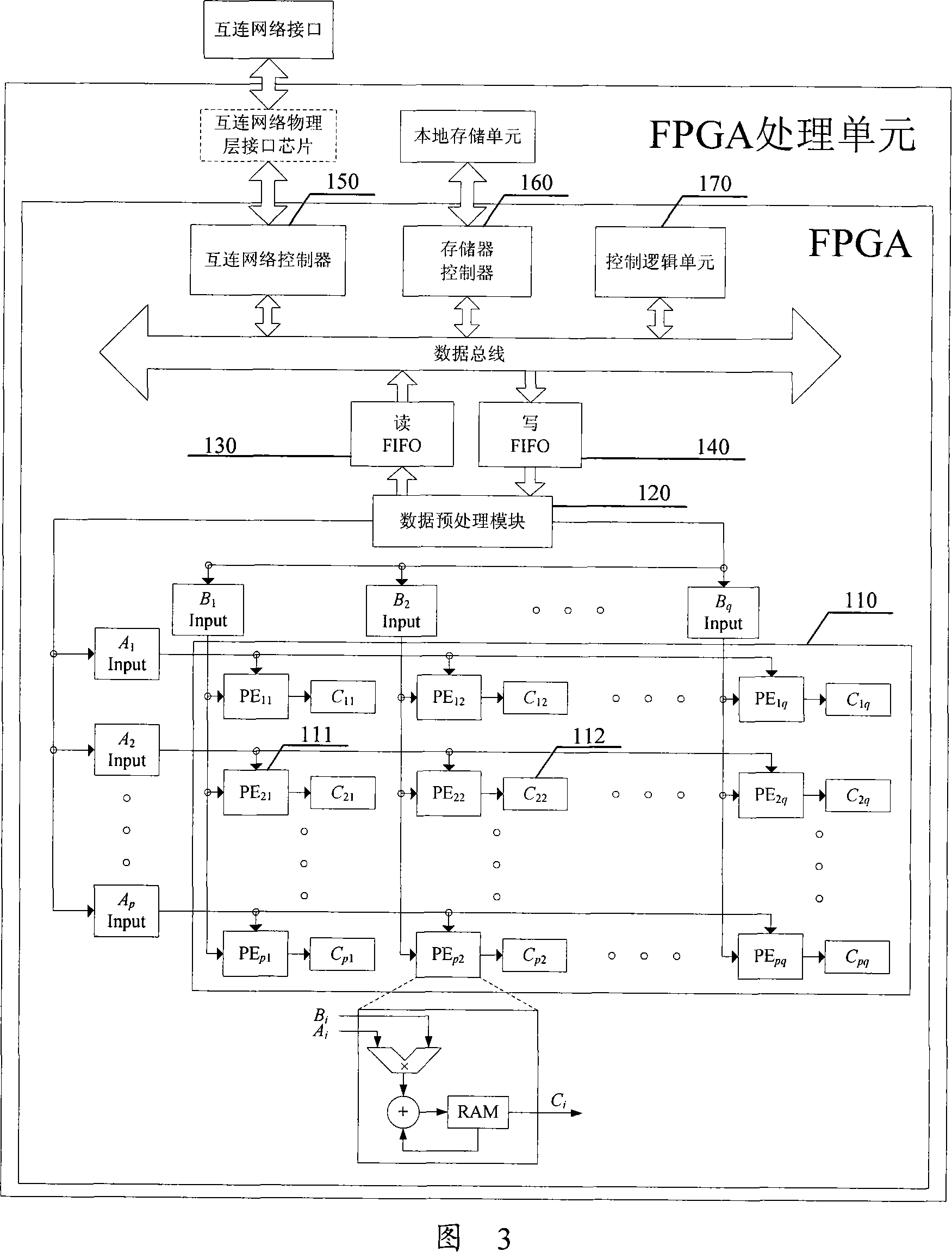

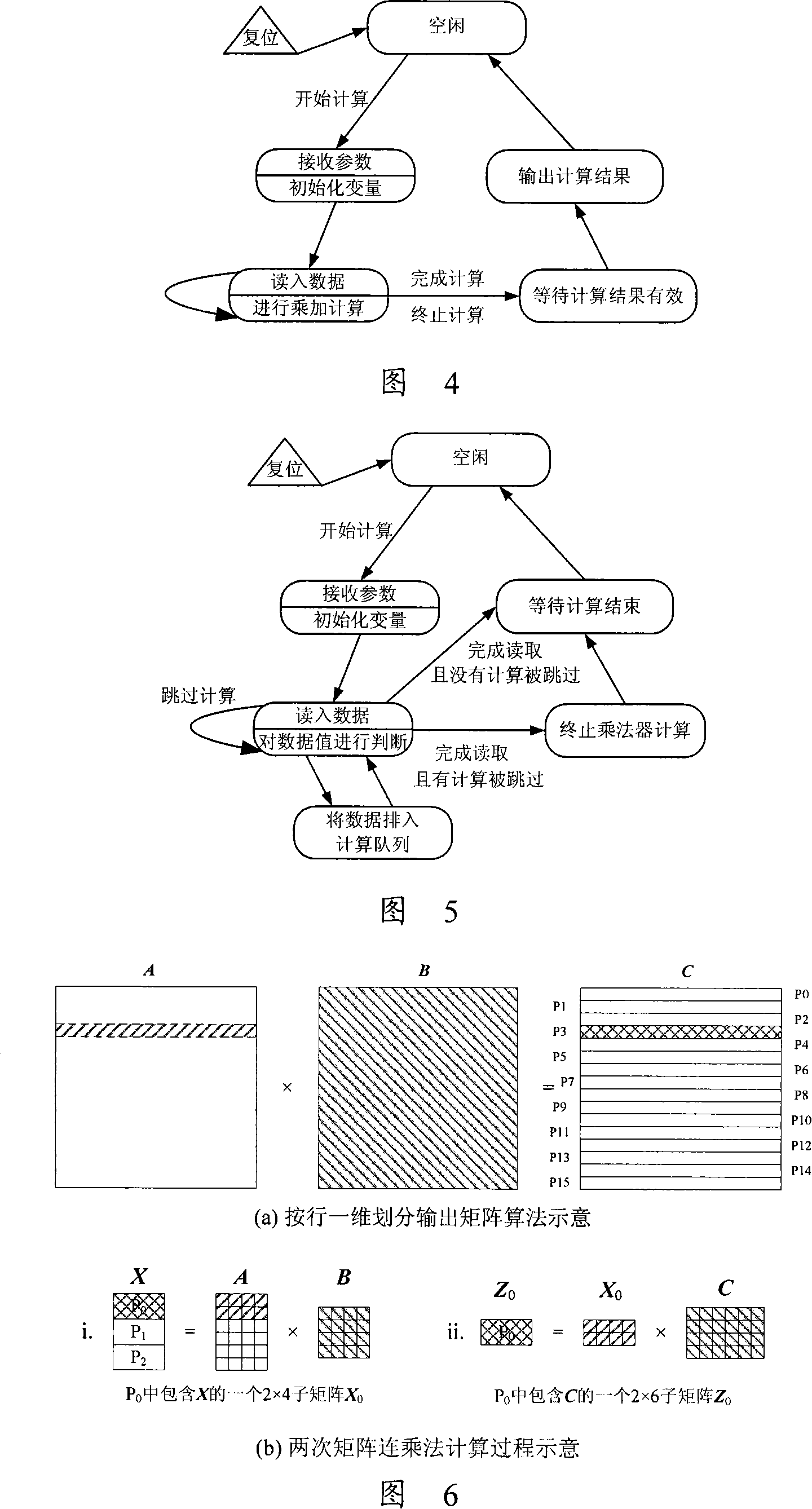

[0029] As shown in Figures 1 and 2, a matrix multiplication parallel computing system based on multi-FPGA and adopting a master-slave distributed structure uses an embedded processor as the main processor 420, and adopts Ethernet or RapidIO interconnection technology. The interconnection topology constitutes a master-slave distributed multi-FPGA matrix multiplication parallel computing system. The interconnection technology of Ethernet and RapidIO supports the multicast transmission mode. When multiple processing units 410 need the same data, the main processor 420 uses the multicast transmission mode through the Ethernet switch or the RapidIO switch 430 to send the data to all these processing units. Compared with other point-to-point interconnect technologies, such as PCI-e, the system has lower communication overhead.

[0030] The main processor 420 includes a data sending module 510 , a command sending module 520 , a response receiving module 530 and a data receiving modu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More