Wafer packaging construction with array connecting pad and method of manufacturing the same

A chip packaging and array technology, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of forming antenna effect, affecting product reliability, general products and methods without suitable structures and methods, etc. Achieve the effect of avoiding scratches or wear, improving anti-rust effect, and avoiding antenna effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment

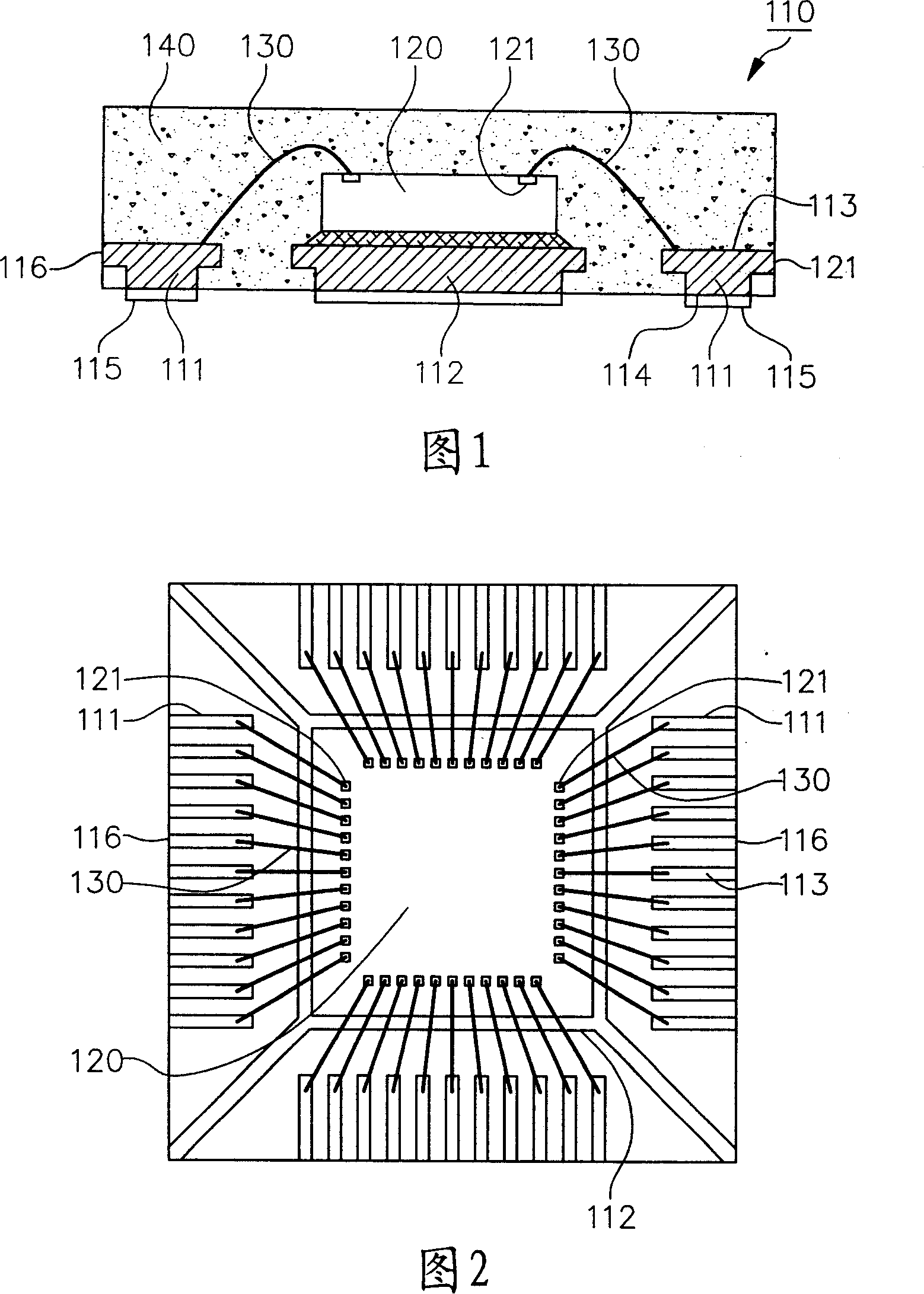

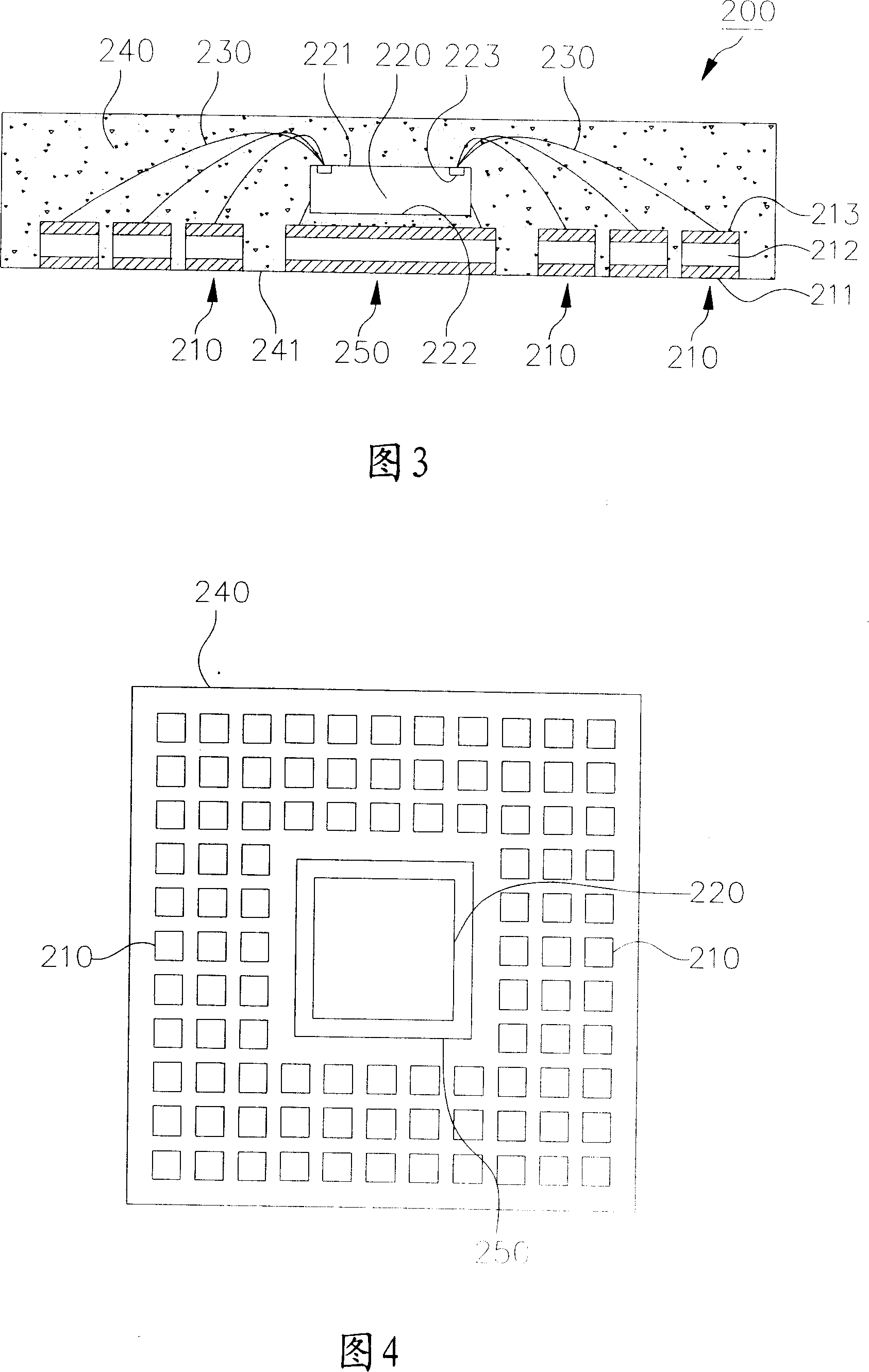

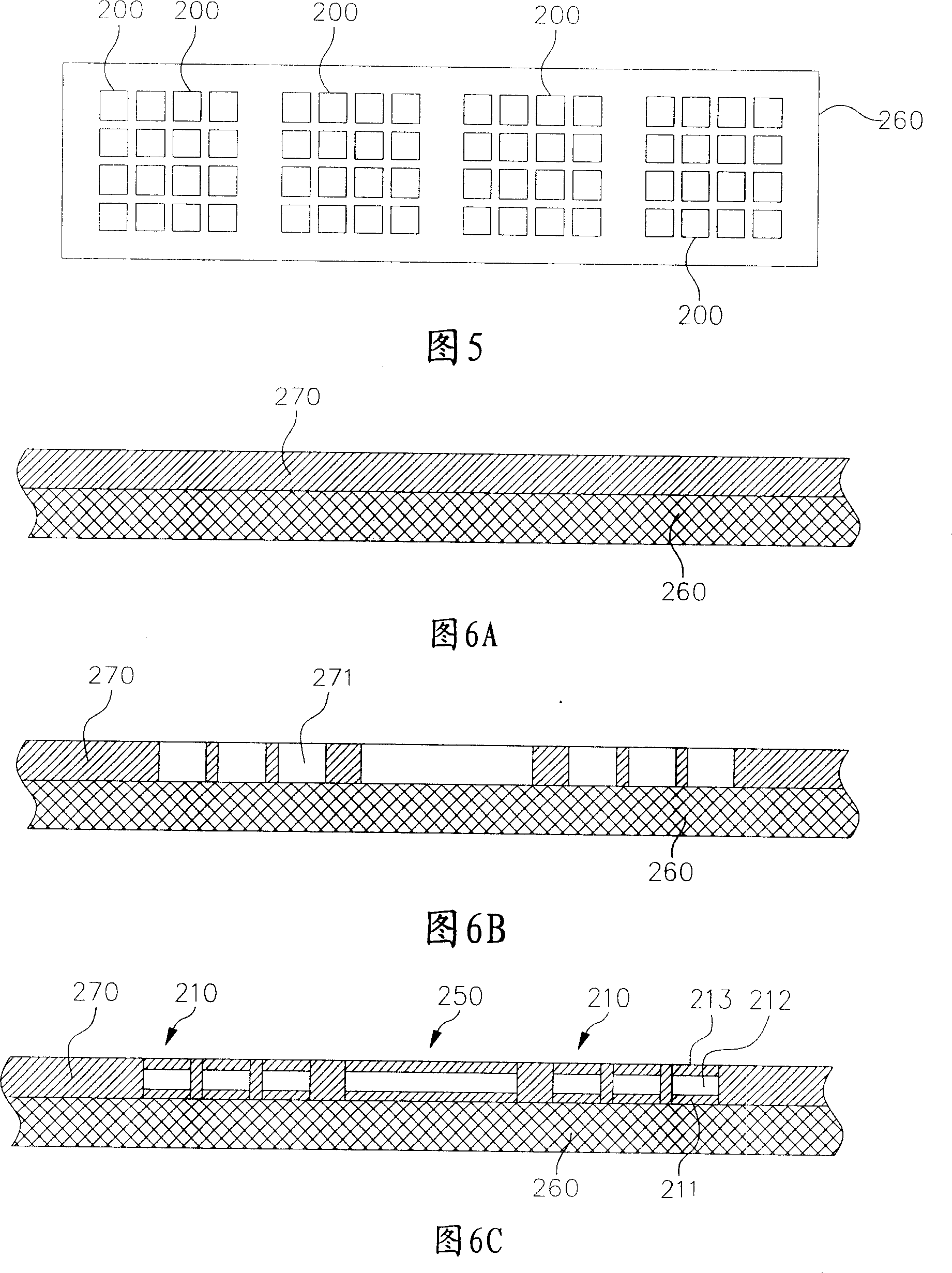

[0069] Please refer to FIG. 3 and FIG. 4. FIG. 3 is a schematic cross-sectional view of a chip package structure with array pads according to a first embodiment of the present invention. FIG. 4 is a chip and wire bonding structure of the chip package structure Schematic of the top surface of the pad. In the first embodiment of the present invention, the chip package structure 200 with array pads mainly includes a plurality of bonding pads 210 , a chip 220 , a plurality of bonding wires 230 and an encapsulant 240 .

[0070] As shown in FIG. 4 , the above-mentioned bonding pads 210 are arranged in an array, and can be arranged in any number of rows, which are formed by electroforming technology (details will be described later). Moreover, as shown in FIG. 3 , the bonding pads 210 are formed on the same plane. Each bonding pad 210 includes a lower bonding layer 211 , an electroformed core 212 and an upper bonding layer 213 , wherein:

[0071] The electroforming core 212 is made...

no. 3 Embodiment

[0093] Please refer to FIG. 9 , which is a schematic cross-sectional view of another chip package structure with array pads according to the third embodiment of the present invention. The present invention can be further applied to different chip package structures of non-wire bonding type. Another chip package structure 400 with array pads disclosed in the third embodiment mainly includes a plurality of pads 410, a chip 420 and A letter of colloid 430.

[0094] The pads 410 are formed in an array on the same plane. Each pad 410 includes a lower bonding layer 411 and an electroforming core 412, and may further include an upper bonding layer 413, so that the electroforming core 412 is located on the lower bonding layer. layer 411 and the upper bonding layer 413 .

[0095] The electroforming cores 412 are made of copper, which has the advantages of good thermal conductivity and easy electroforming. And the side surfaces 412A of the electroformed cores 412 are not covered by th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More