Ground wire layout graph for reducing microwave single-sheet integrated circuit standing wave ratio

An integrated circuit and microwave monolithic technology, applied to circuits, printed circuits, waveguides, etc., to facilitate installation and adjustment, improve success rate, and reduce process errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

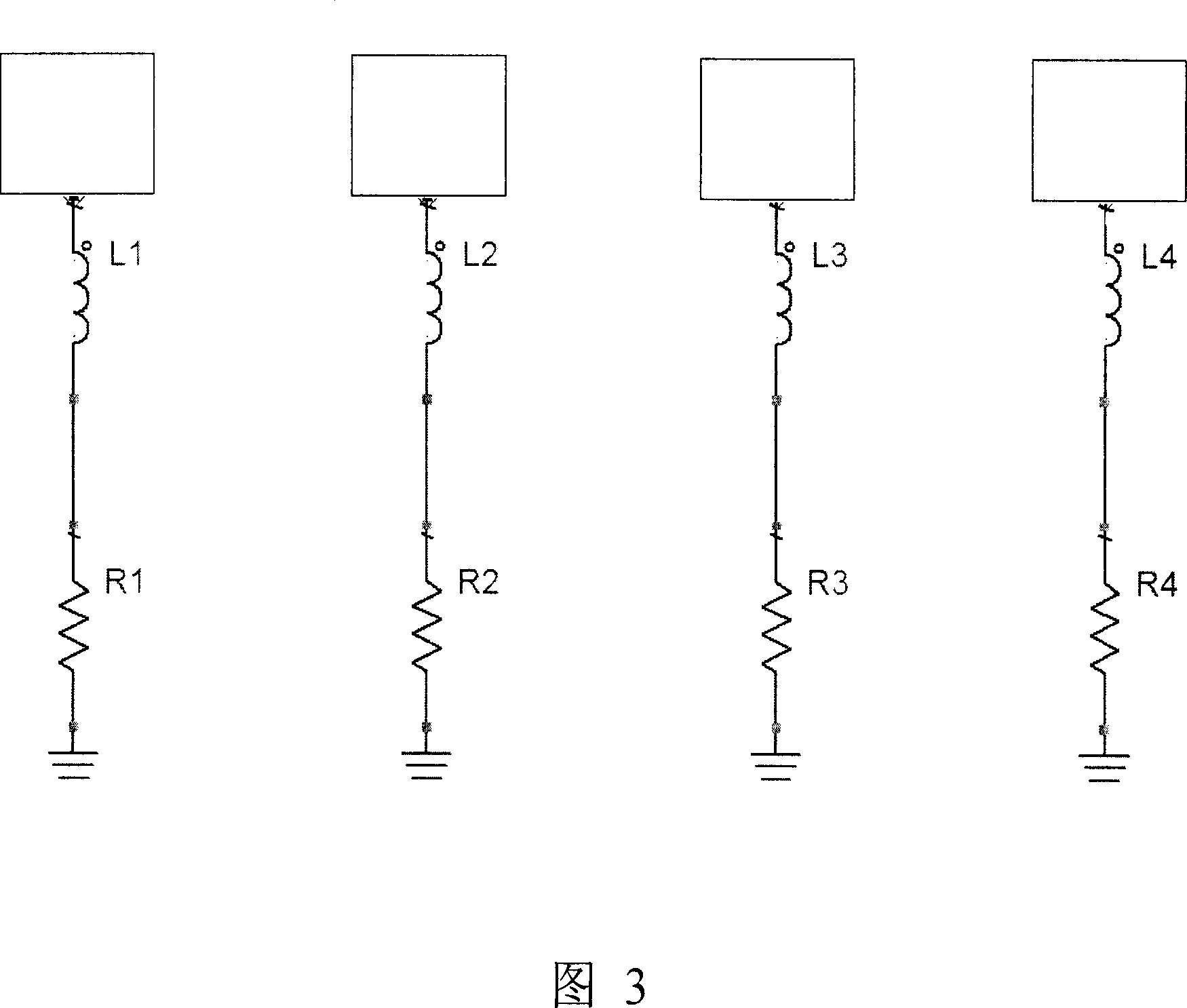

[0041] As shown in FIG. 5, FIG. 5 is a ground wire layout pattern for reducing the MMIC standing wave ratio according to a preferred embodiment of the present invention. Figure 5 shows the ground layout of the input part and the output part.

[0042] The graphic unit is located on the same layer of the printed circuit board or layout. The printed circuit board does not use a solder resist layer and maintains the gold surface. This is because the skin effect of the current in the high-frequency circuit requires a smooth gold surface. If a solder mask is added, the gold surface will not have a polishing process, so the solder mask is not used. The width of the signal microstrip is determined by the center frequency point. The distance between the signal microstrip and the ground plane is calculated according to the coplanar waveguide formula. The distance between the device under test (DUT) is calculated by the microstrip line, and the value is 2-3 times the width of the microstrip ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More