Etch stop layer and its forming method

A technology of etching barrier layer and manufacturing method, which is applied in the direction of electrical components, electrical solid devices, semiconductor/solid device manufacturing, etc., and can solve problems affecting packaging process, device reliability, interlayer dielectric layer and interlayer dielectric Layer interface adhesion and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

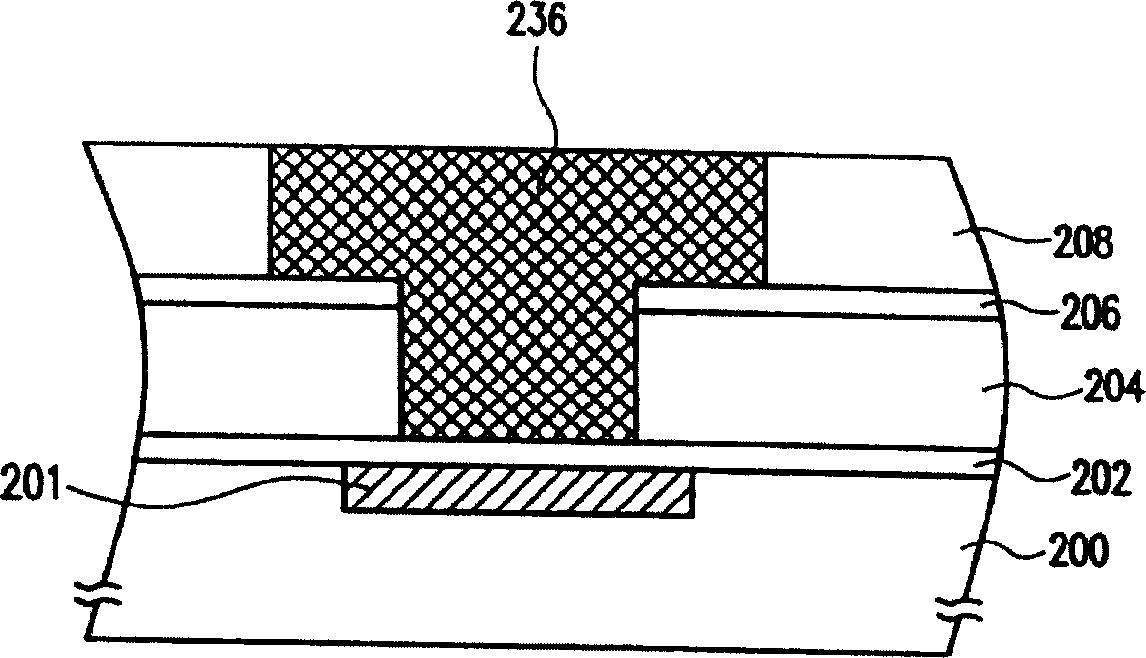

[0039] Figure 4A to Figure 4D It is a schematic diagram of the second embodiment of forming an etching stopper layer on a semiconductor substrate by using the preparation method of the present invention. The specific embodiment of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0040] Such as Figure 4A As shown, a semiconductor substrate 31 with a conductive layer 32 is provided, and the semiconductor substrate 31 has semiconductor devices and wiring layers. To simplify the illustration, only a flat substrate with a conductive layer is shown here. Form the first etch barrier layer 41 on the semiconductor substrate 31 and the conductive layer 32, the first etch barrier layer 41 is silicon nitride, the stress range of the silicon nitride is -1600 to -2000MPa, the nitride The stress of silicon is compressive stress.

[0041] Next, if Figure 4B As shown, a first etch stop layer 41 is formed on a semiconductor substrat...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Stress | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More