Punch through effect enhanced type silicon photo transistor

A punch-through effect, enhanced technology, applied in circuits, electrical components, semiconductor devices, etc., can solve the problems of low SNR, low gain, large dark current, etc., to improve photoelectric conversion gain, improve photoelectric conversion gain, high photoelectric conversion gain effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

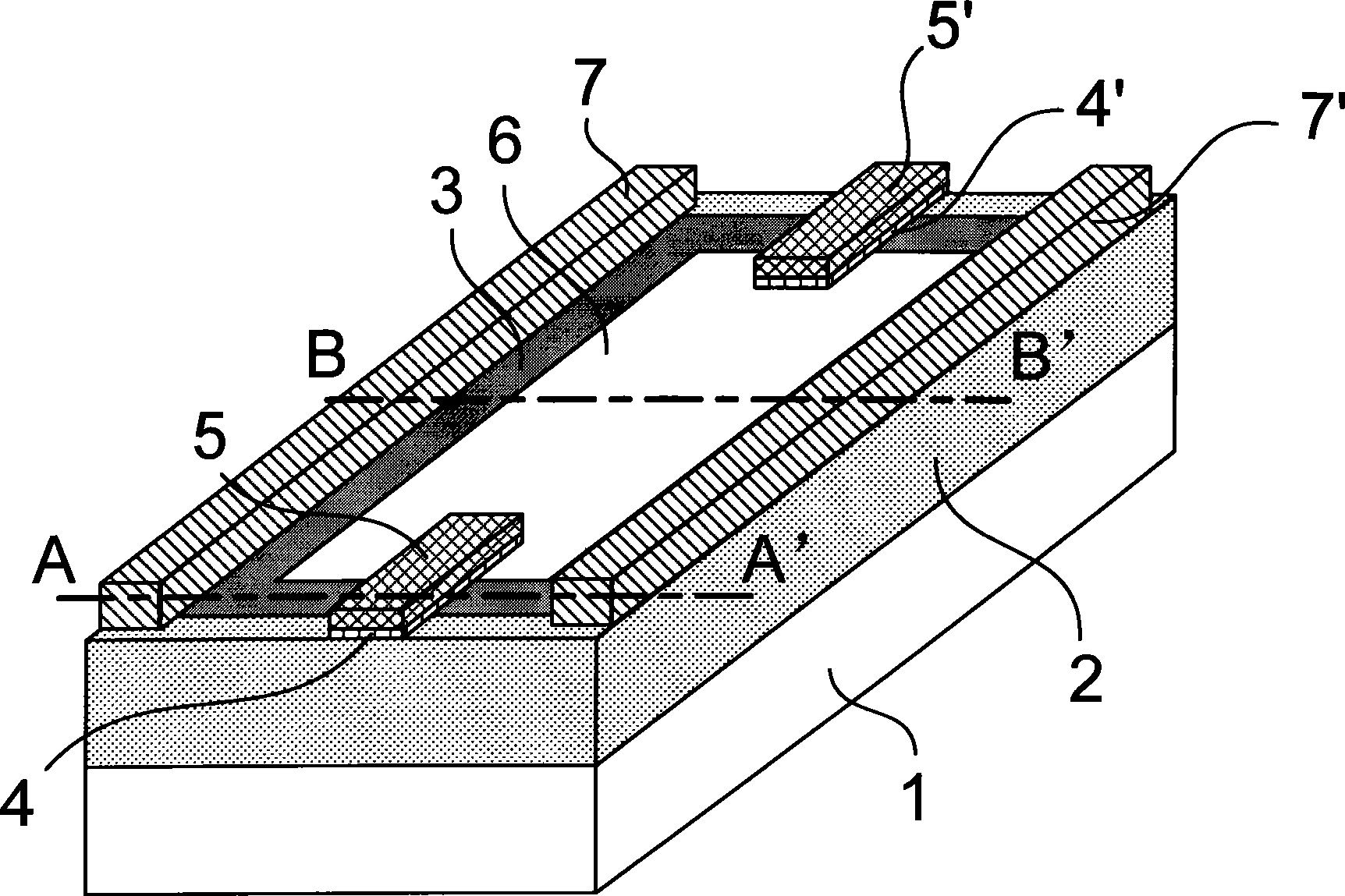

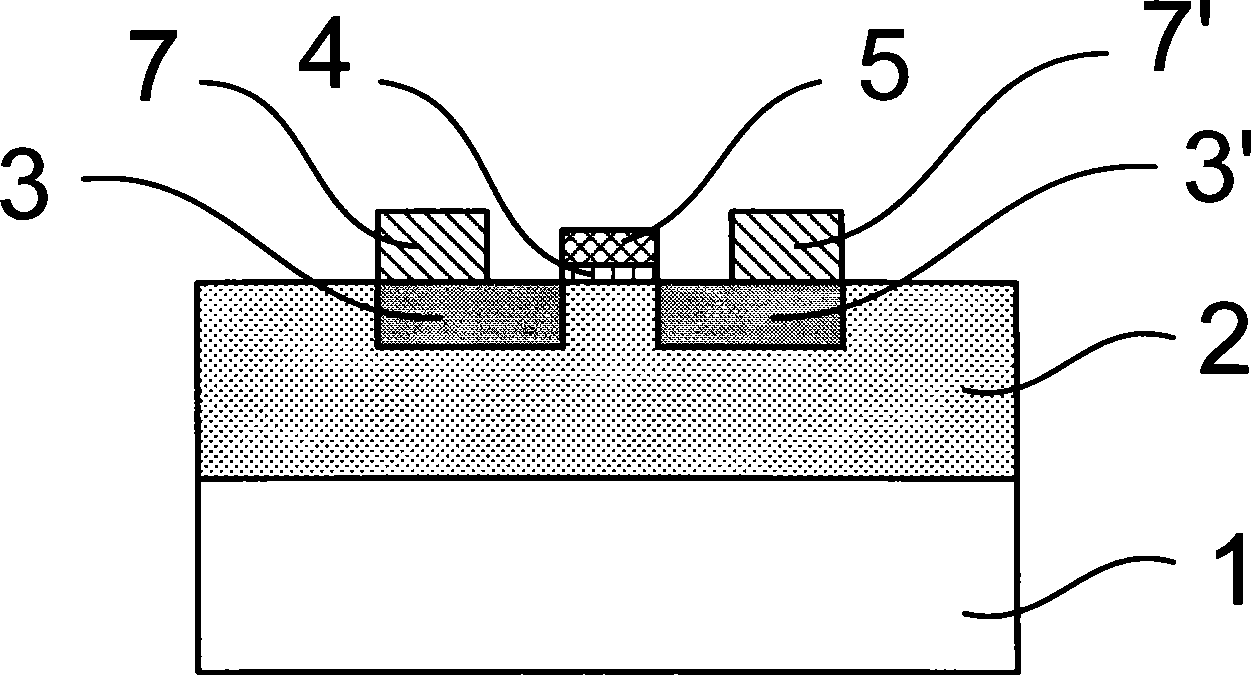

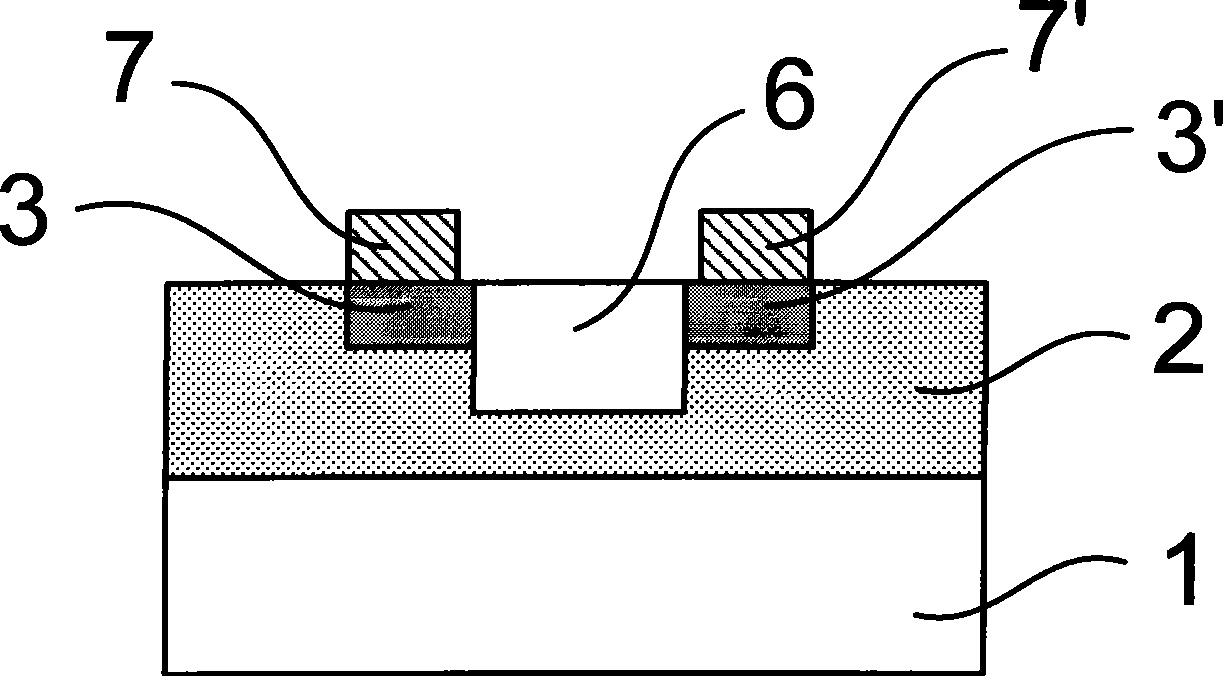

[0053] Since the punch-through effect enhanced silicon phototransistor of the present invention is fully compatible with standard CMOS technology, it can be implemented on any standard CMOS technology line. The specific preparation method will be described below by taking an NPN-type punch-through effect-enhanced silicon phototransistor manufactured by a standard double-well CMOS process with a feature size of 0.5 μm, two layers of polysilicon, and three layers of metal as an example.

[0054] A: Selection of substrate - select a P-type silicon substrate, the substrate resistivity is 15Ω·cm, and the thickness is 100μm;

[0055] B: Formation of the well region—a well is formed by high-energy ion implantation and thermal propulsion. Since it is to make an NPN phototransistor, the P well is used as the base area of the device, that is figure 1 2 of them. As was implanted, the implantation energy and dose of ion implantation were 100keV and 5×10 12 cm -2 . After advancing ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com