Process for treating silicon through-hole interconnection construction

A process method and interconnection structure technology, which is applied in the manufacture of electrical components, circuits, semiconductors/solid-state devices, etc., can solve problems such as long working hours, increased costs, and overruns, so as to alleviate thermal mismatch, reduce parasitic capacitance, and reduce heat dissipation. The effect of mechanical stress

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

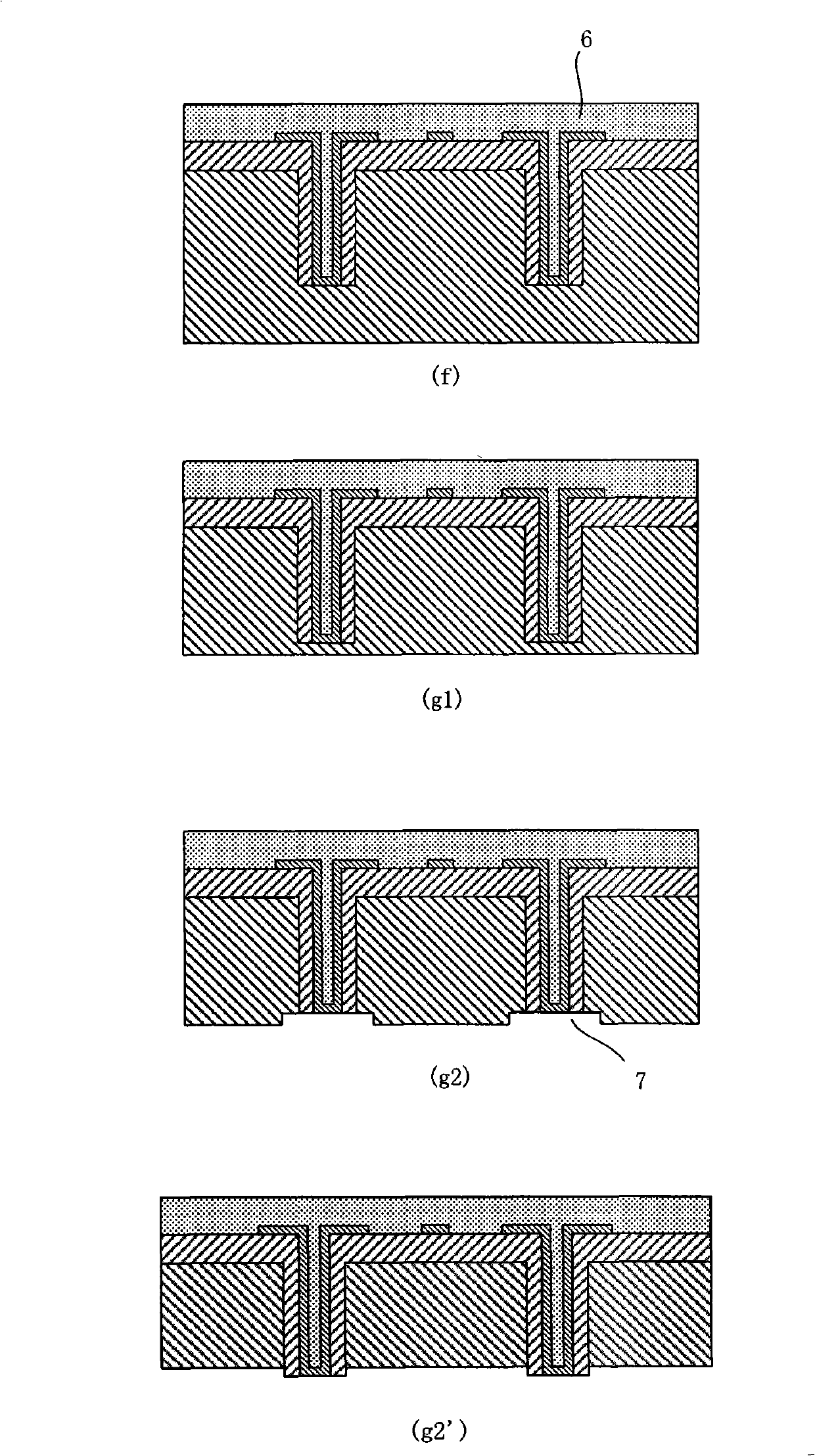

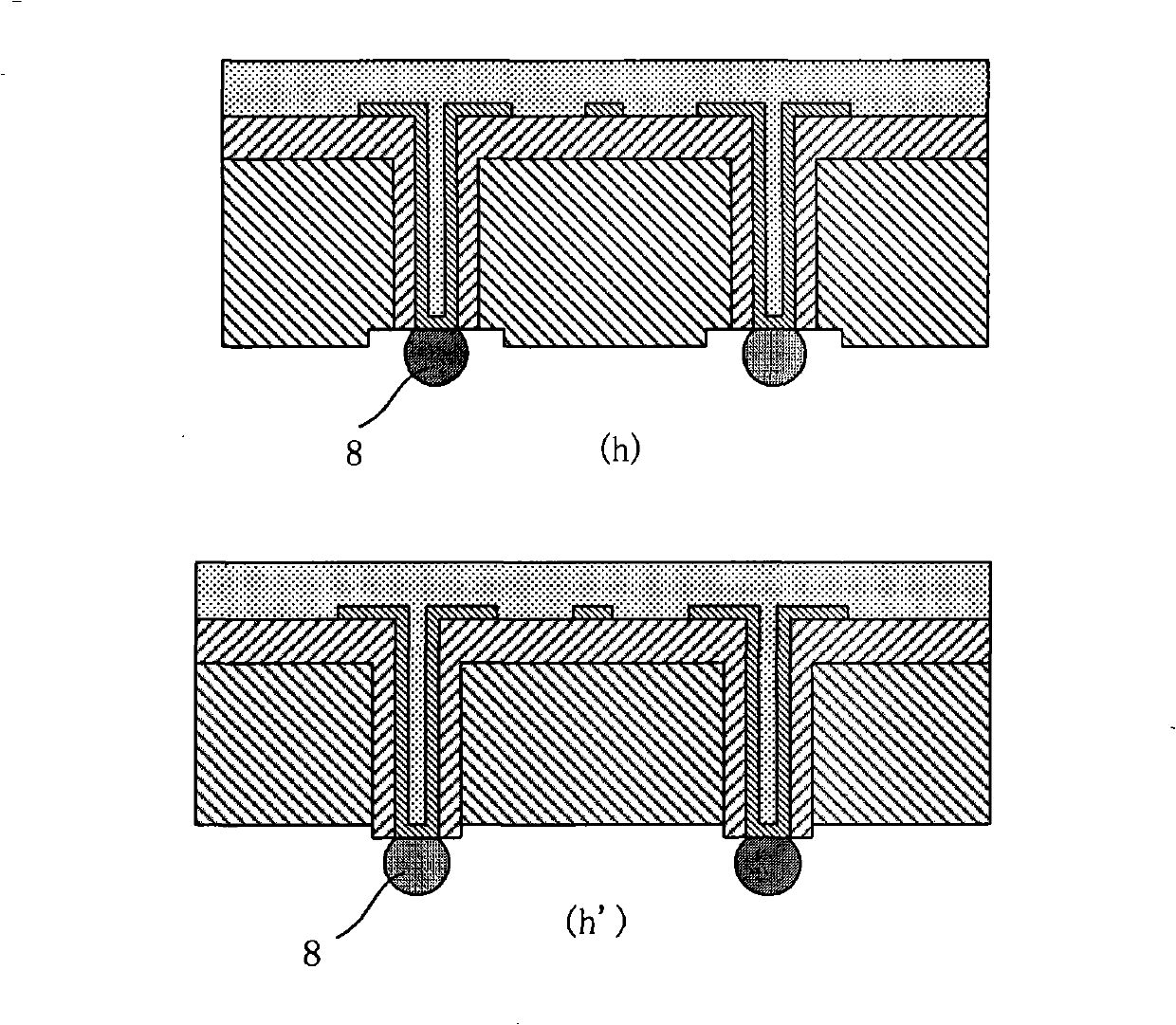

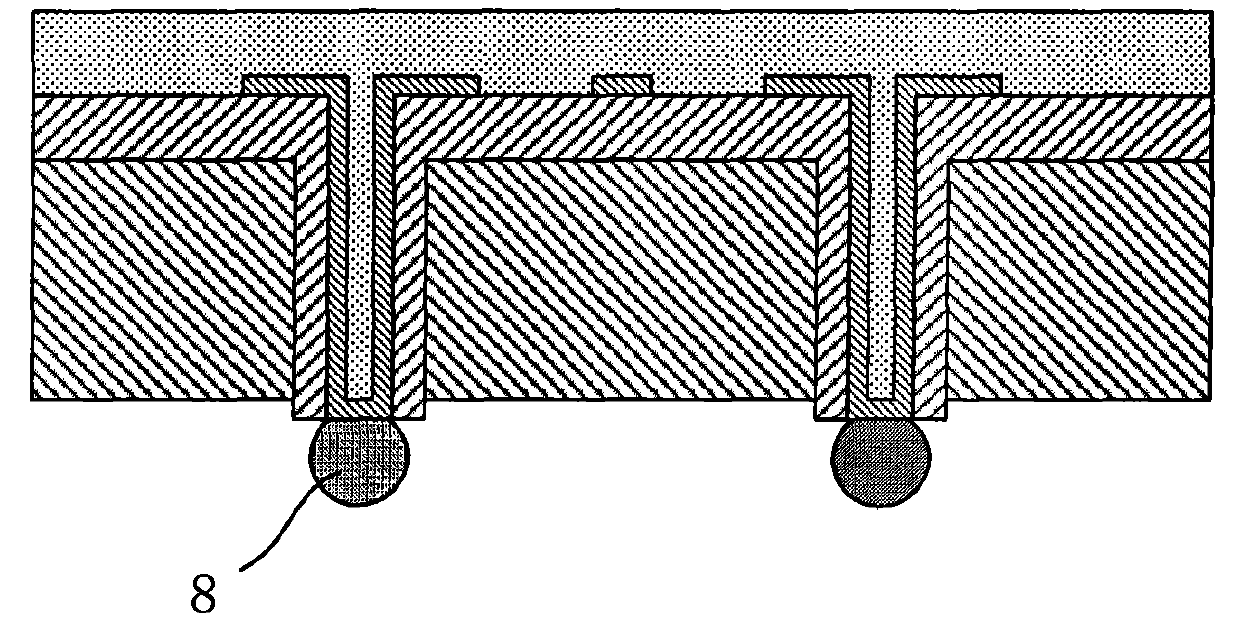

[0018] The specific implementation of the process method provided by the present invention will be further described in detail below in conjunction with the accompanying drawings and examples. The inventive method comprises:

[0019] (a) Provide a substrate 1 such as figure 1 (a) shows. The substrate can be a piece of unprocessed or processed wafer (such as silicon wafer or silicon device wafer), or it can be a microelectronic device. The thickness of the substrate is 10-500 microns.

[0020] (b) dry etching the above substrate 1 to form at least one blind hole 2 , and the aspect ratio of the blind hole 2 is 5:1-20:1. The blind holes 2 can have different shapes and sizes. Etching can use existing technology. Such as reflective ion etching-inductively coupled plasma technology (RIE-ICP) or deep reflected ion etching-inductively coupled plasma technology (DRIE-ICP). The width of the blind hole 2 is usually 20-100 microns, preferably 25 microns, and is most preferably cylind...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More