Gallium nitride-based high electron mobility transistor and preparation method thereof

A high electron mobility, gallium nitride-based technology, applied in the field of gallium nitride-based high electron mobility transistors and their preparation, can solve the problem of limited improvement in the quality of gallium nitride thin film crystals, affecting the high electron mobility of gallium nitride-based The performance of high-speed transistors can be solved, so as to alleviate the accumulation of dislocations and stress, reduce defects and dislocations, and improve the crystal quality.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

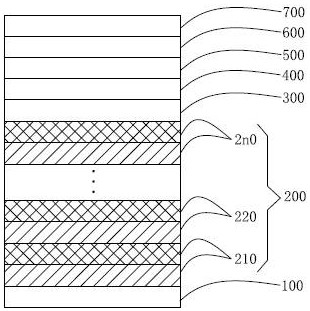

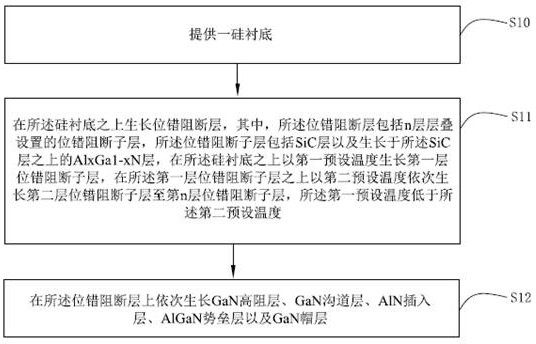

[0031] see figure 1 , shows a GaN-based high electron mobility transistor provided by the first embodiment of the present invention, the GaN-based high electron mobility transistor includes a silicon substrate 100; wherein, a silicon material is used as the substrate, and the It has the advantages of good thermal conductivity, large-scale epitaxial growth, high crystal quality, easy integration and low price, and has great market competitiveness.

[0032] The dislocation blocking layer 200 , the GaN high resistance layer 300 , the GaN channel layer 400 , the AlN insertion layer 500 , the AlGaN barrier layer 600 and the GaN cap layer 700 are sequentially stacked on the silicon substrate 100 . Among them, the dislocation blocking layer 200 is used to slow down the lattice mismatch and thermal mismatch between the silicon substrate 100 and the gallium nitride film, improve the crystal quality of the gallium nitride film, and improve the high electron mobility of the gallium nitri...

Embodiment 2

[0051] A second embodiment of the present invention provides a GaN-based high electron mobility transistor, the GaN-based high electron mobility transistor in this embodiment and the GaN-based high electron mobility transistor in the first embodiment The difference is:

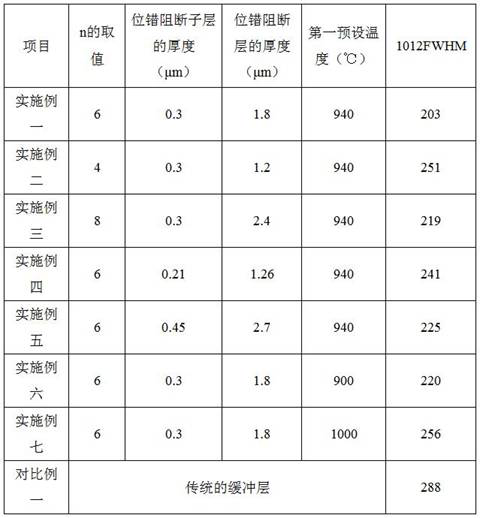

[0052] The dislocation blocking layer includes 4 dislocation blocking sub-layers stacked in layers, other conditions are the same, Al x Ga 1-x The composition ratio x of Al in the N layer is 0.15, and the thickness of the SiC layer is the same as that of Al. x Ga 1-x The thickness ratio of the N layer is 1:2, the thickness of the dislocation blocking sublayer is 0.3 μm, and the first preset temperature is 940°C.

Embodiment 3

[0054] A third embodiment of the present invention provides a GaN-based high electron mobility transistor, the GaN-based high electron mobility transistor in this embodiment and the GaN-based high electron mobility transistor in the first embodiment The difference is:

[0055] The dislocation blocking layer includes 8 dislocation blocking sub-layers arranged by stacking, other conditions are the same, Al x Ga 1-x The composition ratio x of Al in the N layer is 0.15, and the thickness of the SiC layer is the same as that of Al. x Ga 1-x The thickness ratio of the N layer is 1:2, the thickness of the dislocation blocking sublayer is 0.3 μm, and the first preset temperature is 940°C.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More