Preparation process of superconductive planar circuit

A planar circuit and preparation process technology, which is applied in the manufacture/processing of superconductor devices, multilayer circuit manufacturing, and the formation of electrical connection of printed components, etc. and other problems, to achieve the effect of reducing performance deterioration and impact on circuit performance, meeting large-scale industrialization, and long process cycle.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

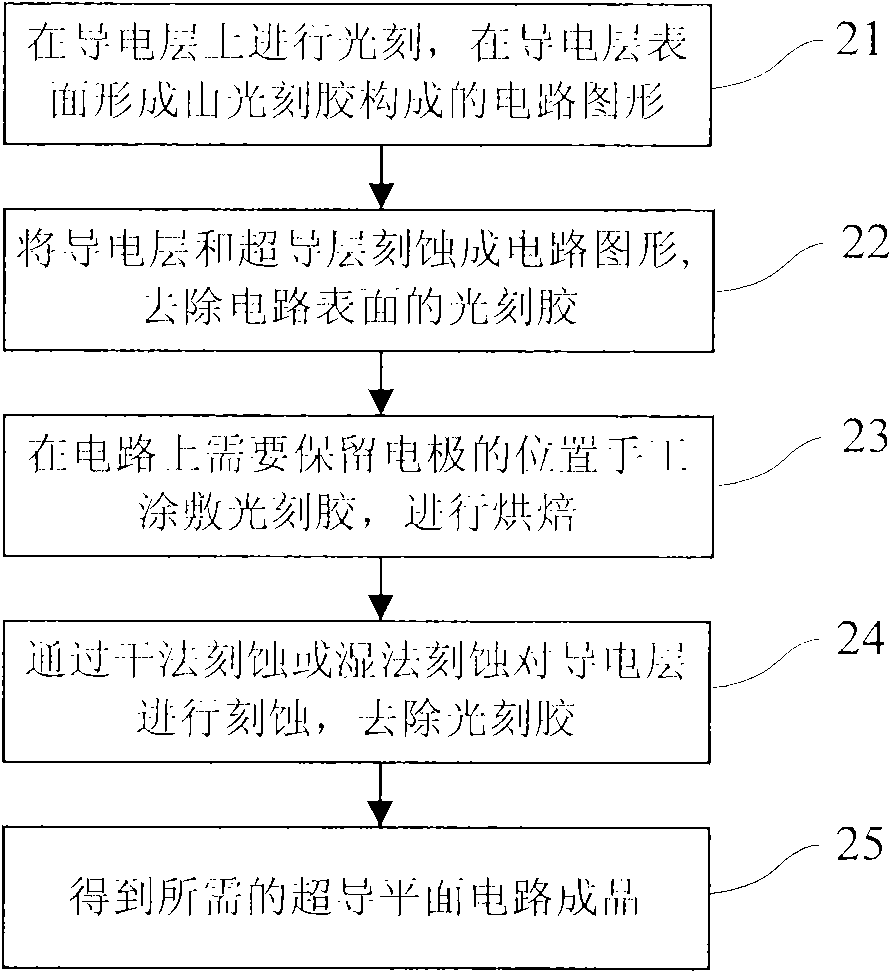

[0030] figure 2 It is a flow chart of an embodiment of the preparation process of the superconducting planar circuit of the present invention.

[0031] The preparation process is carried out in a clean room within 100 grades, the temperature is room temperature, and the relative humidity is less than 40%. The specific preparation steps are as figure 2 Shown:

[0032] Step one (21), provide a substrate with conductive layer and superconducting thin film layer on the surface, described substrate can be silicon Si, silicon Si / silicon dioxide SiO 2 , germanium Ge, gallium arsenide GaAs, etc., or lanthanum aluminate LaAlO 3 , magnesium oxide MgO, strontium titanate SrTiO 3 , sapphire and other single crystal substrates, the thickness is 0.05 ~ 1mm. The superconducting material can be simple substance, alloy and simple compound, such as niobium Nb, lead Pb, niobium-zirconium alloy Nb-Zr, niobium-titanium alloy Nb-Ti, niobium-titanium-tantalum alloy Nb-Ti-Ta, niobium-tin alloy...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More