Panel display driving chip based on silicon on insulator (SOI) and preparation method thereof

A flat-panel display and driver chip technology, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problems of high process conditions, waste of chip area, insufficient reliability, etc., and achieve good anti-latch performance. , The effect of excellent reliability and low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

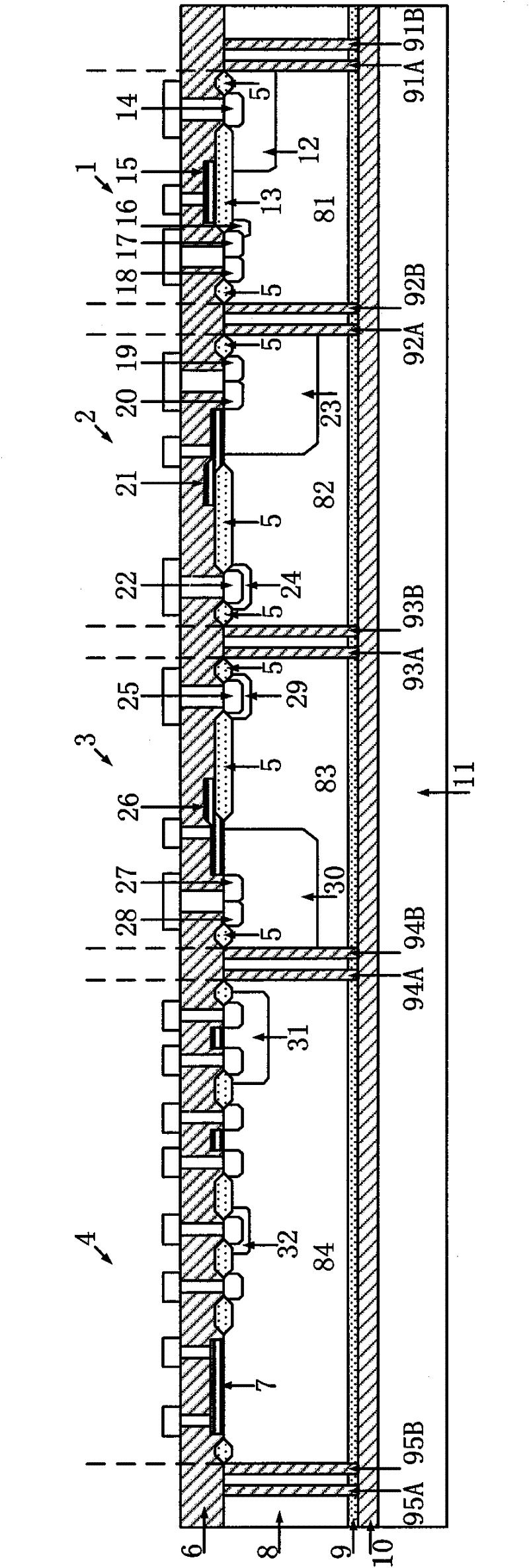

[0021] Below in conjunction with accompanying drawing, the present invention is described in detail, as figure 1Shown, a kind of flat panel display drive chip comprises P-type substrate 11, is provided with buried oxide layer 10 on P-type substrate 11, is characterized in that is provided with N-type buried layer 9 on buried oxide layer 10, in N The buried layer 9 is provided with a high-voltage P-type lateral metal oxide semiconductor transistor 1, a high-voltage N-type lateral metal oxide semiconductor transistor 2, a high-voltage N-type lateral insulated gate bipolar transistor 3, and a low-voltage device 4. The oxide semiconductor transistor 1 is adjacent to the high-voltage N-type lateral metal-oxide-semiconductor transistor 2 and the drain end of the high-voltage P-type lateral metal-oxide semiconductor transistor 1 is adjacent to the source end of the high-voltage N-type lateral metal-oxide semiconductor transistor 2. The N-type lateral insulated gate bipolar transistor...

Embodiment 2

[0030] The preparation method of the high-voltage device for driving the flat panel display of the present invention is:

[0031] The first step: take the impurity concentration as 1.0e15cm -3 The P-type substrate 11 shown in Figure 2(a) is pre-cleaned; the buried oxide layer 10 is prepared on the P-type substrate 11 as shown in Figure 2(b); then the growth impurity concentration is 1.5e15cm -3 N-type epitaxial layer 8, and pass a dose of 1e12cm -2 As shown in Figure 2 (c), an N-type buried layer 9 is fabricated on the N-type epitaxial layer 8; a P-type body of a high-voltage N-type lateral metal oxide semiconductor transistor 2 is respectively fabricated on the N-type epitaxial layer 8 Region 23 and the P-type body region 30 of the high-voltage N-type lateral insulated gate bipolar transistor 3 are shown in Figure 2(d); then the P-type drift region 12 fabricated on the N-type epitaxial layer 8 is shown in Figure 2(e) As shown; Next, on the N-type epitaxial layer 8, the drai...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More