Method for manufacturing n-metal-oxide-semiconductor (NMOS) transistor

A manufacturing method and transistor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of poor performance of semiconductor devices, difficulty in ion implantation depth and concentration, and failure of NMOS transistor resistance and junction depth to meet requirements and other problems, to achieve the effects of reducing the resistance of the source and drain regions, suppressing diffusion and channel effects, and suppressing instantaneously enhanced diffusion and tunneling effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

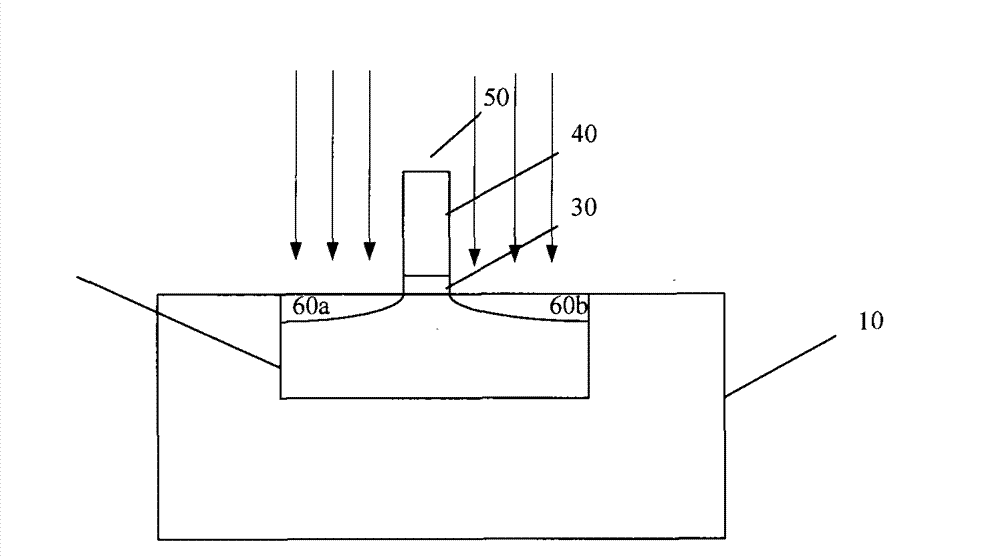

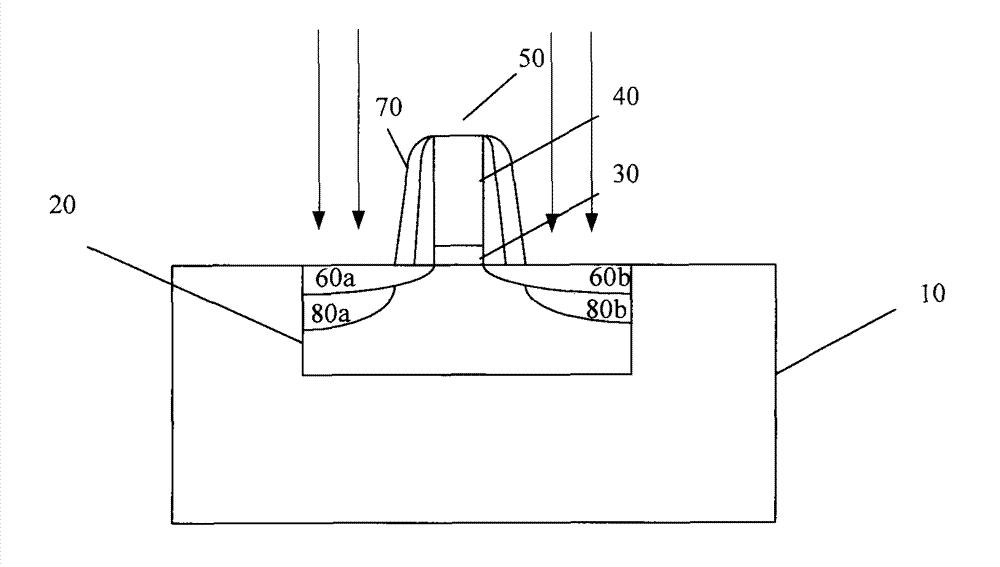

[0057] Figure 4 It is a flow chart of an embodiment of the manufacturing method of the NMOS transistor of the present invention. Figure 5 to Figure 7 It is a schematic diagram of an embodiment of the manufacturing method of the NMOS transistor of the present invention. Combine below Figure 5 to Figure 7 The semiconductor device manufacturing method of the invention is described in detail, the semiconductor device manufacturing method of the present invention includes steps:

[0058] S20: providing a semiconductor substrate having a gate structure on the semiconductor substrate.

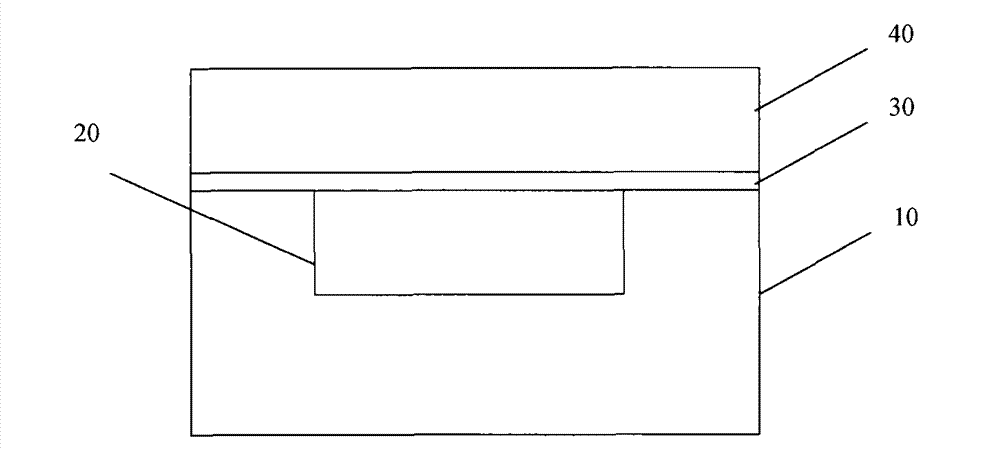

[0059] refer to Figure 5 Specifically, the semiconductor substrate 100 may be silicon or silicon germanium (SiGe) with a single crystal, polycrystalline or amorphous structure, or silicon-on-insulator (SOI), or may also include other materials, such as indium antimonide , lead telluride, indium arsenide, indium phosphide, gallium arsenide, or gallium antimonide. Although several examples of m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More