Method for manufacturing semiconductor device

A manufacturing method and semiconductor technology, which can be used in semiconductor/solid-state device manufacturing, electrical components, radiation control devices, etc., and can solve the problem of large difference in thickness of the dielectric layer of the chip.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

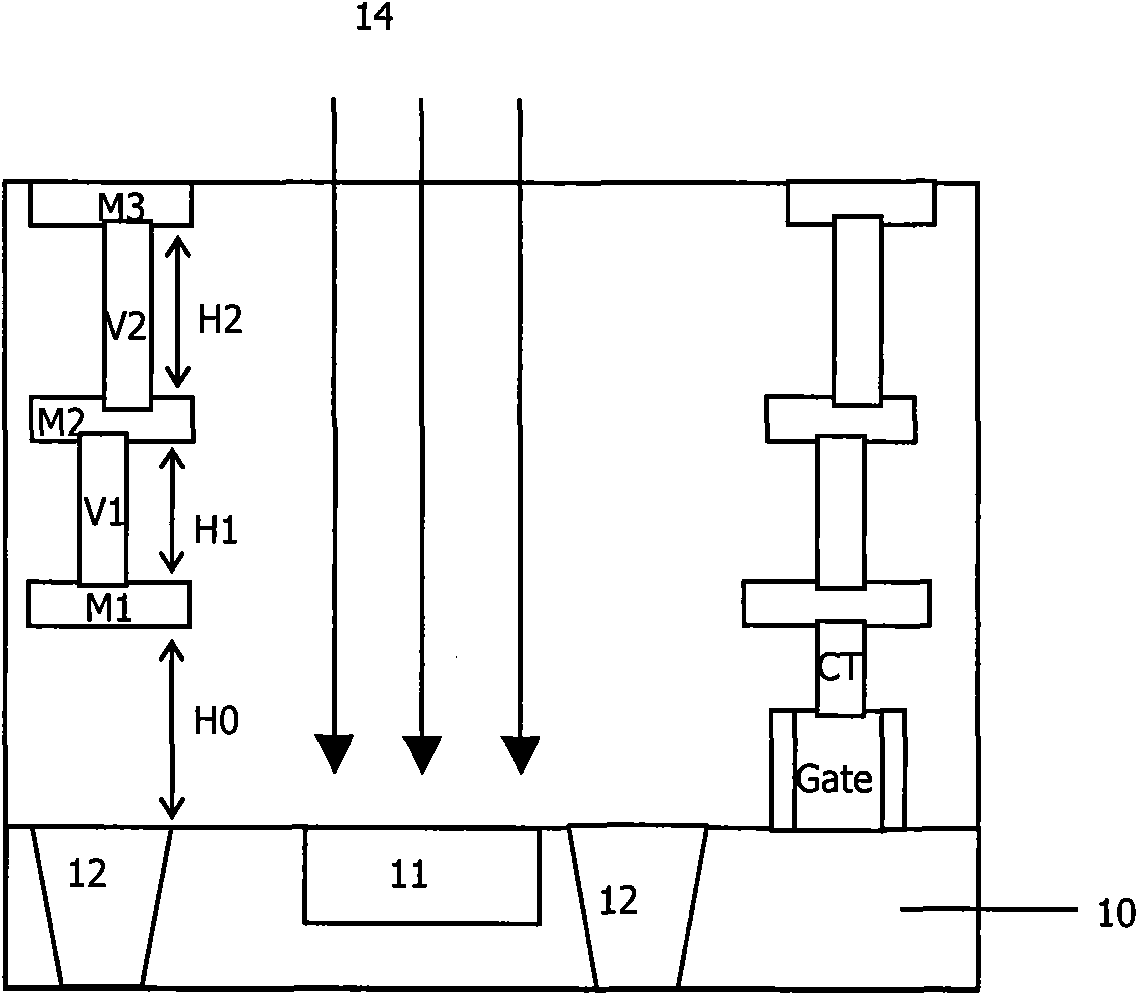

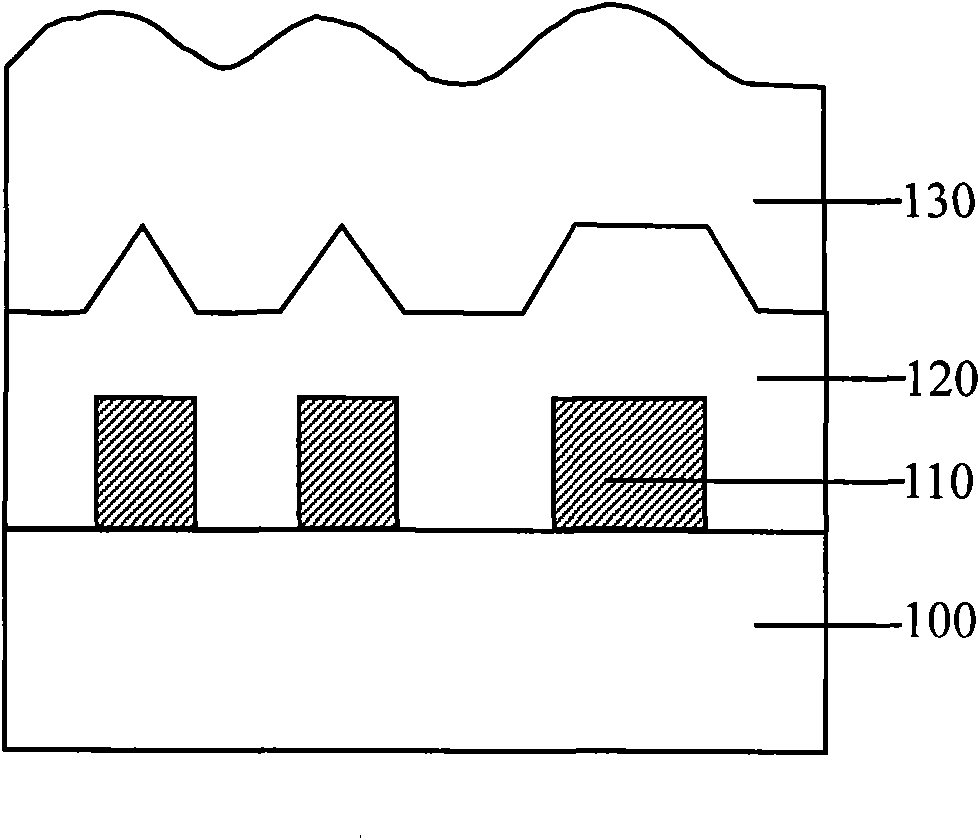

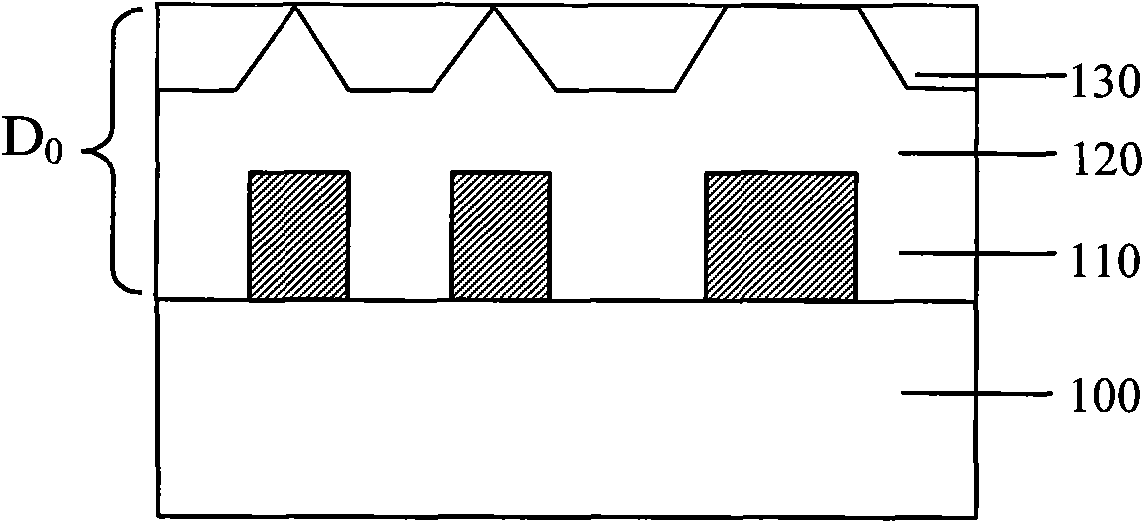

[0026] According to the background technology, the method for increasing the sensitivity of the CIS chip in the prior art is to use the CMP process to polish the dielectric layer of the wafer (including the interlayer dielectric layer ILD, the intermetal dielectric layer IMD, and the metal front dielectric layer PMD) , to reduce the thickness of the dielectric layer, but because the CMP process has different polishing rates for the center and the edge of the wafer, the method described on the wafer will cause the height difference between the center of the wafer and the surface of the edge of the wafer to be too high Large, resulting in a decline in the yield of the wafer. Therefore, the present invention proposes a method. After the dielectric layer is formed, an etching barrier layer is deposited on the dielectric layer, and then a DUO layer is formed on the dielectric layer by a spin coating process, and then the DUO layer is sequentially etched by an etching process. The e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More