Data bus in multi-kernel processor chip

A multi-core processor and data bus technology, applied in the direction of electrical digital data processing, instruments, digital computer components, etc., can solve the core's impact on data input/output operations, static routing network performance, complex routing control, poor bus flexibility, etc. Problems, to achieve good mapping, improve the main frequency of the system, and achieve the effect of good local characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The specific embodiments of the present invention will be further introduced below in conjunction with the accompanying drawings.

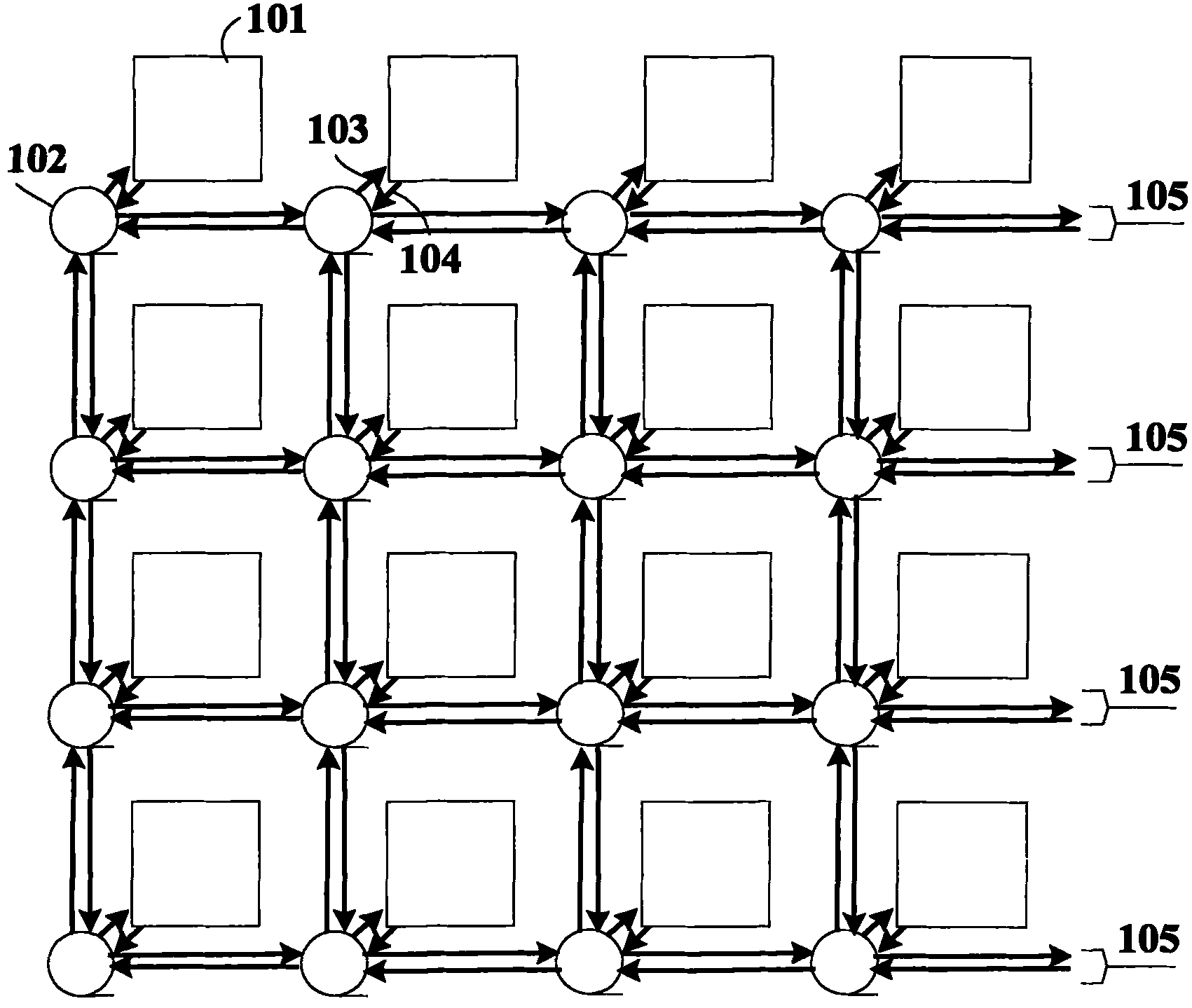

[0043] In the embedded field, traditional control-intensive applications are gradually changing to data-intensive applications, and the proportion of data calculation and processing is gradually increasing. In response to this feature, in the design of multi-core chips, (taking the use of DSP engines as an example) is to integrate several DSP (digital signal processor) engines into the same chip, relying on the data communication network in the chip to realize these DSP engines. data interaction between them.

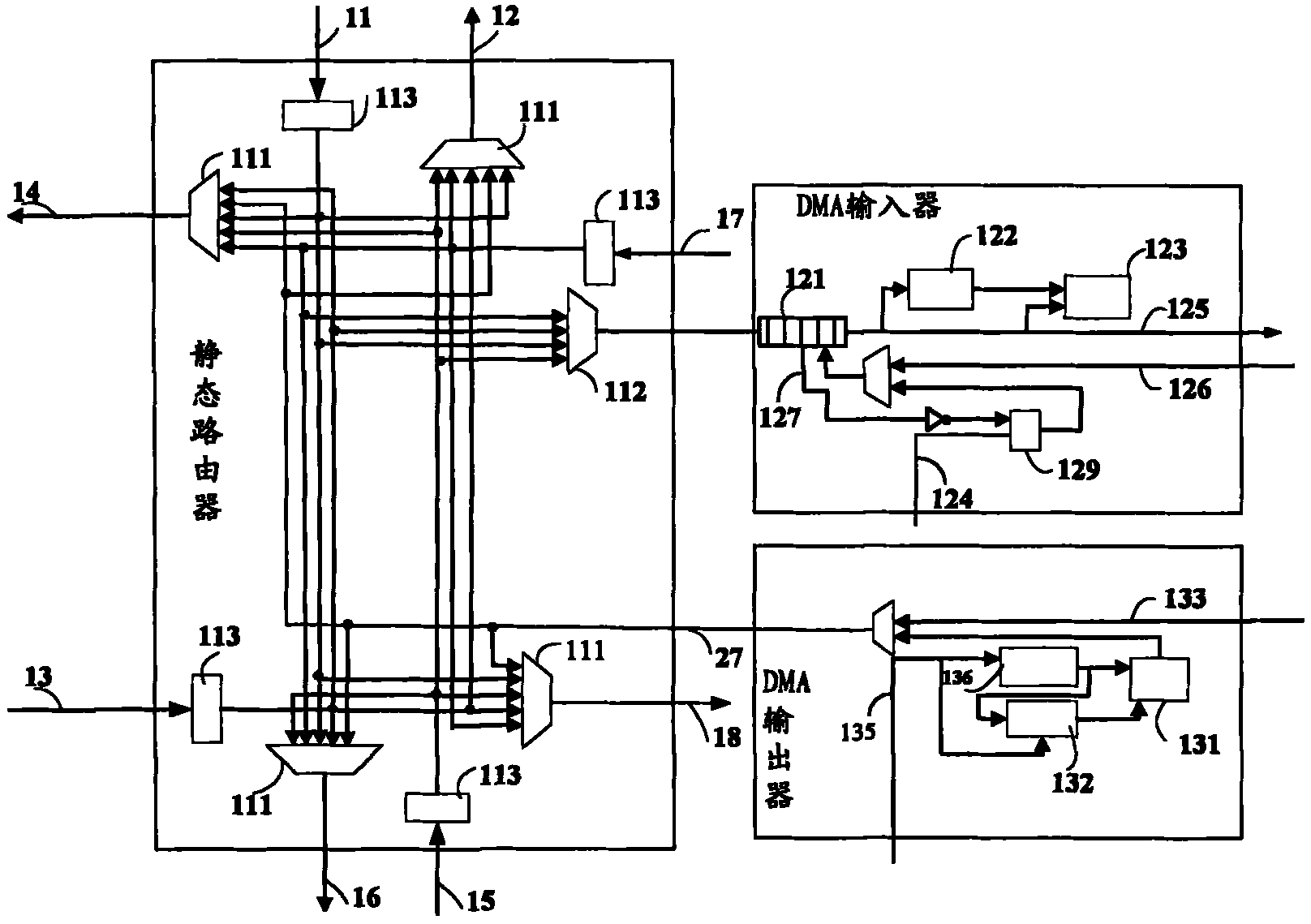

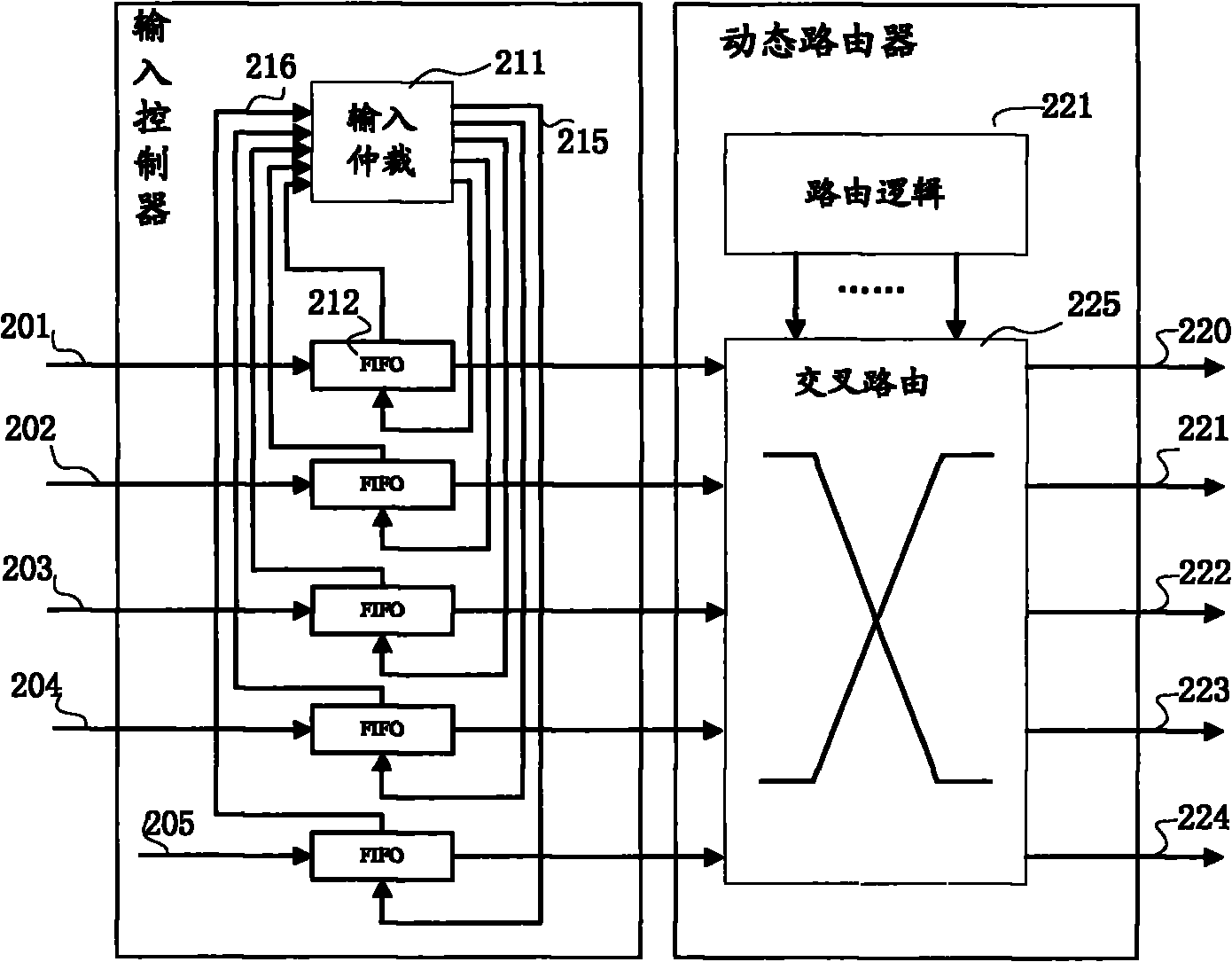

[0044] The data bus in the multi-core processor chip (or "multi-core chip") in the present invention is composed of a static routing bus and a dynamic routing bus. In terms of functional division, the static routing bus is responsible for high-throughput data transmission, and the dynamic routing bus completes flexible control varia...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More