All-silicon clock generator realized on basis of complementary metal oxide semiconductor (CMOS) process

A technology of clock generator and MOS tube, which is applied in the direction of instruments, pulse generation, electric pulse generation, etc., can solve the problems of temperature characteristics, process stability, poor power supply suppression ability, complex circuit, poor precision, etc., and achieve strong power supply suppression ability , The circuit structure is simple, the effect of reducing circuit cost and power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] Below in conjunction with accompanying drawing, preferred specific embodiment of the present invention is described:

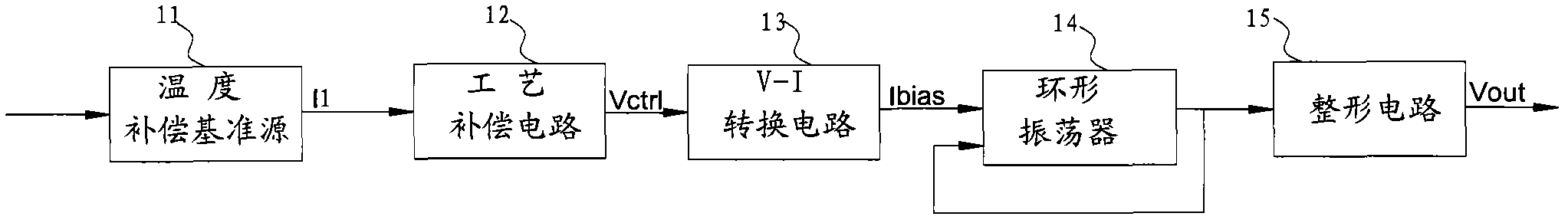

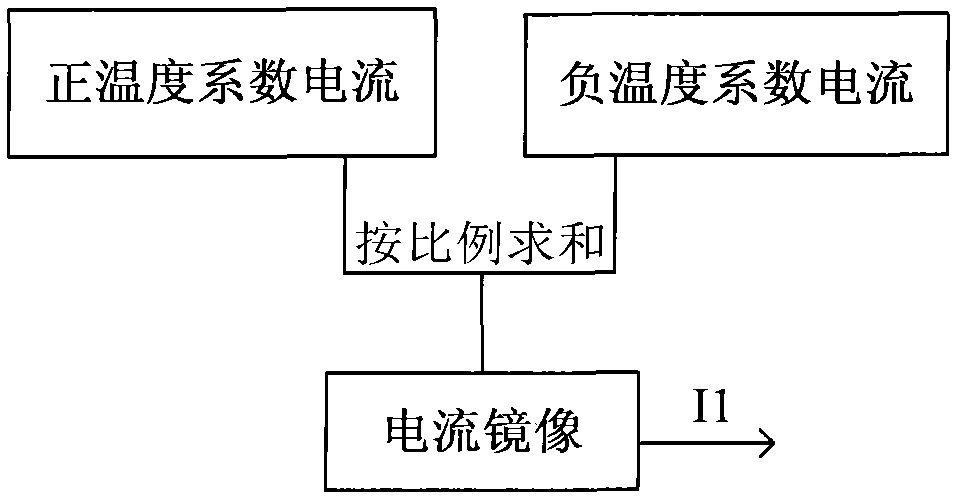

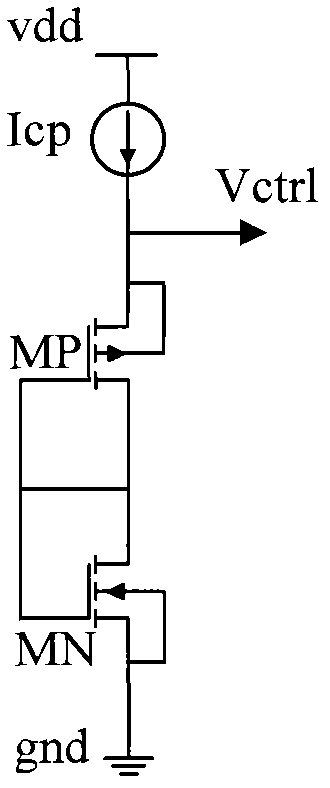

[0021] Such as figure 1 The all-silicon clock generator shown is sequentially connected by a temperature compensation reference source 11, a process compensation circuit 12, a V-I conversion circuit 13, a ring oscillator 14, and a shaping circuit 15. The temperature compensation reference source 11 is used to receive input power supply voltage, and temperature-compensate the input voltage according to the change of external temperature to output a stable voltage or current signal to the process compensation circuit 12, and the process compensation circuit 12 receives the voltage or current signal output by the reference source and generates the circuit according to the entire clock Process deviation is compensated to output a compensated control voltage Vctrl, and the control voltage Vctrl is output to the V-I conversion circuit 13 to be converted into ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More