Patents

Literature

72results about How to "Improve clock accuracy" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

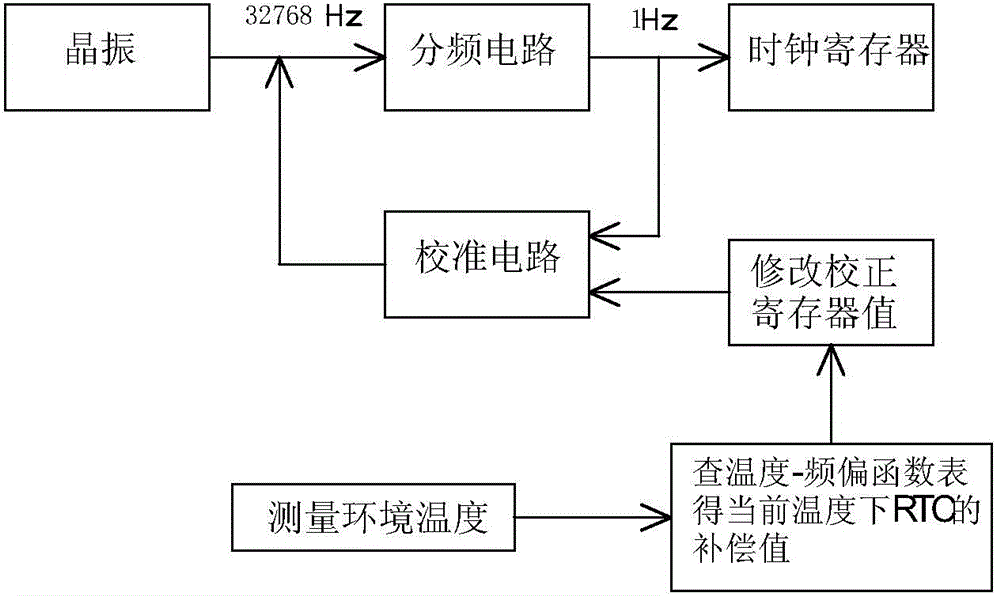

Method for improving precision of built-in real-time clock of electric energy meter MCU

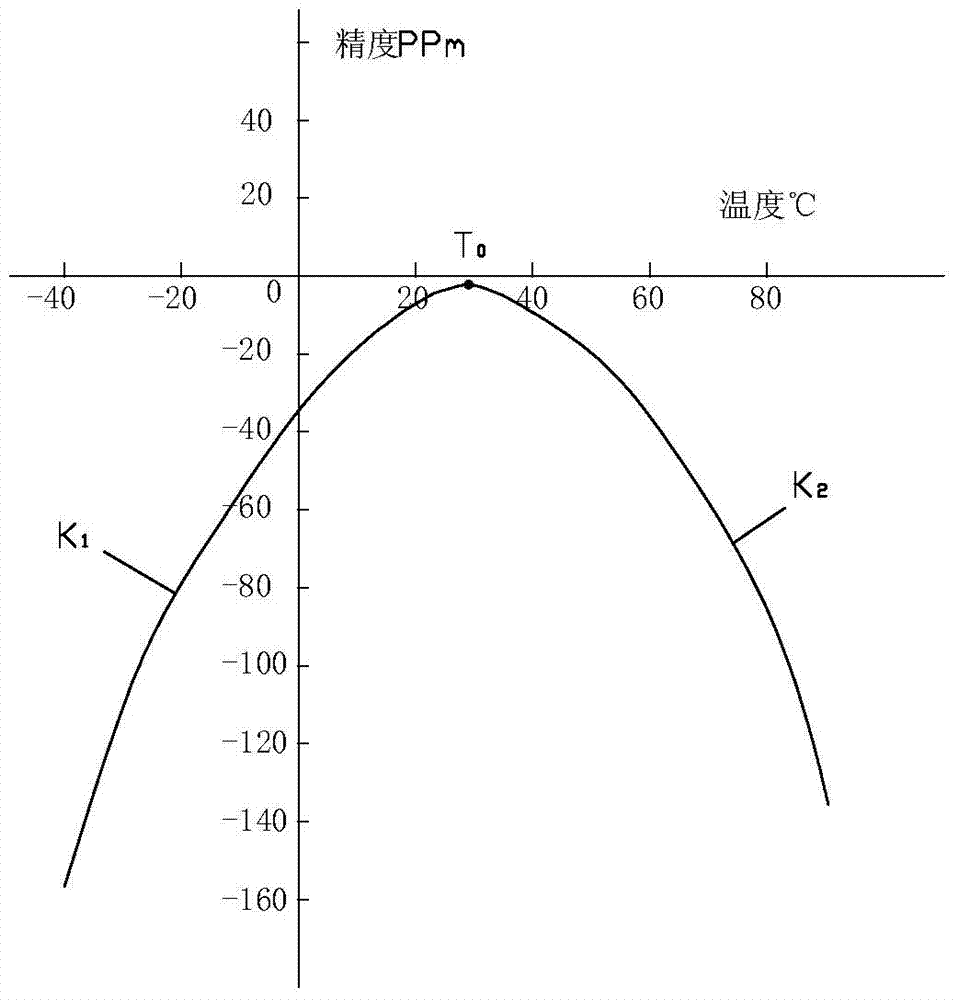

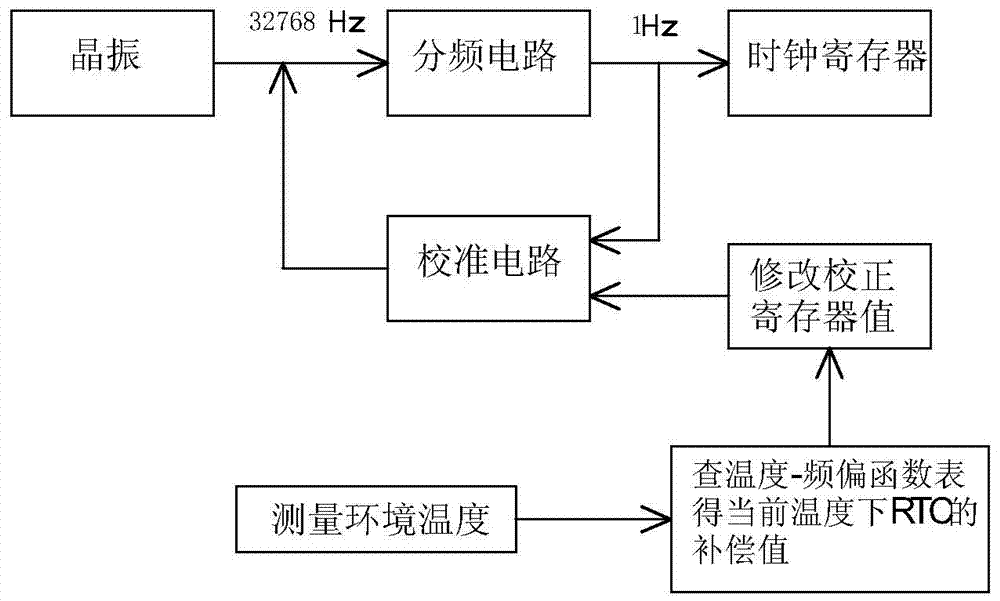

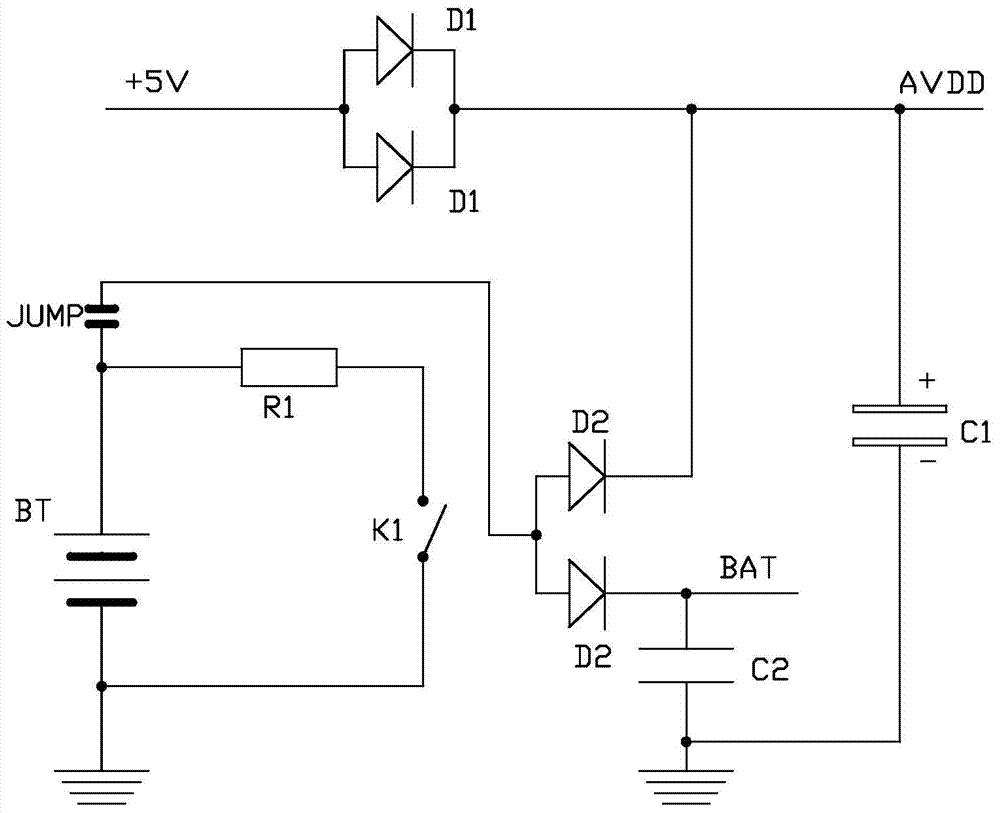

ActiveCN103499803ACompensation value is accurateImprove clock accuracyElectrical measurementsReal-time clockCurve fitting

The invention discloses a method for improving the precision of a built-in real-time clock of an electric energy meter MCU. Based on the practical crystal oscillator frequency, fine compensation can be achieved. An electric energy meter comprises the MCU, a crystal oscillator and a power management unit. The method for improving the precision of the built-in real-time clock of the electric energy meter MCU includes the following steps of compensation amount calculation and clock calibration. Compensation amount calculation is performed according to the following processes that firstly, frequency deviations of the practical crystal oscillator under different temperatures are measured; secondly, a temperature-frequency deviation curve sketch is drawn, and the turn temperature T0 is found out; thirdly, the measured frequency deviations of the two sides of T0 undergo curve fitting, and a corresponding buckling constant is obtained; fourthly, a temperature-frequency deviation function table is formed according to a function of the third process, the frequency deviation value of the current temperature can be obtained through the temperature-frequency deviation function table according to the practical environmental temperature, and the frequency deviation value serves as the compensation amount for calibrating the clock under the practical environmental temperature. According to the method for improving the precision of the built-in real-time clock of the electric energy meter MCU, an accurate compensation value can be obtained according to errors of the practical crystal oscillator, and therefore the precision of the clock is improved.

Owner:YANGZHOU WANTAI ELECTRIC TECH CO LTD

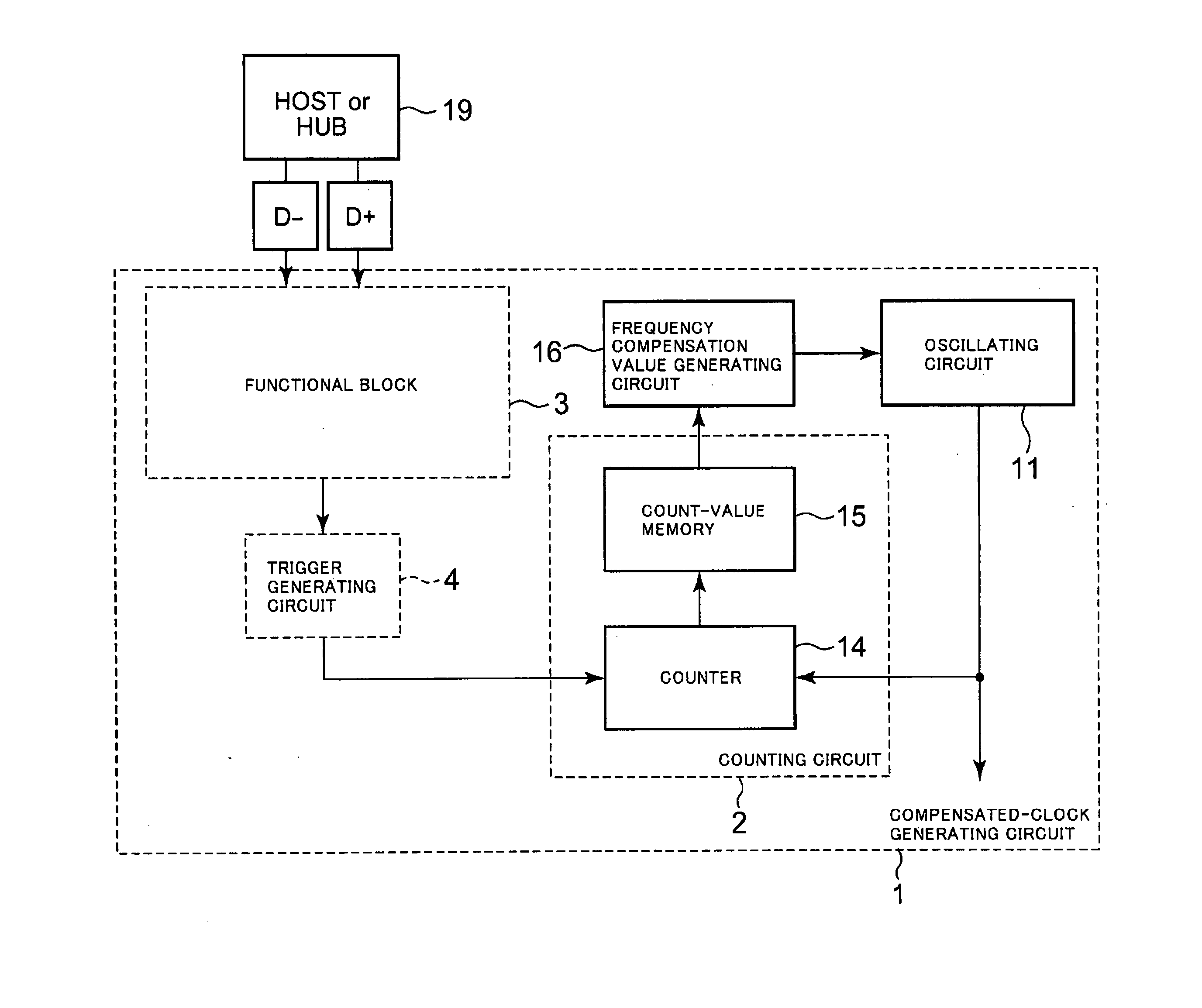

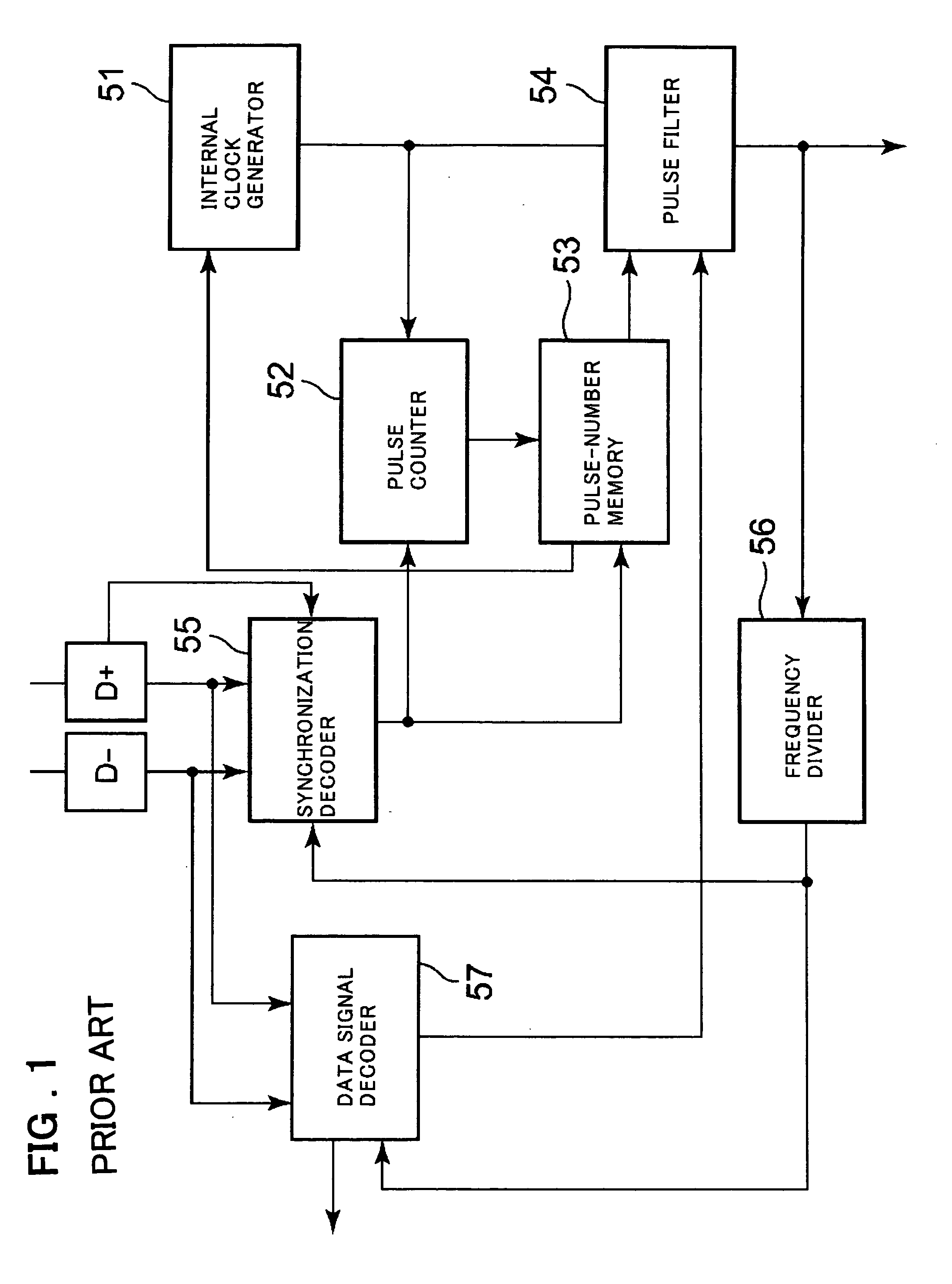

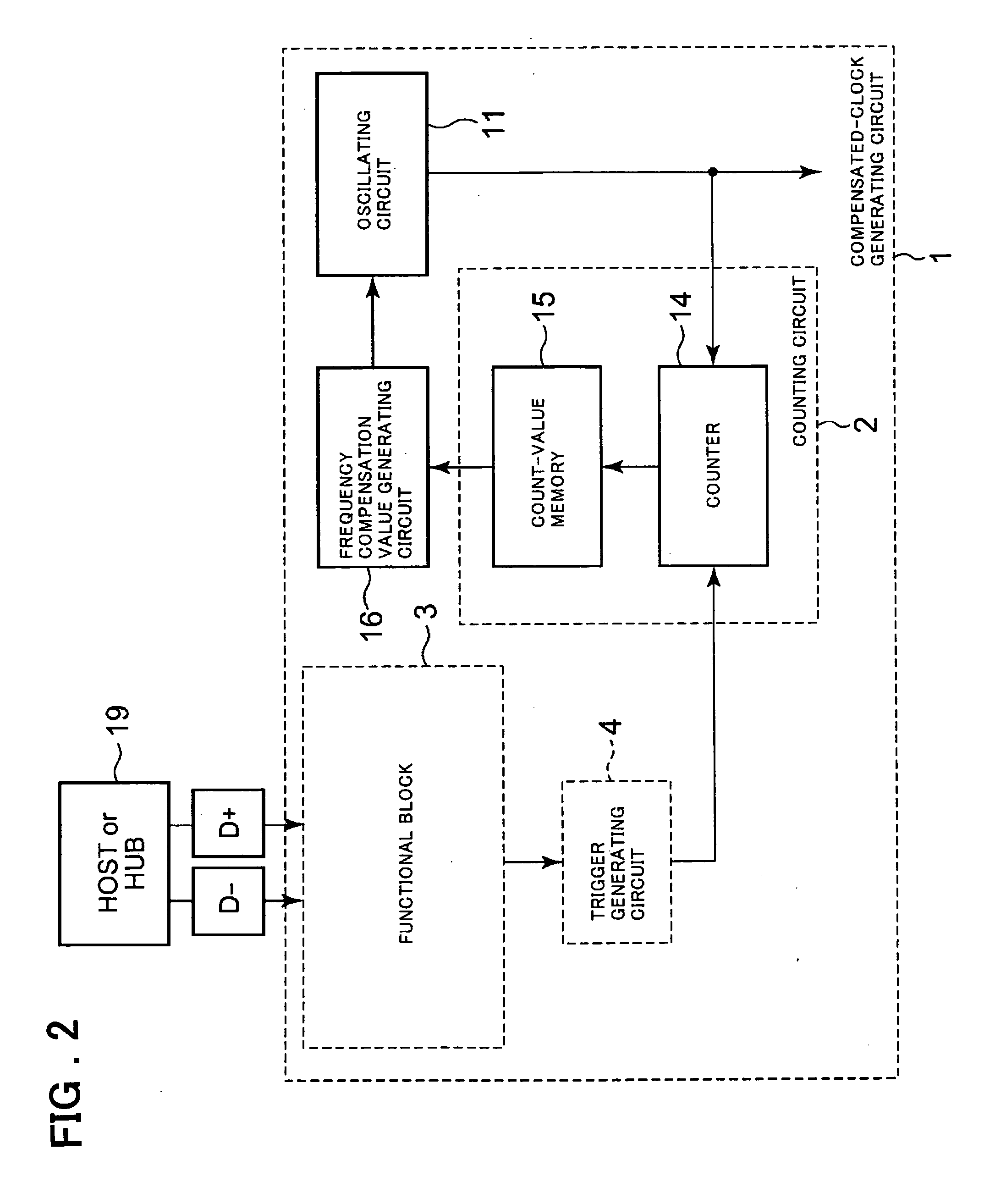

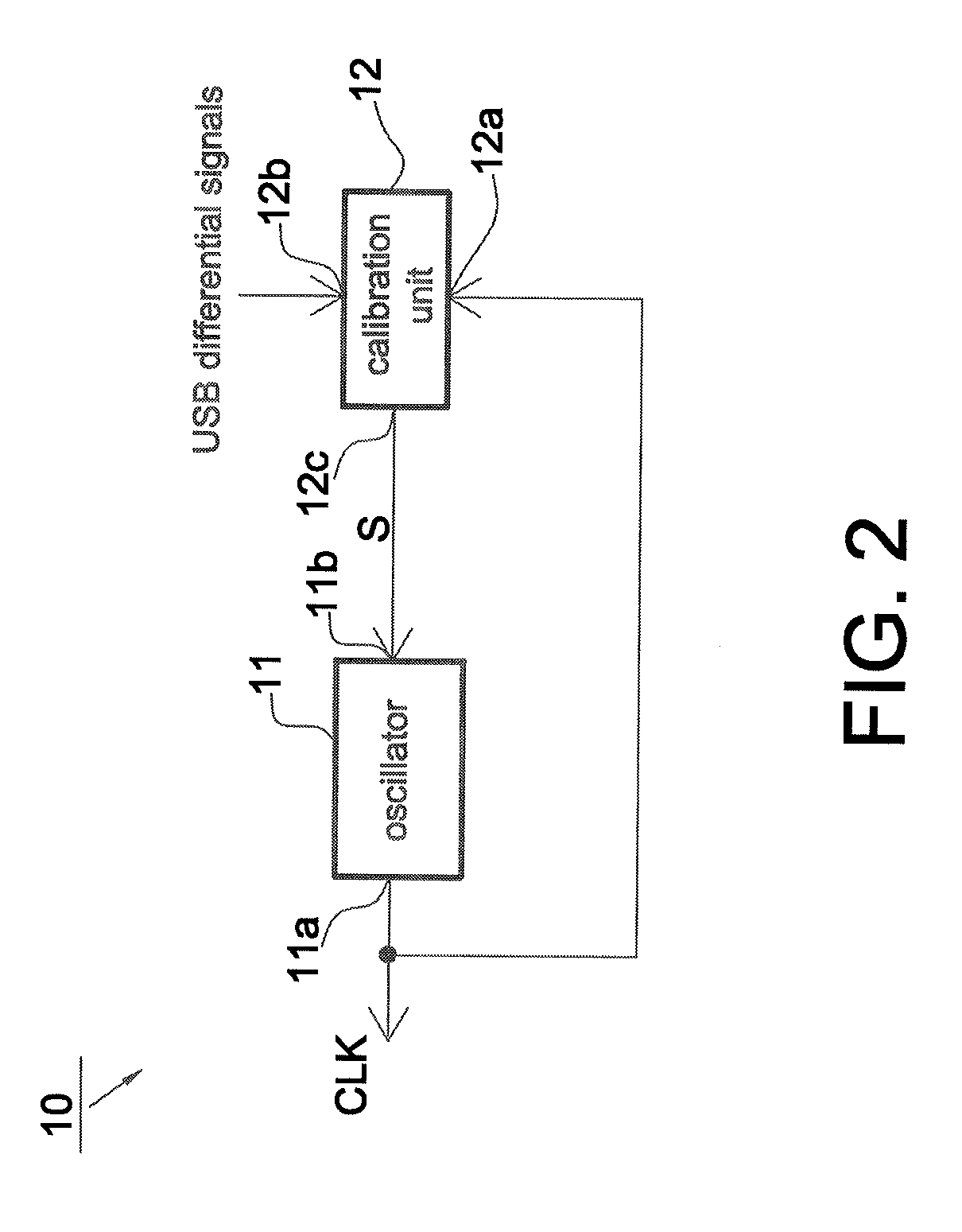

Compensated-clock generating circuit and USB device having same

InactiveUS20070079166A1Low costImprove clock accuracyPulse automatic controlDigital data processing detailsFrequency compensationUSB

A compensated-clock generating circuit that complies with USB specifications includes an oscillating circuit that generates clock pulses; a counting circuit that counts the number of clock pulses from the oscillating circuit based upon a regular prescribed signal in accordance with a USB downstream signal; and a frequency compensation value generating circuit that compares the value counted by the counting circuit and a prescribed reference value and obtaining a compensation value. The oscillation frequency of the oscillating circuit is corrected to a prescribed value in response to receipt of the compensation value from the frequency compensation value generating circuit. Compensation is applied based upon a highly accurate signal that is based upon USB specifications, thereby making it possible to generate pulses of higher accuracy even if the accuracy of the oscillation frequency per se of the oscillator in the oscillation circuit is low.

Owner:NEC ELECTRONICS CORP

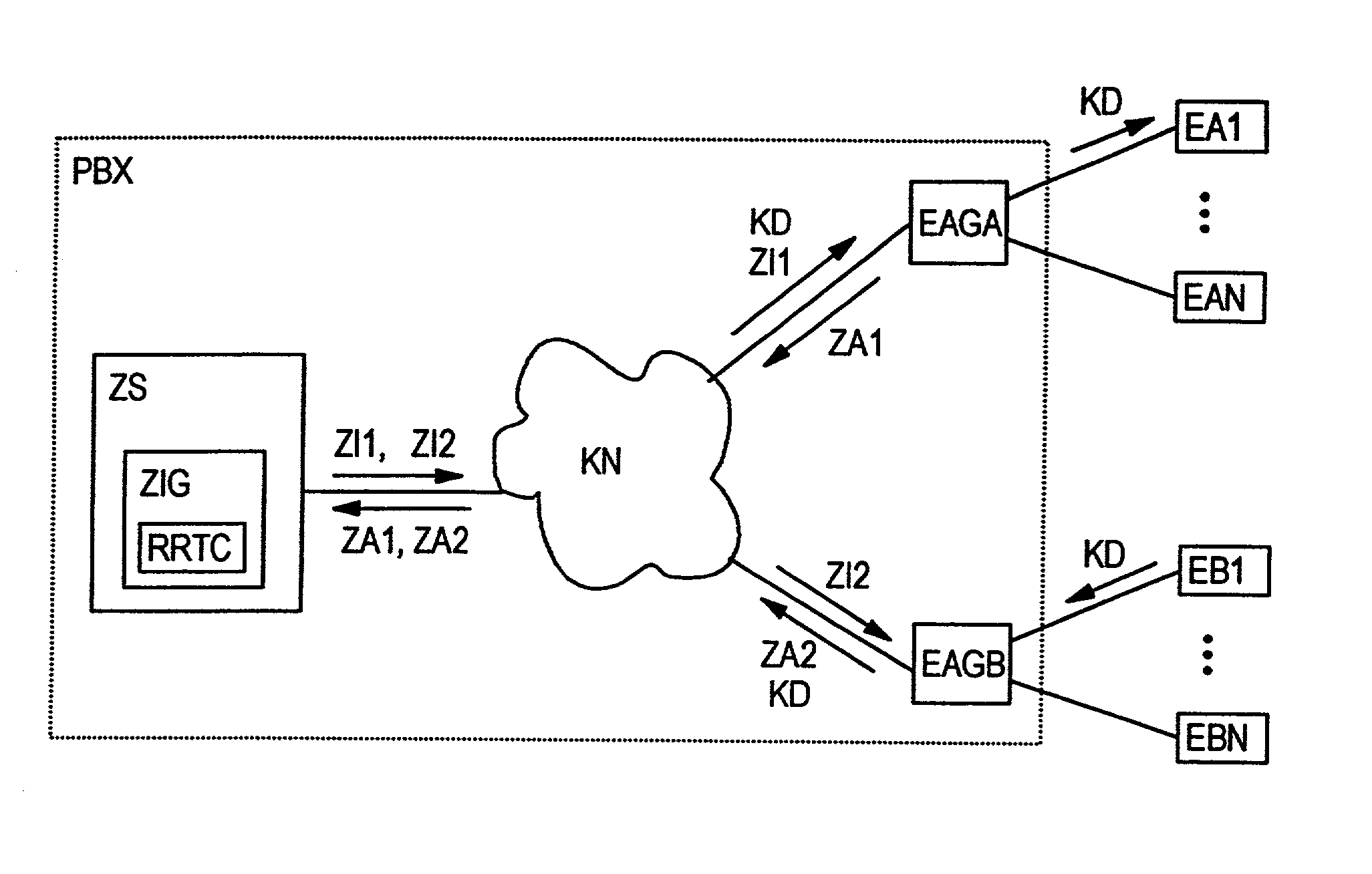

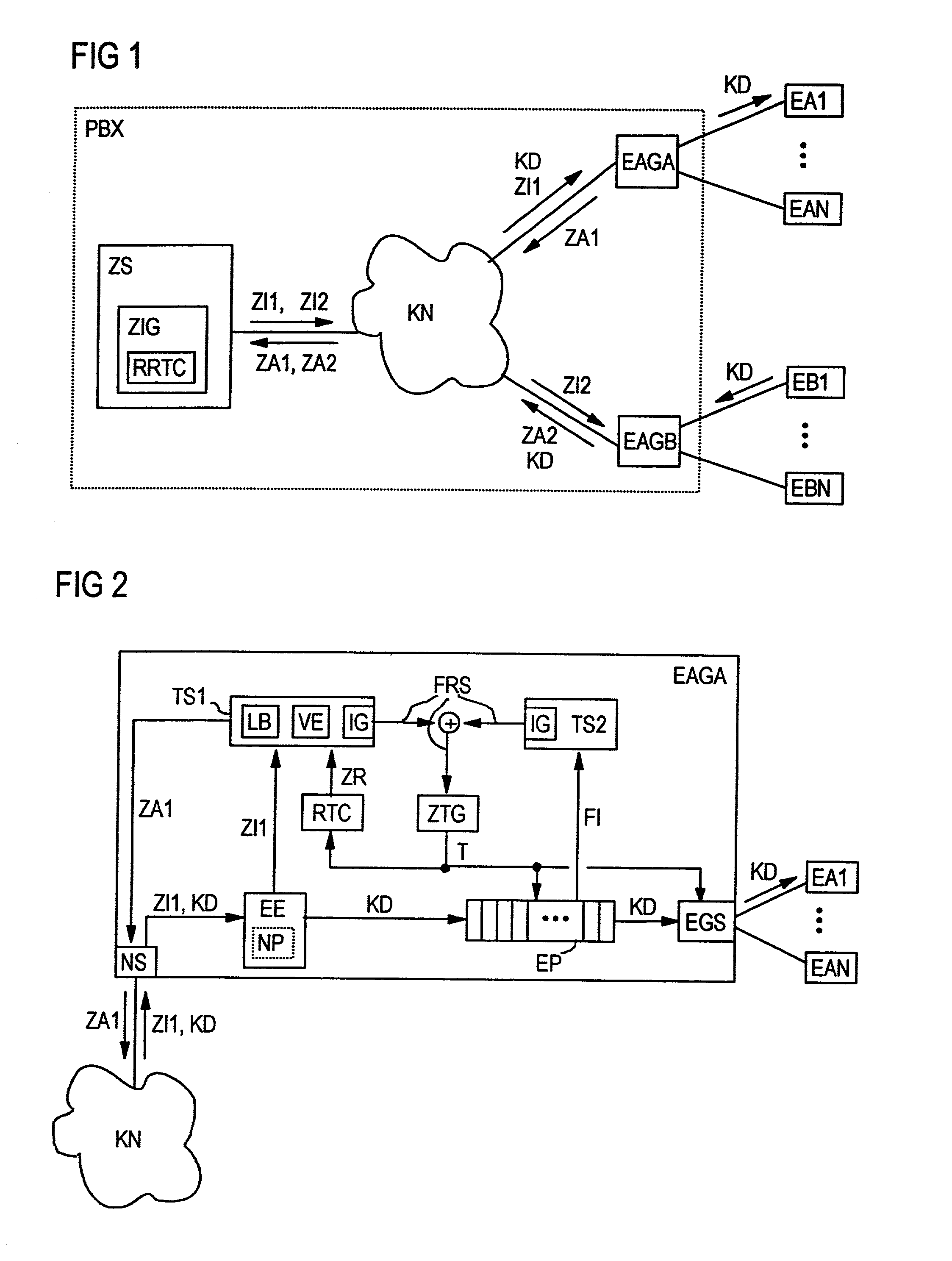

System for synchronizing communications system components coupled via a communications network

InactiveUS7085276B1Improve clock accuracyAccurate synchronizationTime-division multiplexData switching by path configurationTime informationReal-time clock

To synchronize communications system components coupled via a communications network, a time information transmitter is provided which is used to transmit time information, possibly on request, relating to the communications system components. The communications system components each have a clock generator, which needs to be synchronized, and a real time clock, where the clock generator both determines the transmission rate for communications data which are to be transmitted and prescribes the time base for the real time clock. In addition, the communications system components each have a comparison device for comparing received time information with a current time value indicated by the real time clock, and a clock frequency controller for regulating the clock frequency of the clock generator on the basis of the comparison result.

Owner:RINGCENTRAL INC

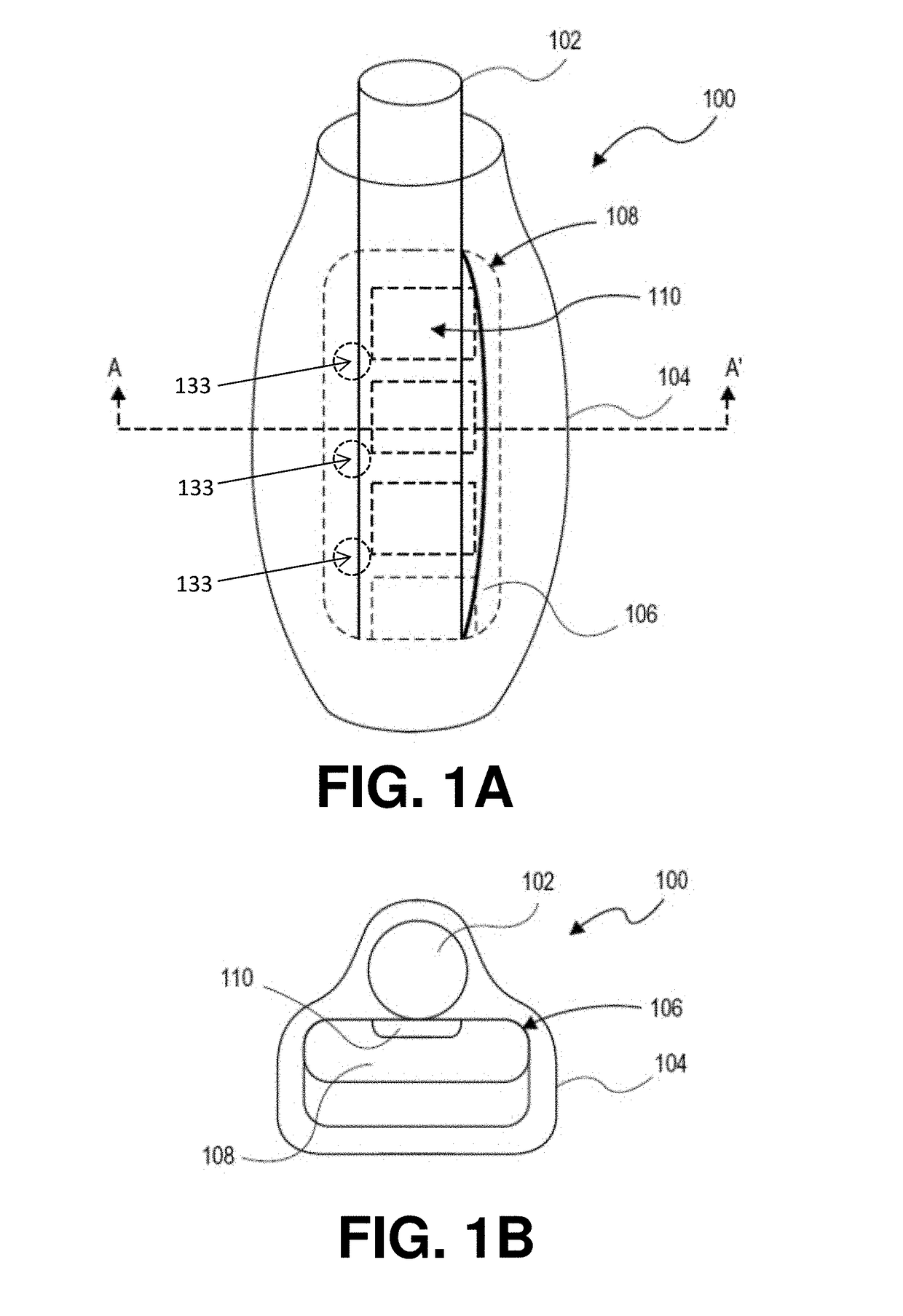

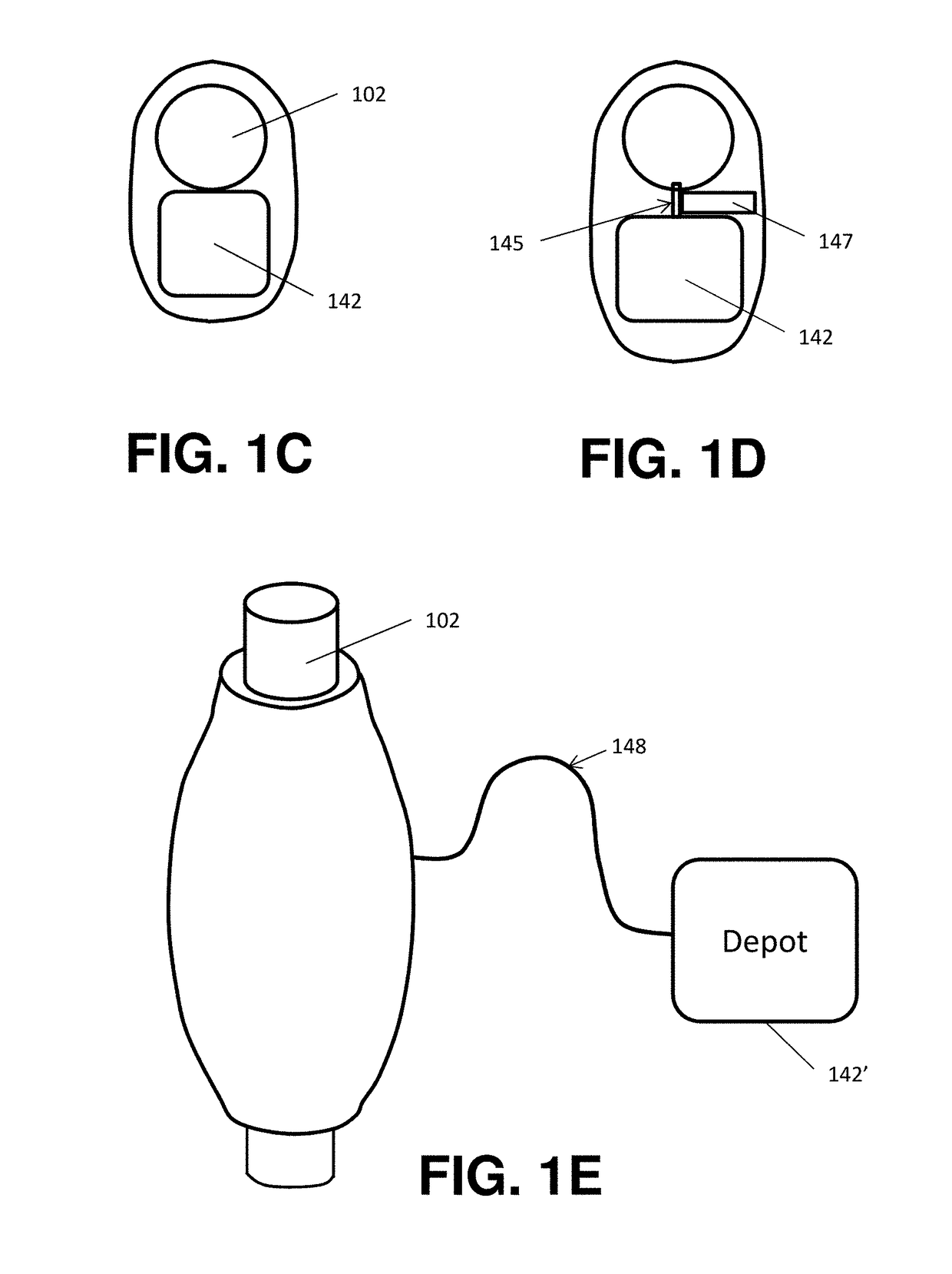

Systems and methods for establishing a nerve block

ActiveUS20170197076A1Improve accurate timeImprove clock accuracySpinal electrodesMedical devicesNerve cuffControlled delivery

A nerve cuff for establishing a nerve block on a nerve can have a cuff body with a channel for receiving a nerve, a reservoir for holding a drug, and an elongate opening slit extending the length of the cuff body that can be opened to provide access to the channel and can be closed to enclose the cuff body around the nerve. The nerve cuff can also include an electrode for detecting and measuring electrical signals generated by the nerve. A controller can be used to control delivery of the drug based on the electrical signals generated by the nerve.

Owner:SETPOINT MEDICAL CORP

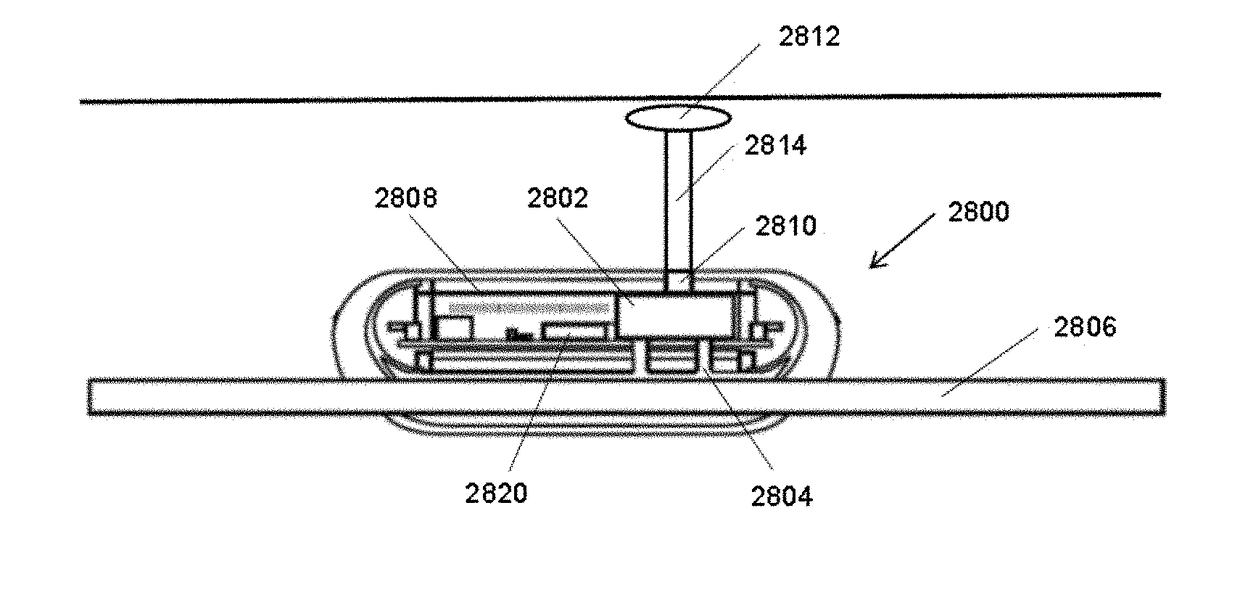

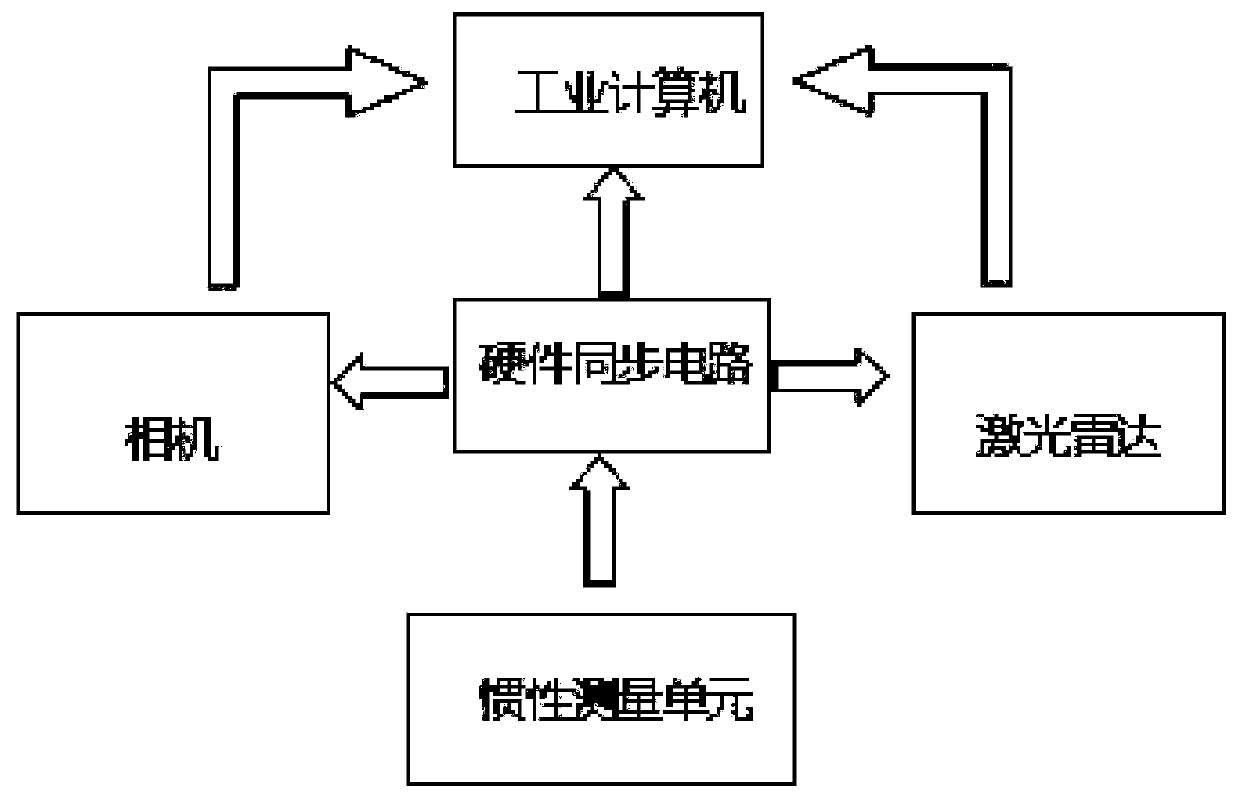

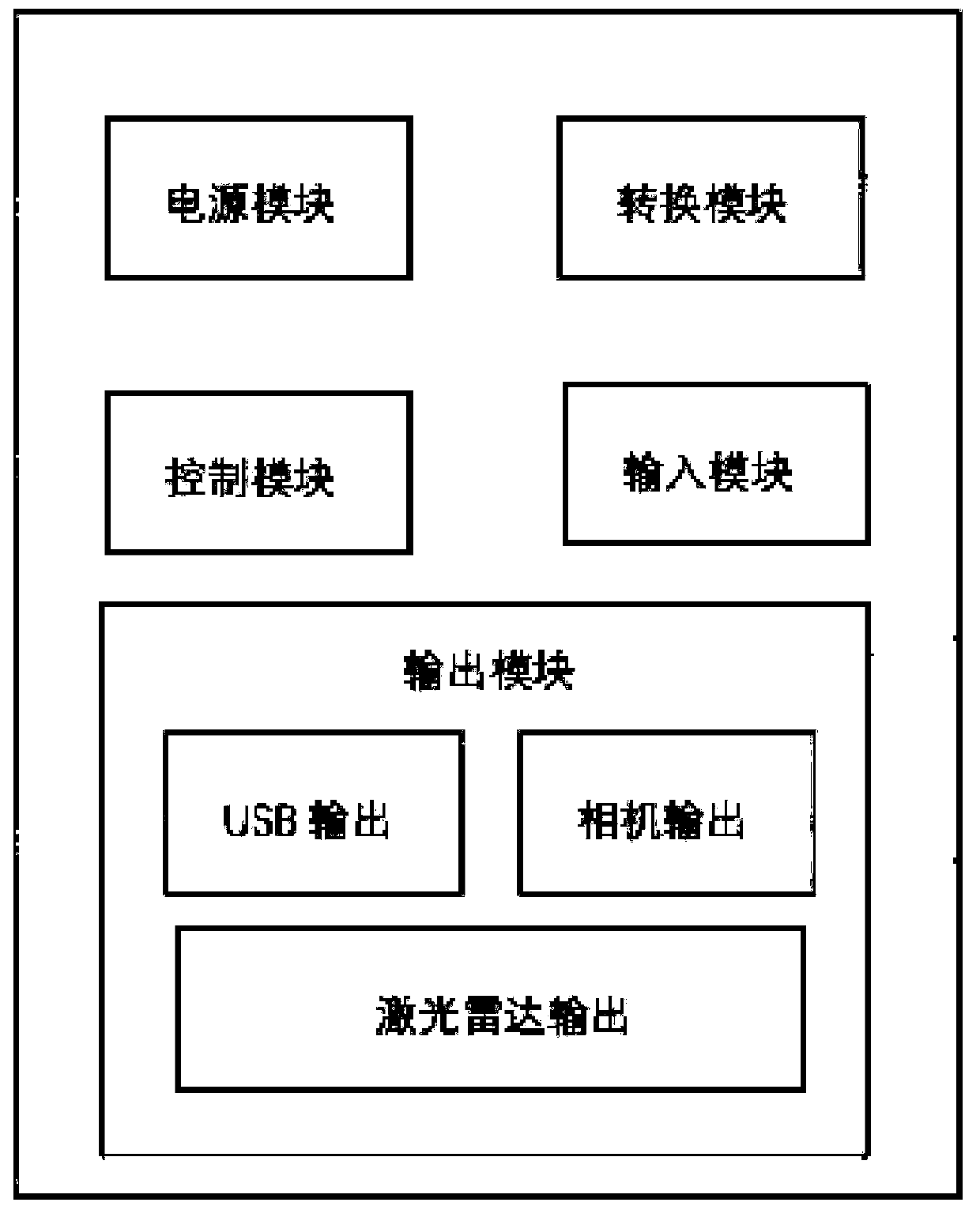

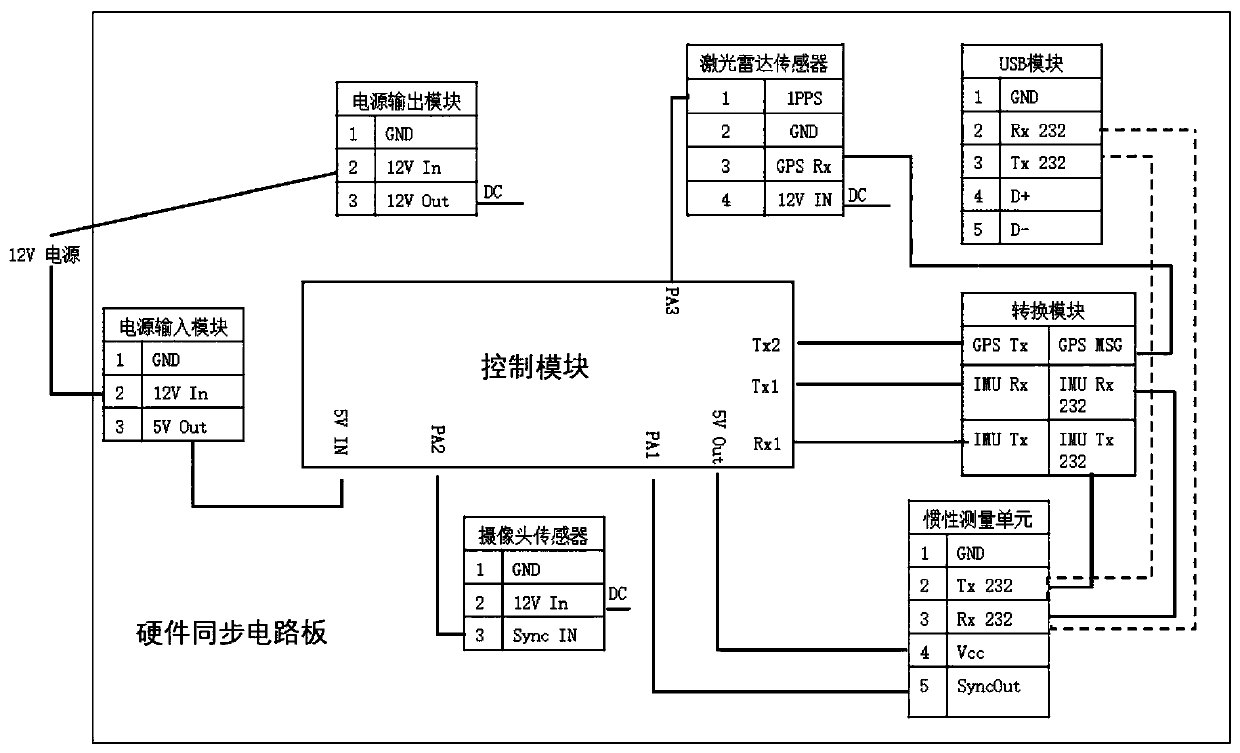

Method and device for unmanned acquired data synchronism

ActiveCN110329273ARich varietyRich typeNavigational calculation instrumentsNavigation by speed/acceleration measurementsData synchronizationData information

The invention discloses a method and device for unmanned acquired data synchronism. An unmanned vehicle is provided with at least one inertia measuring unit (IMU), a laser radar sensor and a camera sensor, at least one industrial computer and a hardware synchronous circuit board. The method comprises the steps that the hardware synchronous circuit board obtains collected data information in the atleast one inertia measuring unit and pulse signals of a certain frequency sent by the sensors, and after the frequency of the obtained pulse signals sent by the inertia measuring unit is lowered to apreset value, the pulse signals are sent to the laser radar sensor. The signals are processed by adopting a hardware circuit, due to the fact that the hardware body adopts a controller with the highclock precision, the time difference between data generated by the hardware body is in the microsecond level, the synchronous precision is high, modularized functional units are adopted, the modules are integrated on the small space, the integration level is high, the size is small, and the modules can be easily transplanted into different unmanned systems.

Owner:ZHEJIANG UNIV

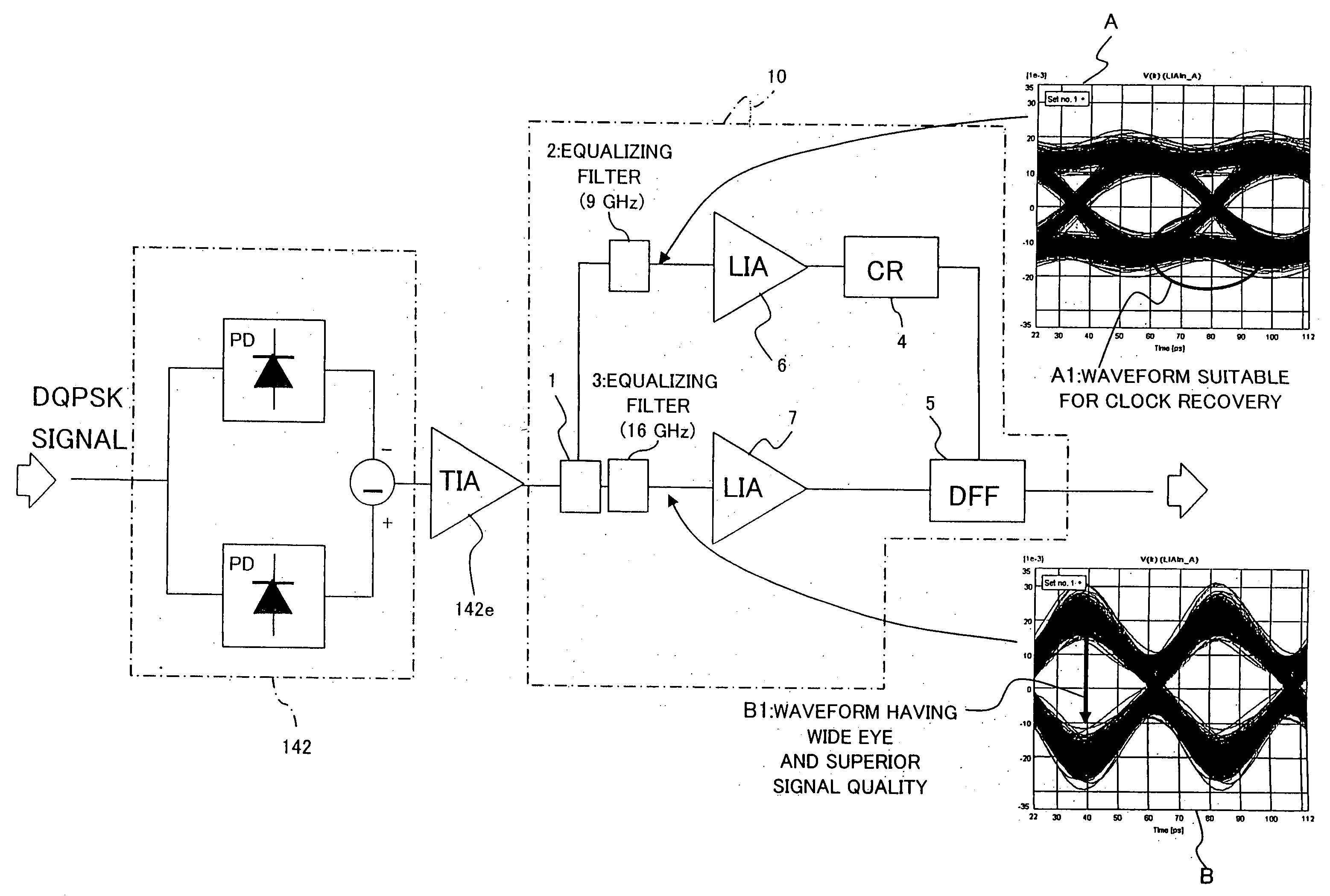

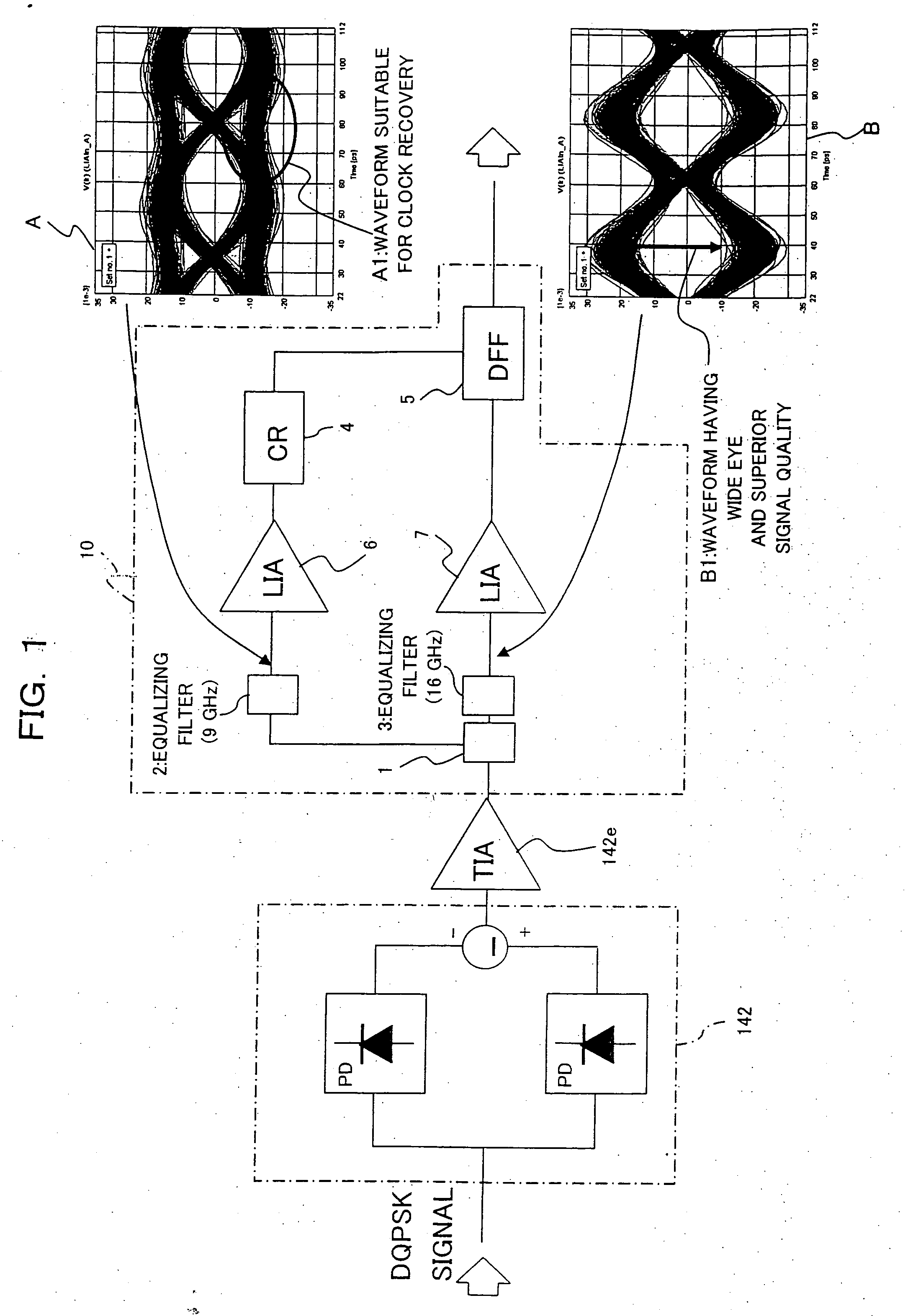

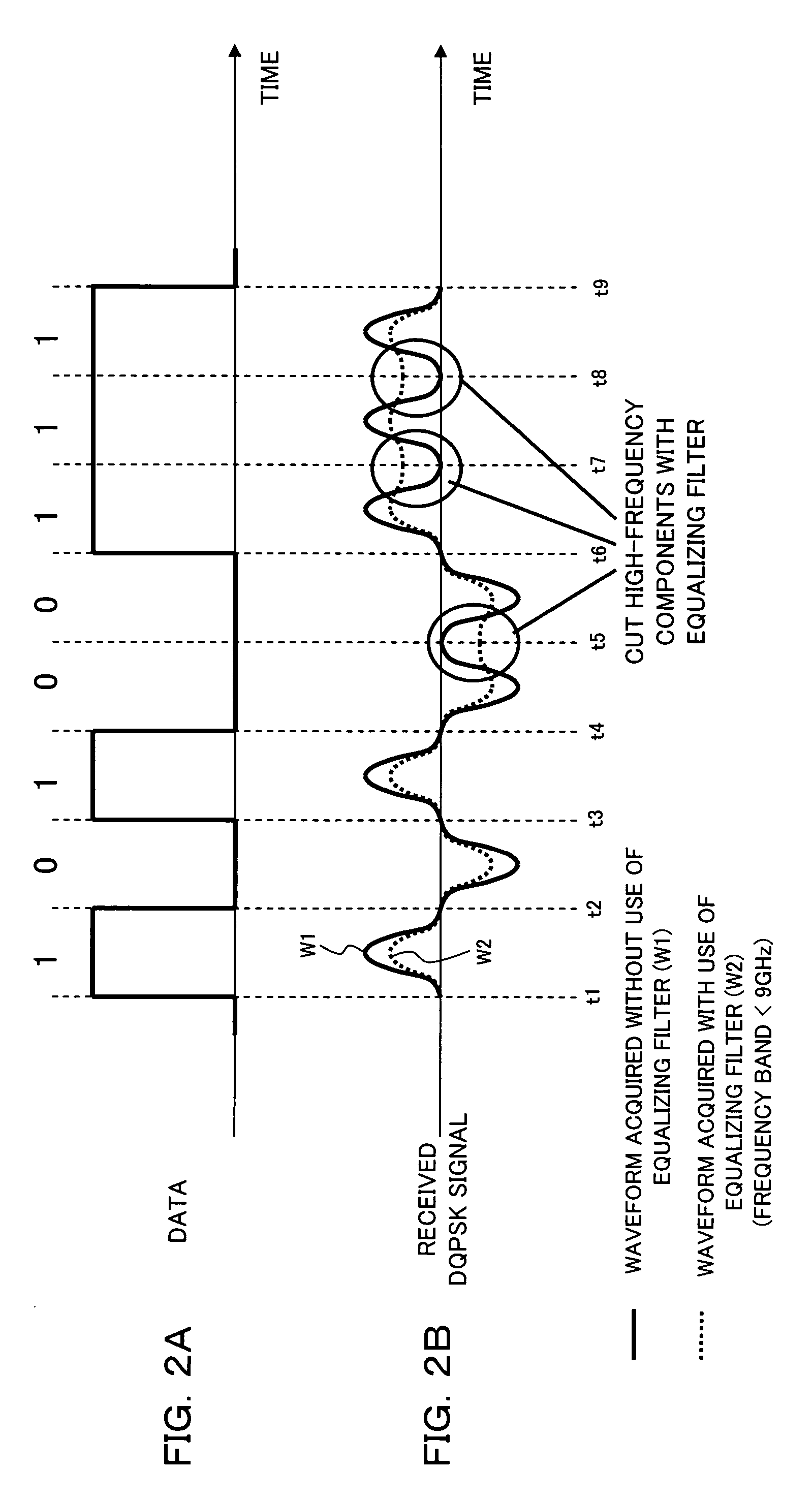

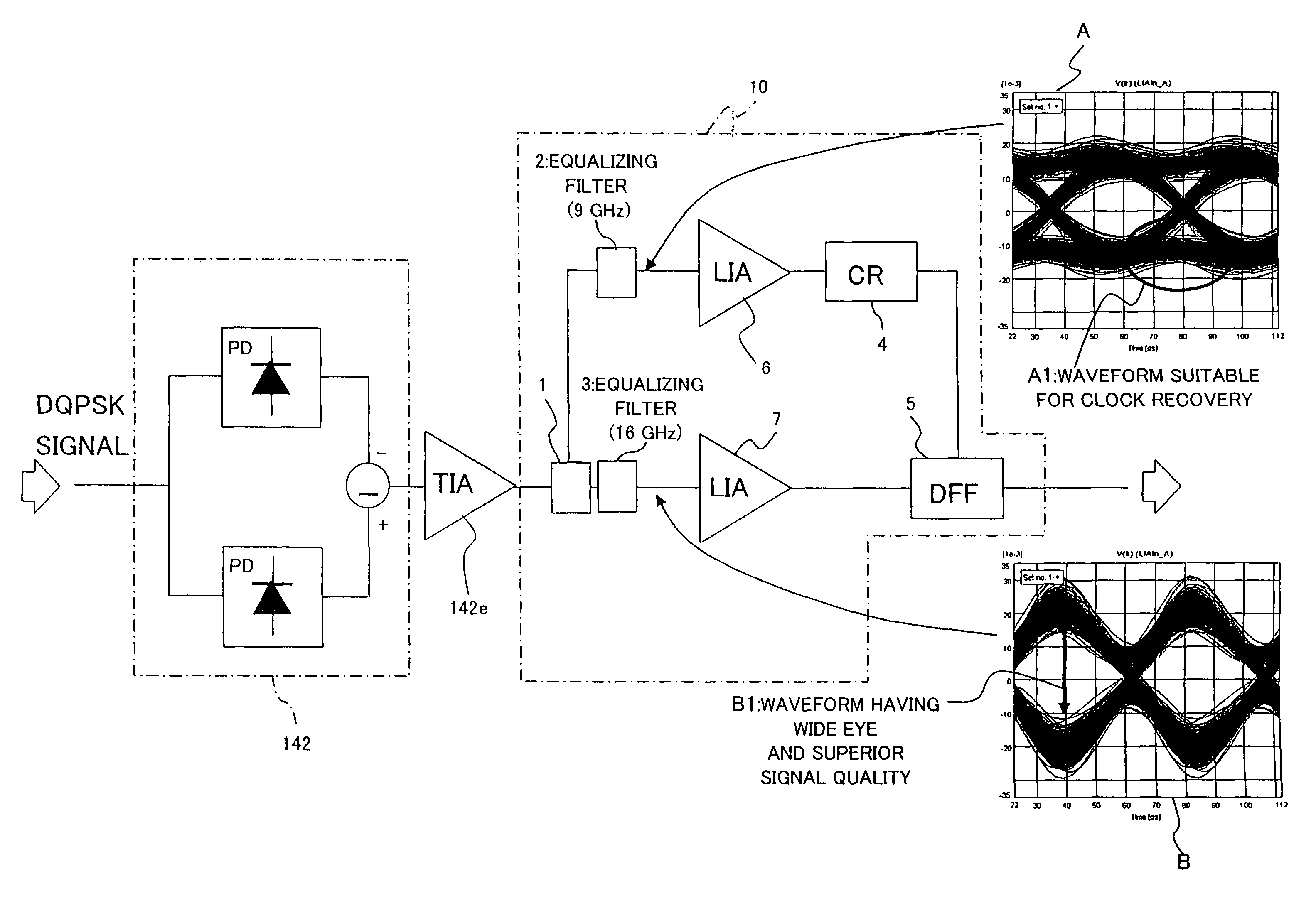

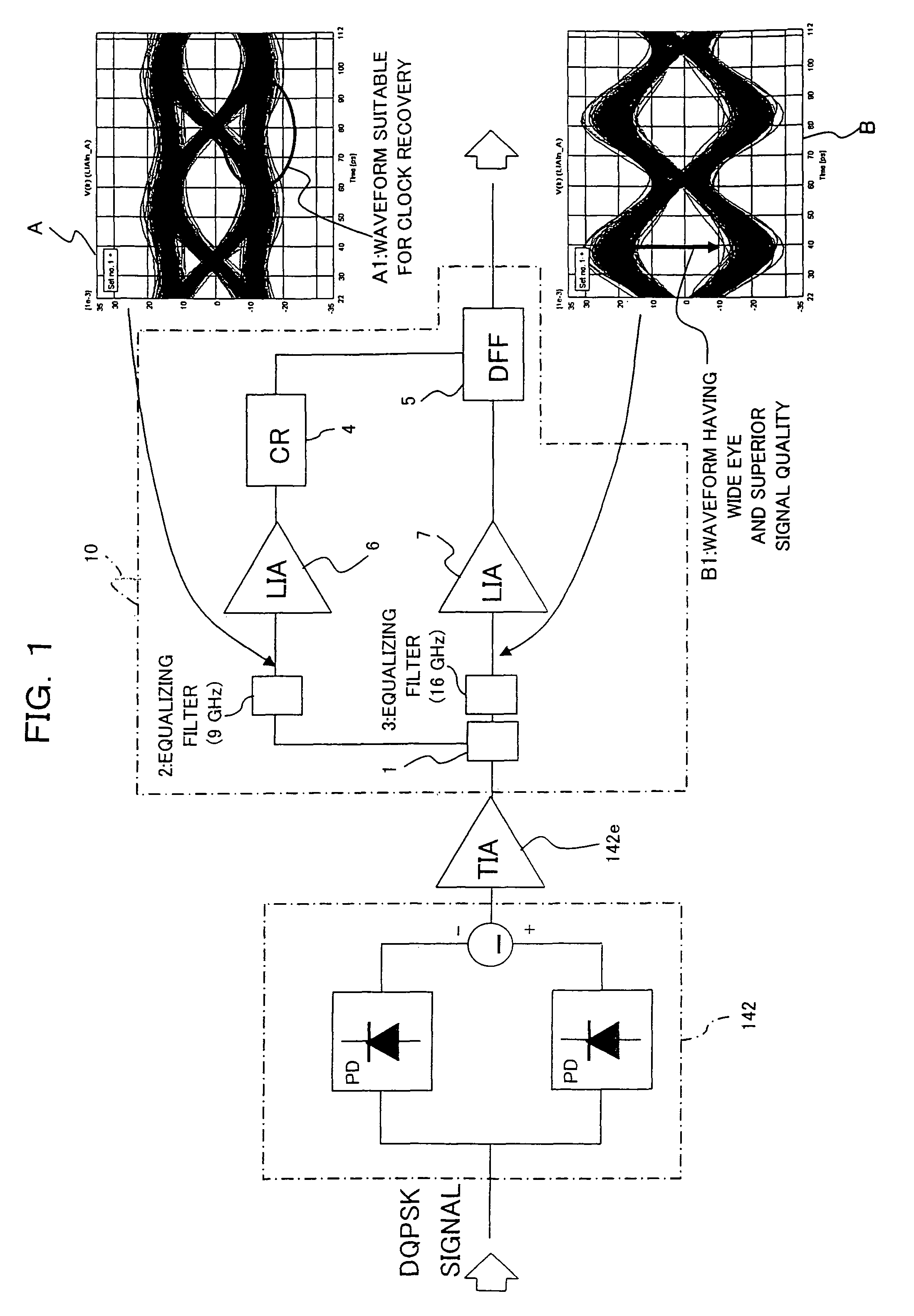

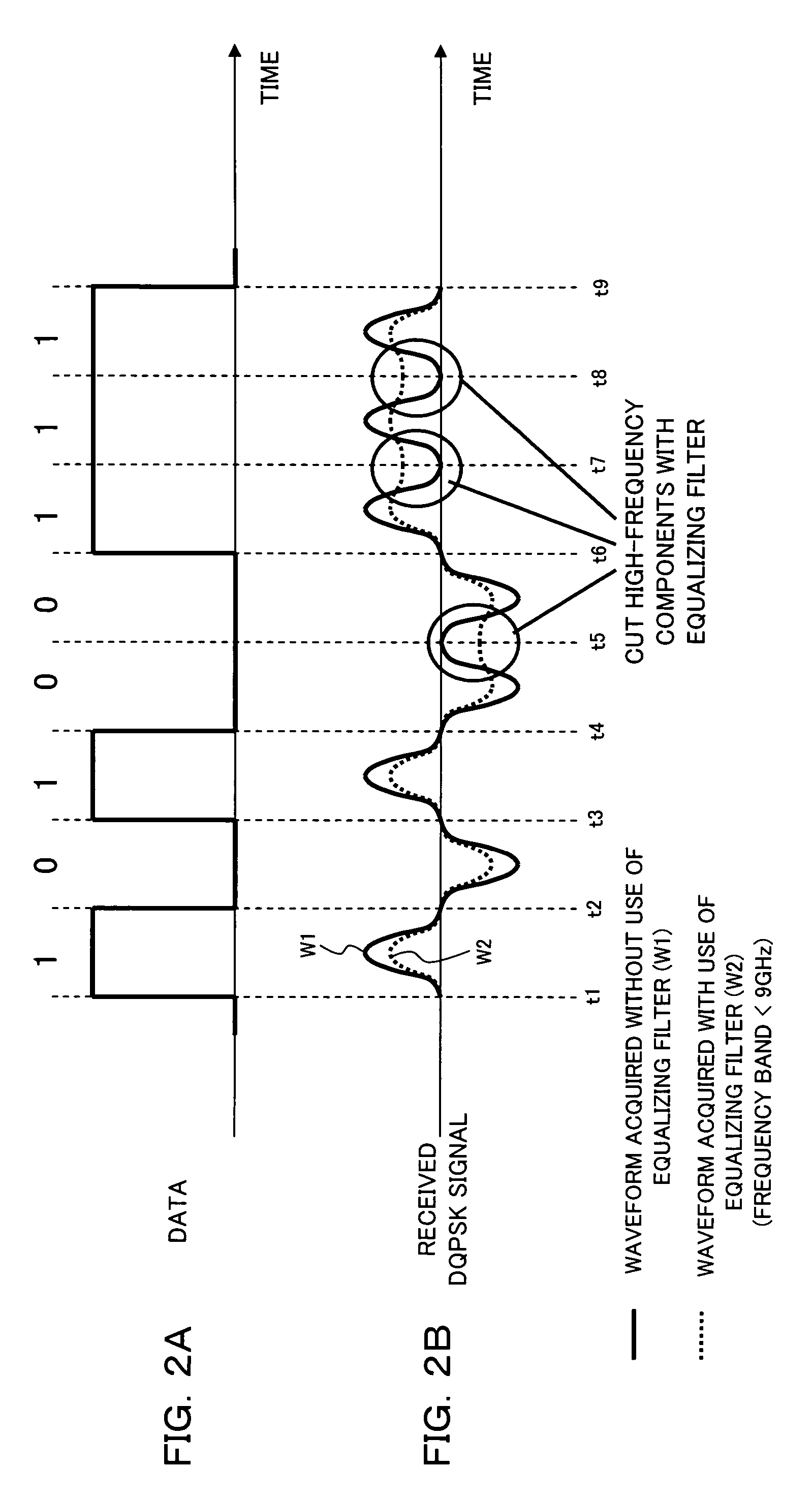

Signal regeneration device, optical receiver, and signal processing method

InactiveUS20070127929A1Improve clock accuracyImprove receiver sensitivityEqualisersPhase-modulated carrier systemsDifferential phaseData signal

A signal regeneration device which makes an extracted clock signal highly accurate while maintaining superior receiving sensitivity. To this end, a device of the present invention is configured to have a branch section for branching an input electrical signal which has been demodulated from a differential phase-shift modulated state; a first filter for equalizing a waveform of one of the demodulated electrical signals branched by the branch section; a clock recovery section for recovering a clock signal from the demodulated electrical signal whose waveform has been equalized by the first filter; and a data regeneration section for regenerating a data signal from a remaining one of the demodulated electrical signals branched by the branch section and from a clock signal recovered by the clock recovery section.

Owner:FUJITSU LTD

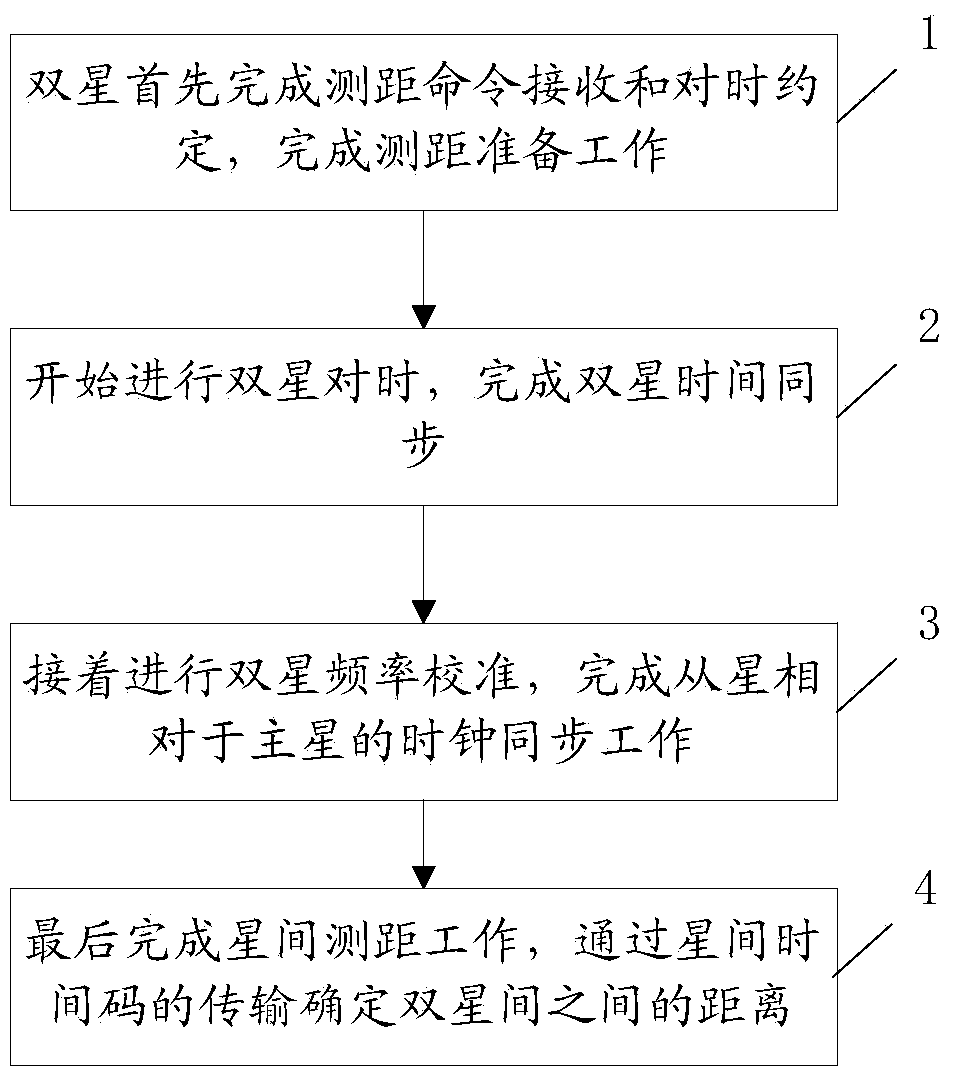

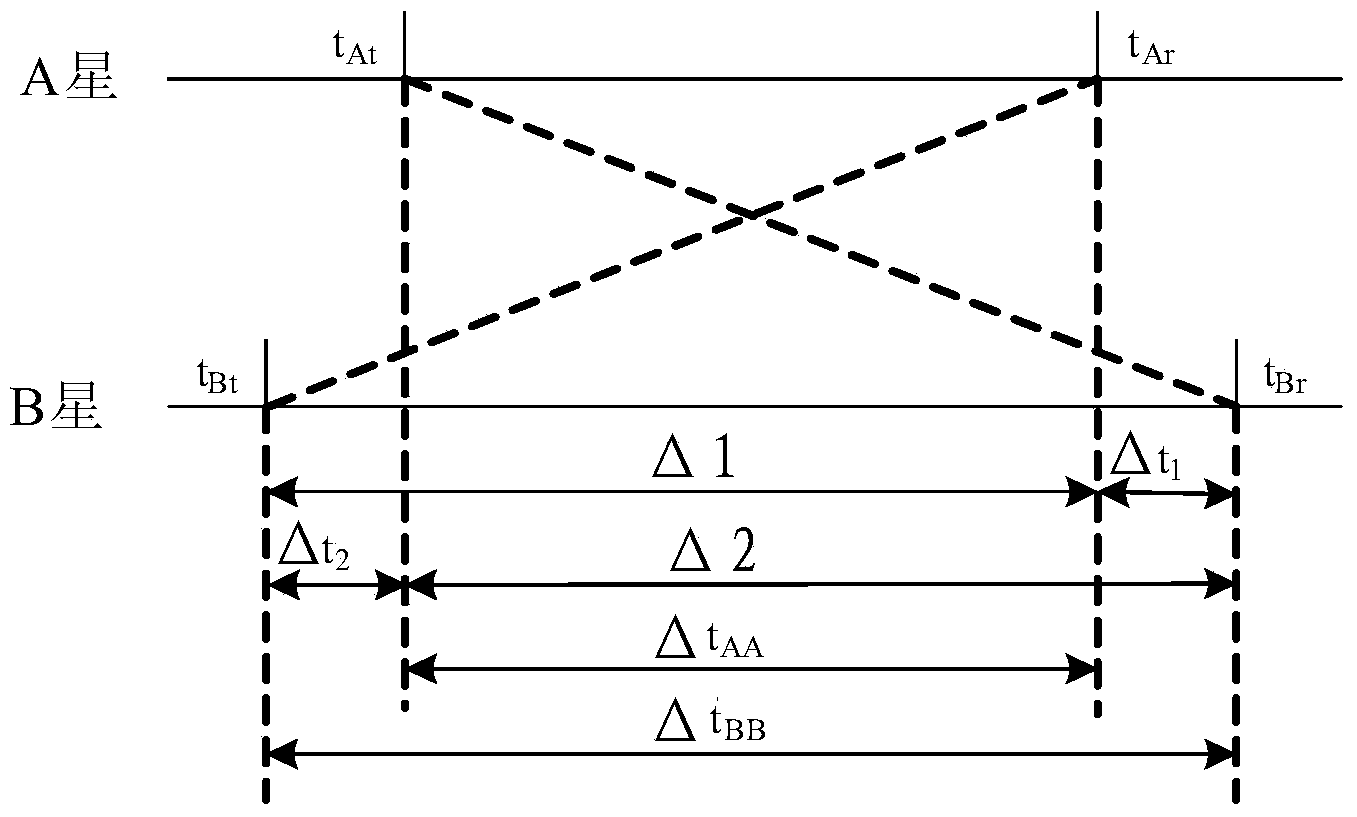

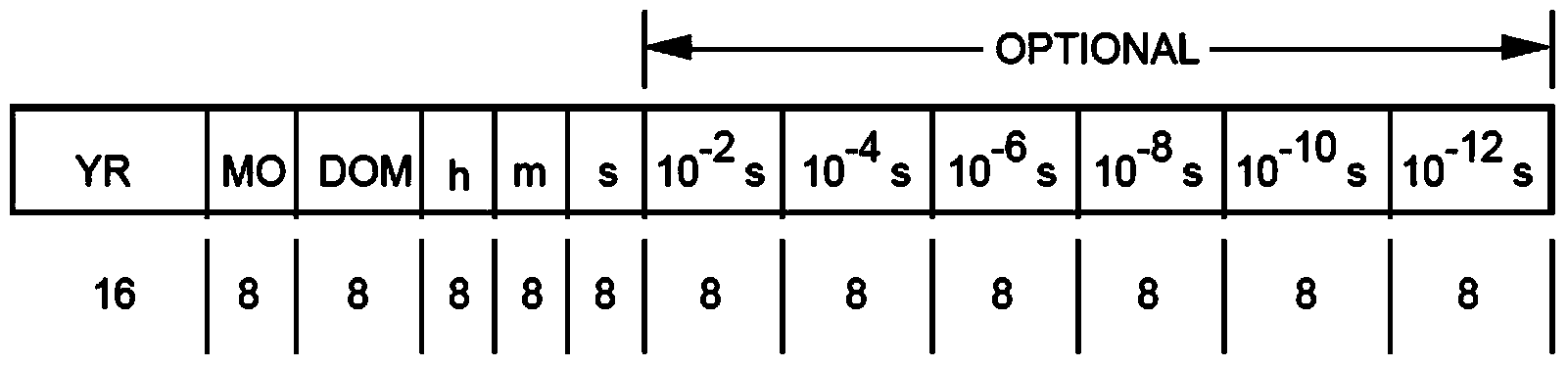

Inter-satellite ranging method based on dual-satellite time synchronization

ActiveCN103675804AHigh frequencyImprove clock accuracyRadio wave reradiation/reflectionClock rateTwo step

The invention discloses an inter-satellite ranging method based on dual-satellite time synchronization. On the basis of not depending on GPS, ranging accuracy can be raised, and present ranging requirements can be met. Firstly, a main satellite and a following satellite make an appointment for time setting. At the moment of time setting, time synchronization of dual-satellite is carried out. After time synchronization, dual-satellite clock frequency synchronization is carried out. After the two steps of synchronization are finished, the dual satellites operate under the clock after the synchronization, and the distance between the dual satellites is determined through inter-satellite timing code transmission.

Owner:NO 513 INST THE FIFTH INST OF CHINA AEROSPACE SCI & TECH

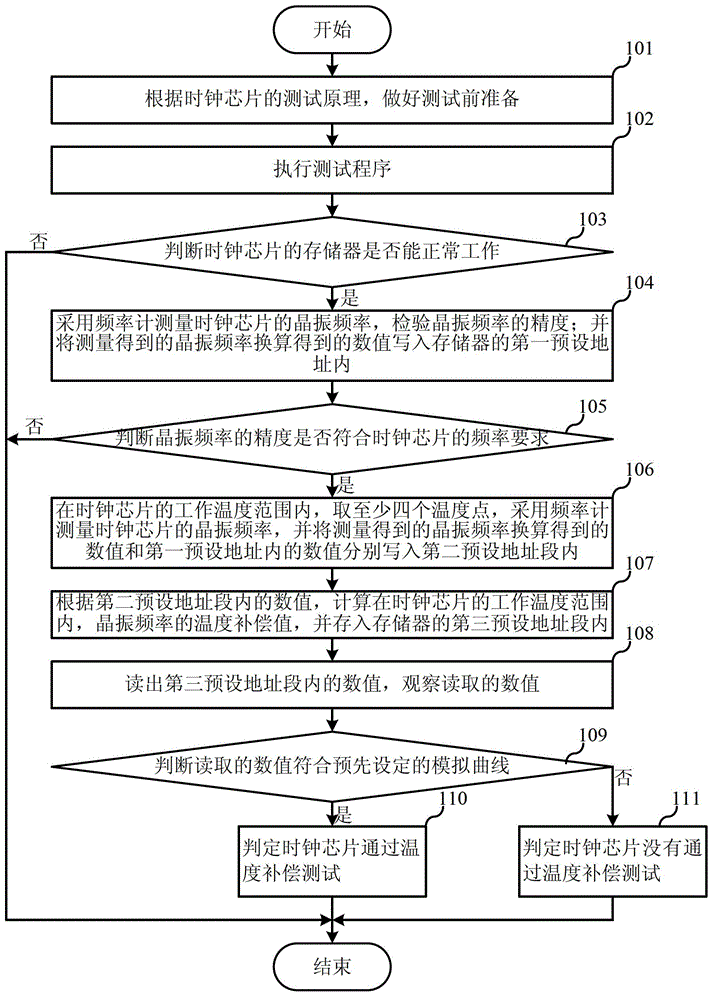

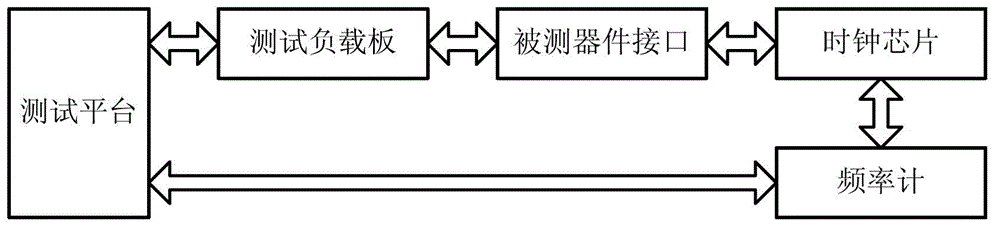

Testing method and system of clock chip

ActiveCN104035021AIncrease temperatureImprove clock accuracyElectronic circuit testingFrequency measurement arrangementIntegrated circuitOperating temperature range

The invention, which relates to the integrated circuit testing field, discloses a testing method and system of a clock chip. According to the invention, on the basis of the clock chip testing principle, a testing load plate and a tested device interface are designed and arranged. When the memory of the clock chip works normally, the precision of the crystal oscillator frequency can be tested; a high-precision frequency meter is used for measuring the crystal oscillator frequency in a working temperature range of the clock chip; a temperature compensation value of the crystal oscillator frequency in the working temperature range of the clock chip is calculated according to the measuring value and is stored into the memory of the clock chip; and the temperature compensation value is read, and when the read value meets a predetermined simulated curve, that the clock chip passes the temperature compensation test successfully is determined. Therefore, temperature compensation testing is realized in a wide temperature range from minus 40 DEG C to 85 DEG C for the crystal oscillator frequency of the clock chip; and the clock precision is improved.

Owner:NANJING MACROTEST SEMICON TECH CO LTD

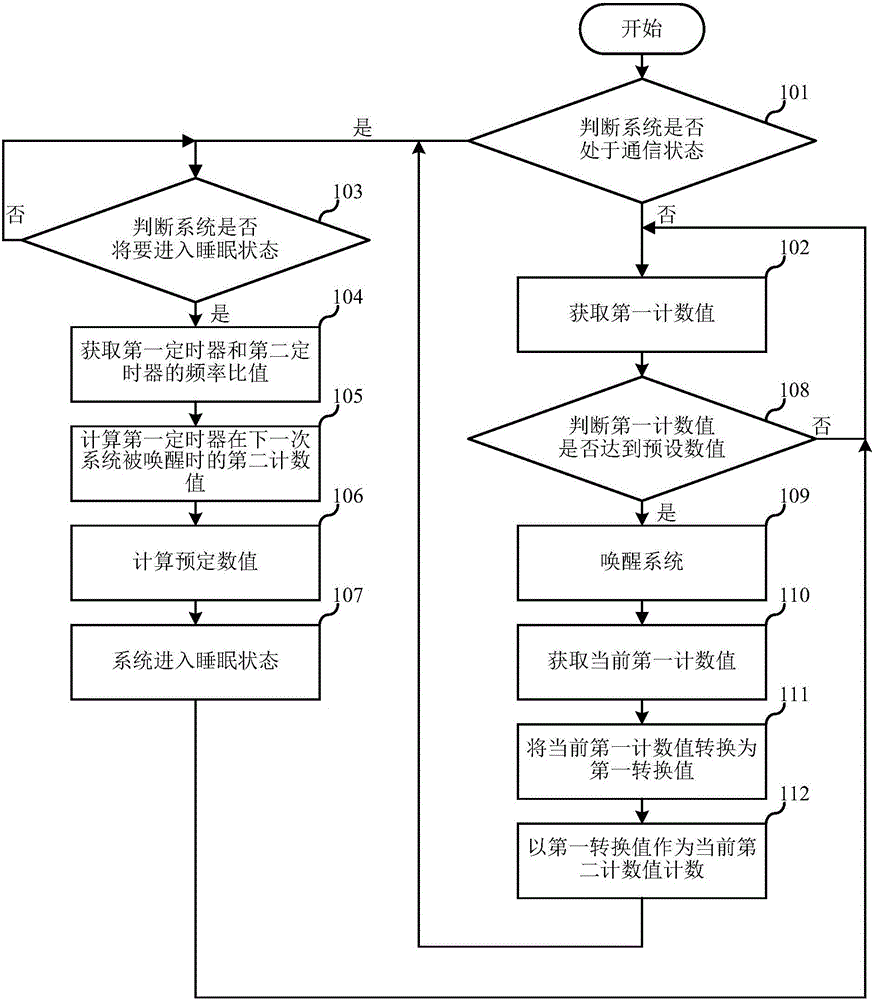

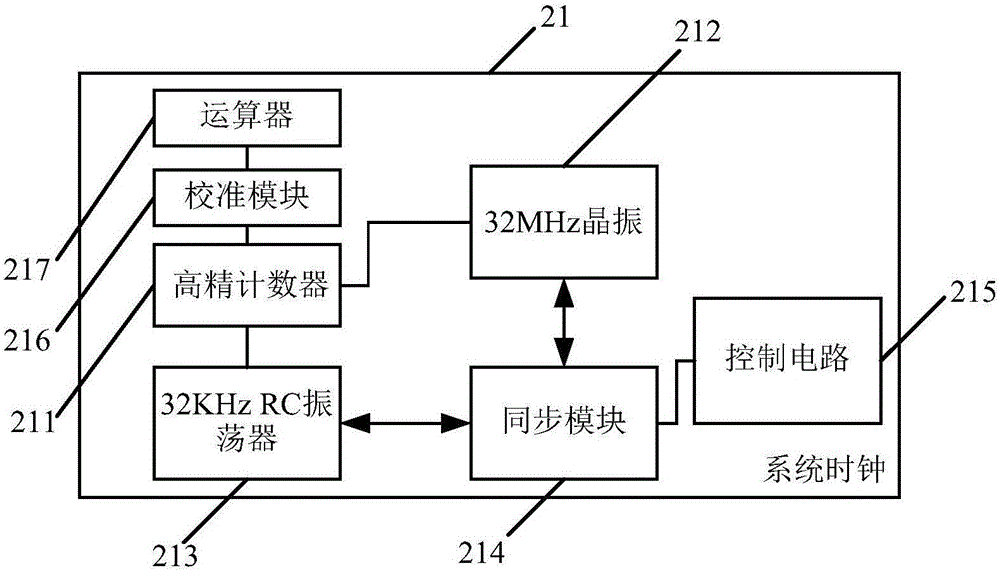

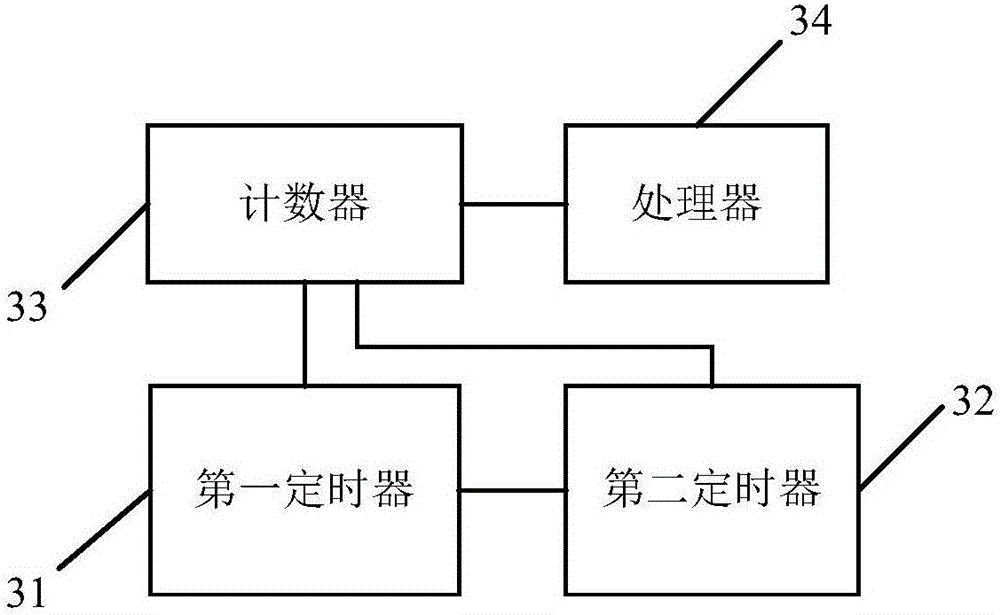

System clock

InactiveCN106227293AHigh precisionReduce power consumptionPower supply for data processingGenerating/distributing signalsIntegrated circuitPower consumption

The invention relates to the integrated circuit field, and discloses a system clock; the system clock comprises a first timer and a second timer, wherein the first timer is higher in precision than the second timer; the second timer continuously counts, and the count value of the second timer is the first count value; the first time counts when the system is in a communication status, and the count value of the first timer is the second count value; when the first count value of the second timer reaches a preset value, the system is waken up; when the system is waken up, the first timer can convert the present first count value into a first conversion value according to the frequencies of the first and second timers; the first conversion value can serve as the present second count value for continuous counting. The system clock can improve clock precision, and can limit system power consumption, thus reducing cost.

Owner:TELINK SEMICON SHANGHAI

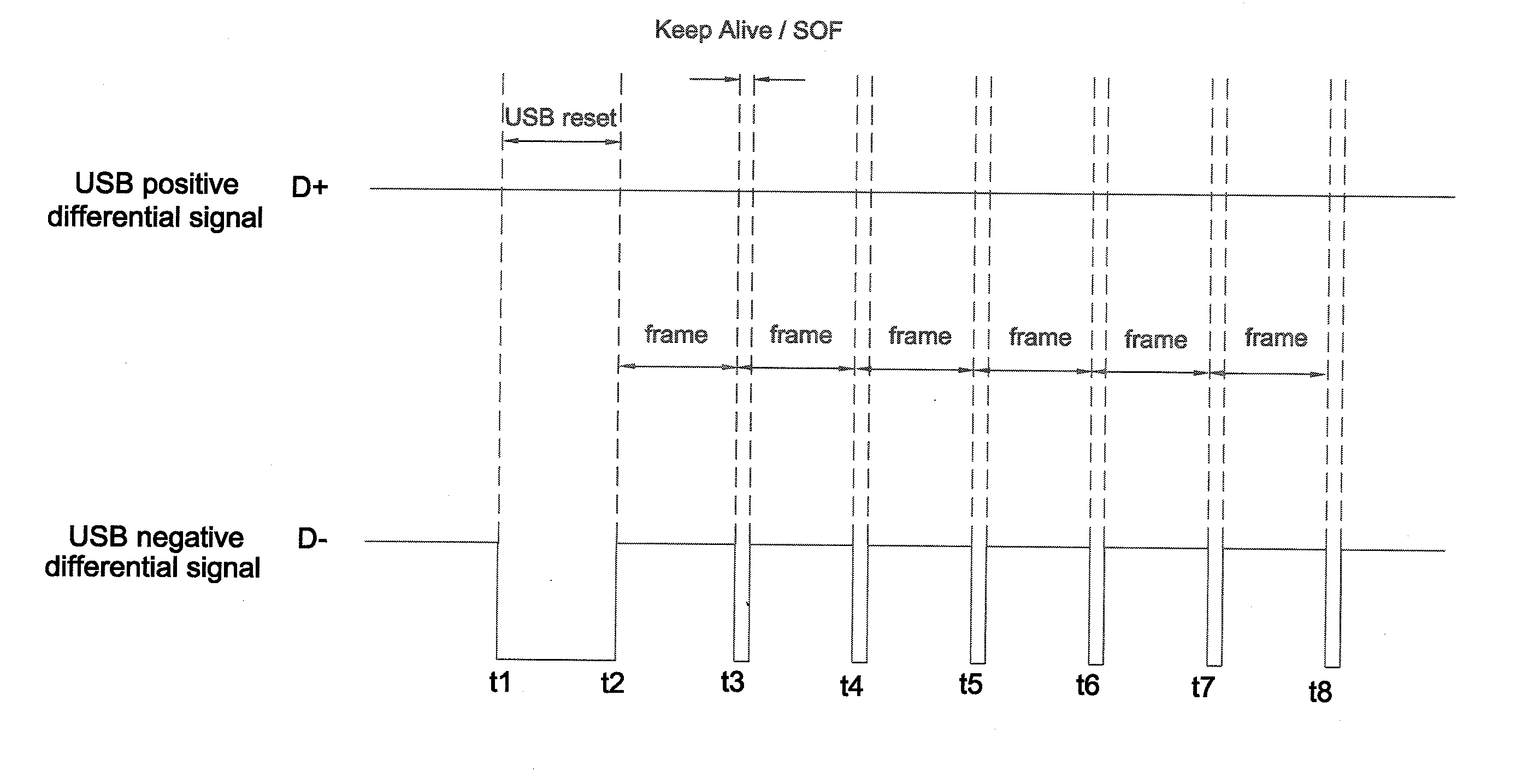

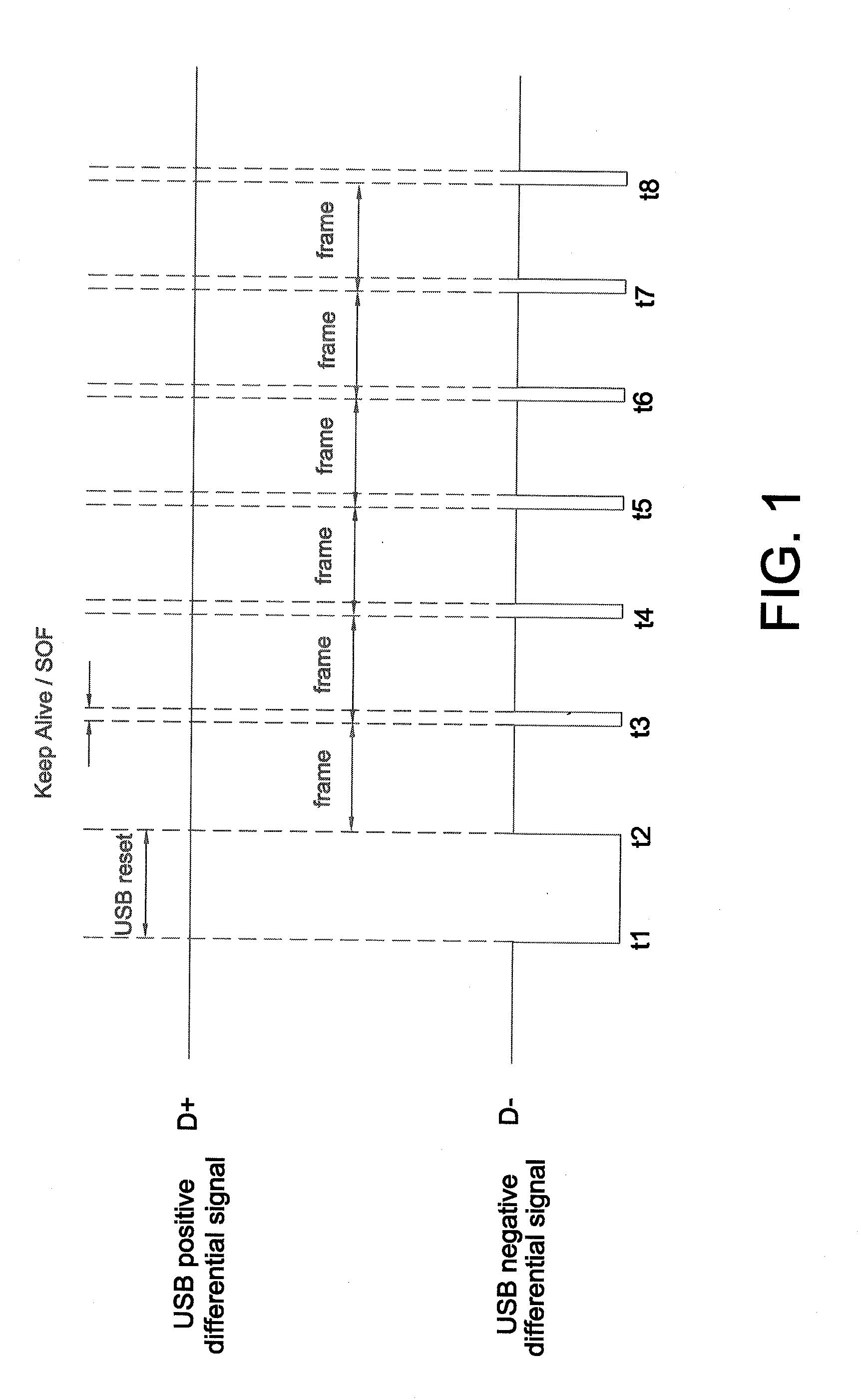

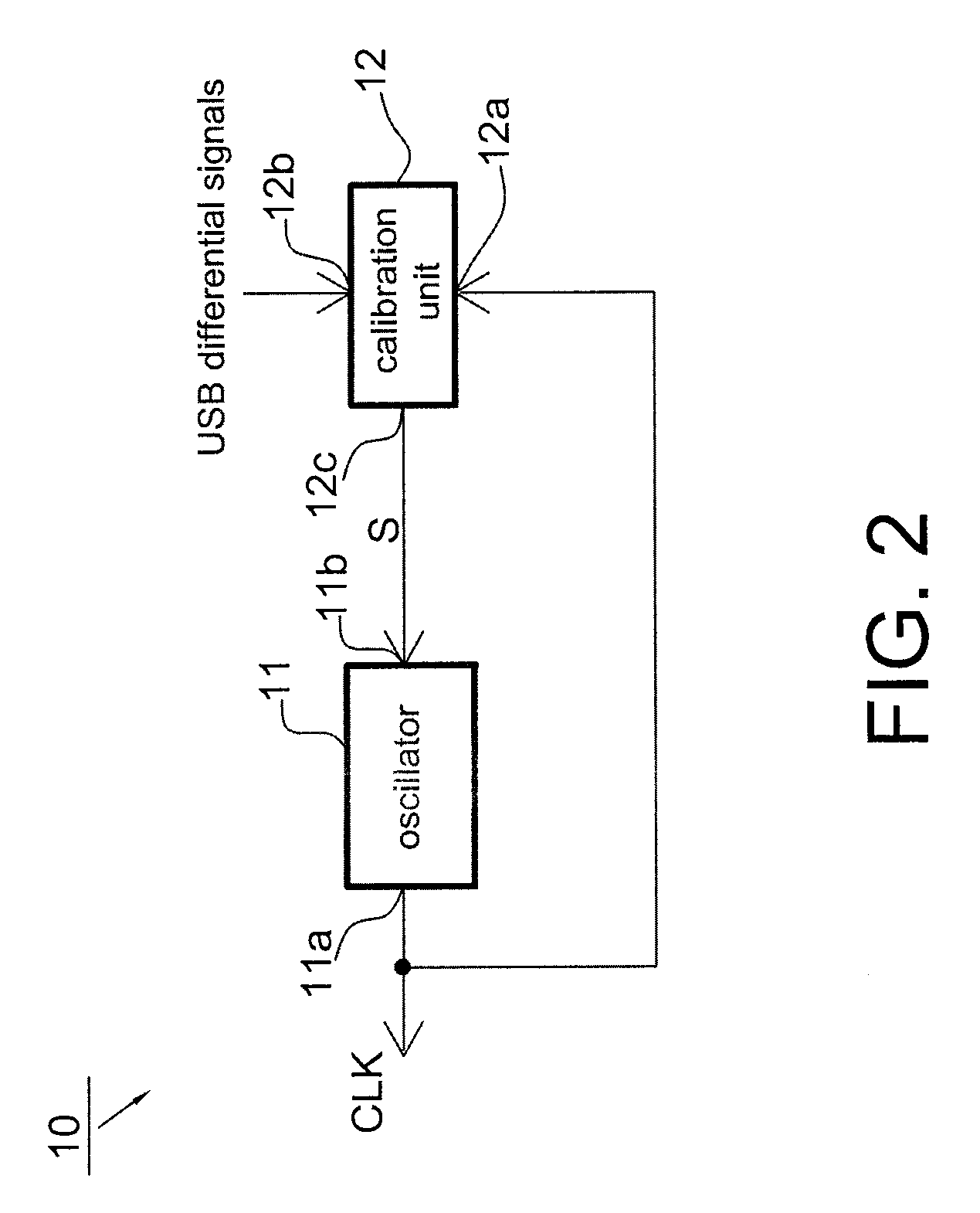

Clock frequency adjusting circuit and clock frequency adjusting method thereof

InactiveUS20120051479A1Improve clock accuracySmall sizeGenerating/distributing signalsSynchronising arrangementClock ratePhase difference

A clock frequency adjusting method includes the steps of: calculating a phase difference between a local signal and SOF signals or EOP signals in an external signal; counting a count value of the phase difference based on a clock frequency of a local oscillator; and adjusting the clock frequency according to the count value. The present invention further provides a clock frequency adjusting circuit.

Owner:PIXART IMAGING INC

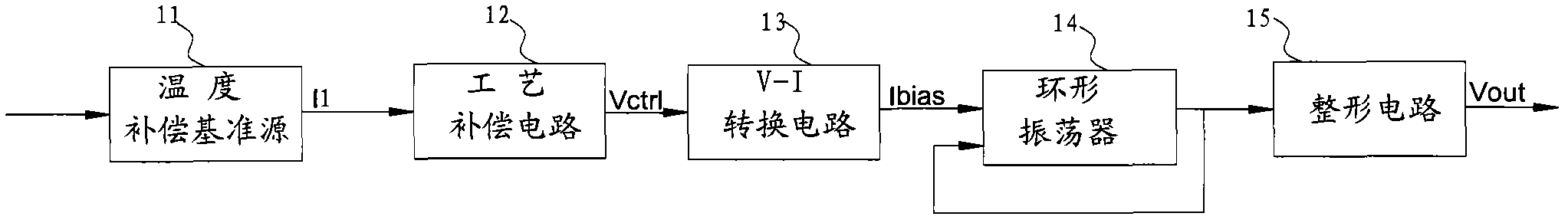

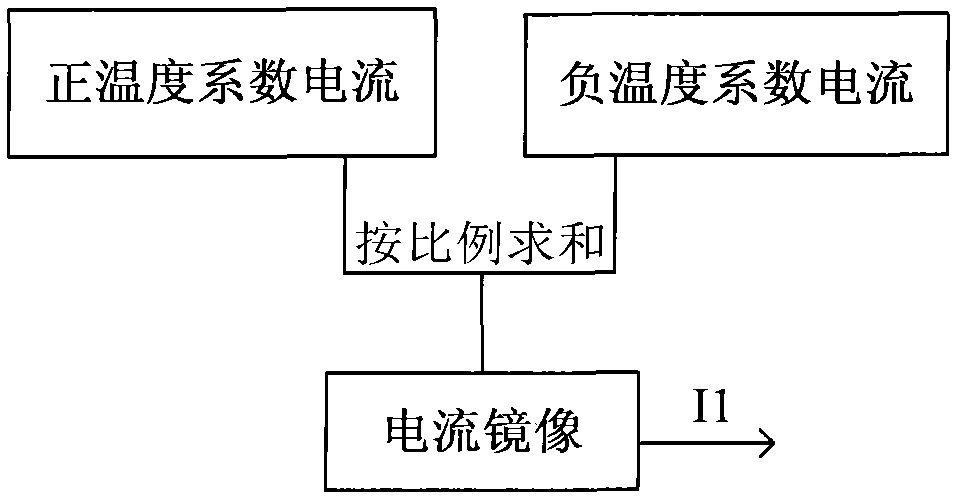

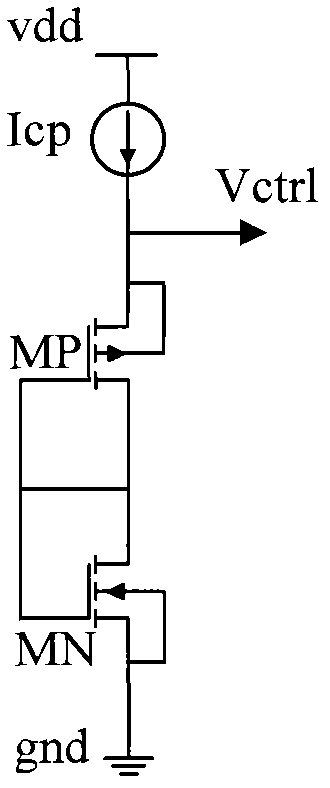

All-silicon clock generator realized on basis of complementary metal oxide semiconductor (CMOS) process

InactiveCN102064801ASimple structureImprove clock accuracyElectric pulse generatorElectric variable regulationPower flowEngineering

The invention relates to an all-silicon clock generator realized on the basis of a complementary metal oxide semiconductor (CMOS) process. The all-silicon clock generator comprises a temperature compensation current source, a process compensation circuit, a V-I conversion circuit, a loop oscillating circuit and a shaping circuit the output ends of which are sequentially connected, wherein the temperature stabilizing current source is used for providing current after temperature compensation; the process compensation circuit is used for providing voltage for reducing the deviation of the CMOS process; the V-I conversion circuit is used for converting the compensated voltage to current output; the loop oscillating circuit generates clock signals with the corresponding frequency according tothe magnitude of the received current; and the shaping circuit is used for shaping the clock signals and outputting after frequency division. The invention adopts the temperature and process compensation circuits, thus ensuring that the CMOS clock circuit has favorable temperature and process stabilities and also has stronger power-supply rejection capacity. Besides, the circuit structure is simple, and the clock accuracy is high, so that the CMOS clock circuit can be substituted for a quartz crystal oscillator, a ceramic resonator and other circuits and used as a clock source.

Owner:SUZHOU R&D CENT OF NO 214 RES INST OF CHINA NORTH IND GRP

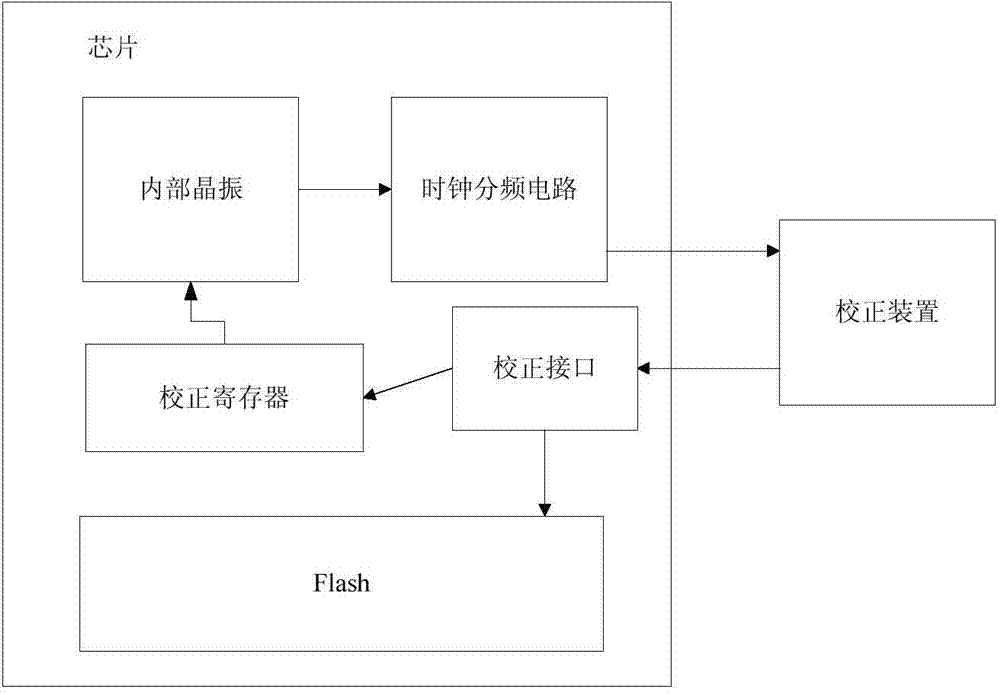

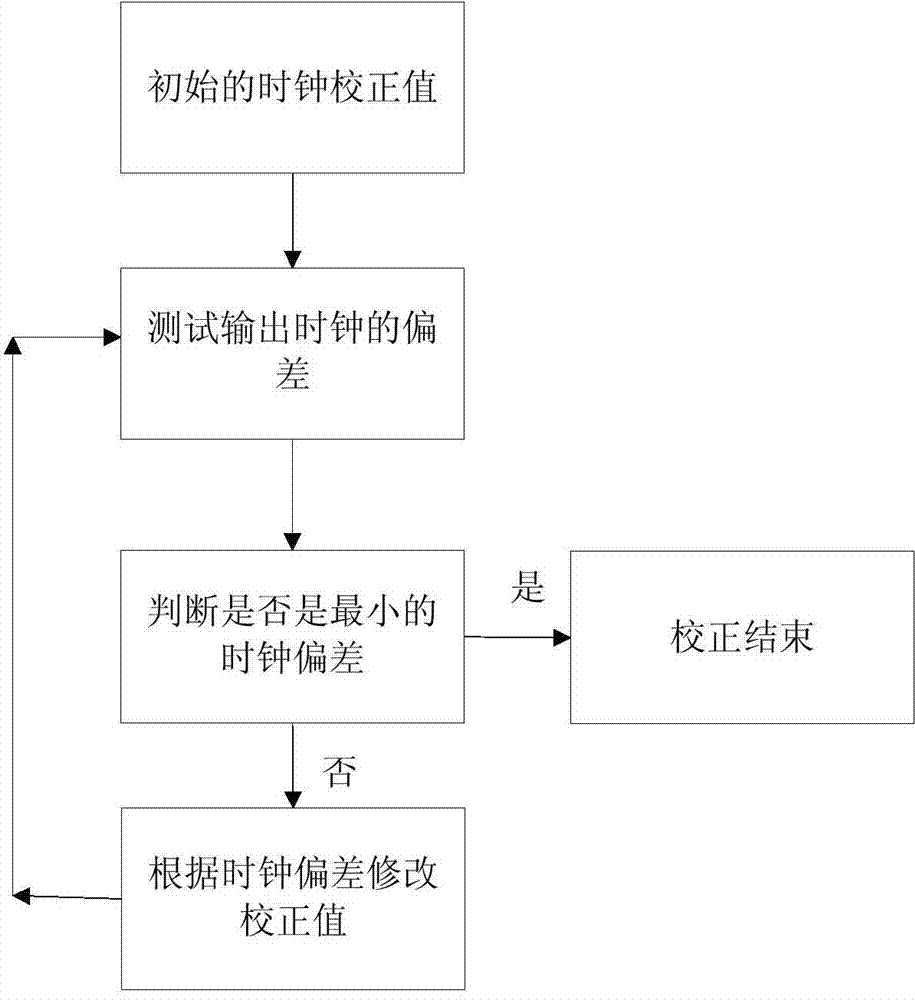

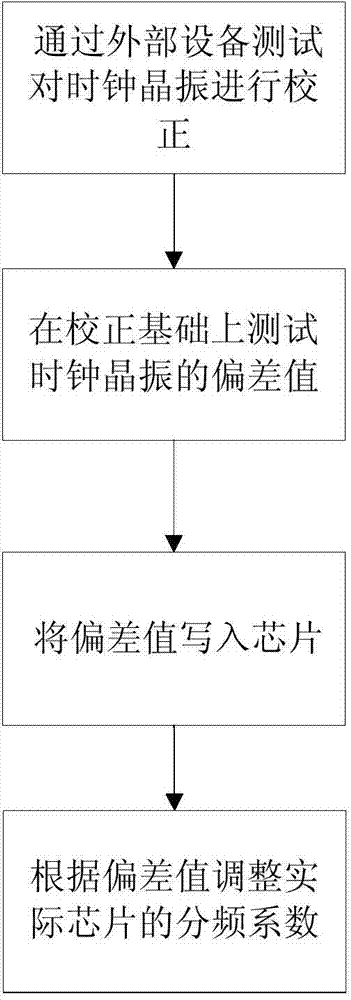

MCU chip frequency division clock correcting device and method

ActiveCN104122936AImprove clock accuracyGenerating/distributing signalsProcessor registerClock offset

The invention discloses an MCU chip frequency division clock correcting device and method. The device comprises a clock module, a clock frequency division circuit, a correcting register, a correcting interface, a storage device and a correcting device body, wherein the clock module, the clock frequency division circuit, the correcting register, the correcting interface and the storage device are arranged in a chip, and the correcting device body is arranged outside the chip. When a clock is corrected, the external correcting device body writes a correcting value into the correcting register through the correcting interface, the clock module adjusts the clock according to the correcting value, the clock is output through the clock frequency division circuit, the external correcting device body adjusts the correcting value according to the clock output until the correcting value with the minimum clock offset is found, the offset value with the actual frequency is worked out, and the correcting value and the clock offset are written into the chip internal storage device. According to the MCU chip frequency division clock correcting device and method, the offset value of a clock crystal oscillator is used for improving the clock accuracy, and the clock accuracy can be greatly improved on the basis of the accuracy of an existing clock oscillator. The accuracy limitation brought by the practice that a fixed correcting value is written in by an external device can be broken through, circuit upgrading does not need to be conducted on the chip, and an external crystal oscillator and an external IO are omitted.

Owner:CHIPSEA TECH SHENZHEN CO LTD

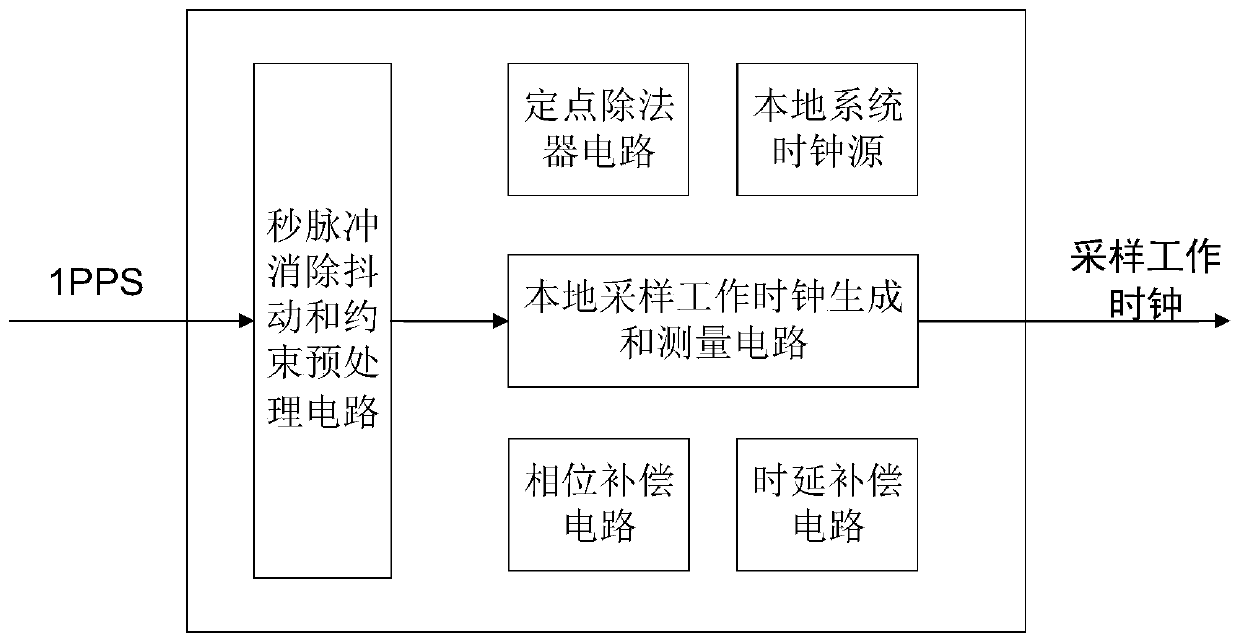

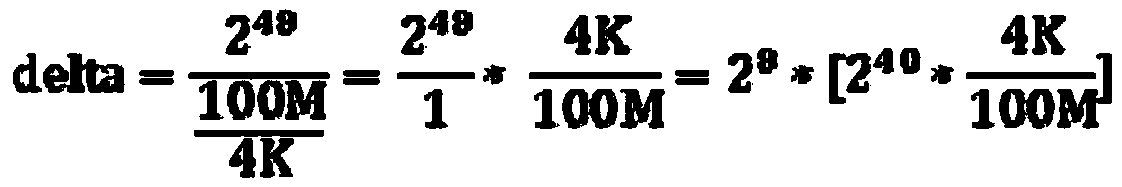

GNSS receiver pulse per second-based clock synchronization method

ActiveCN109765583AImprove clock accuracyImprove errorPulse automatic controlSatellite radio beaconingBit numberingMultiple pulse

The invention discloses a GNSS receiver pulse per second-based clock synchronization method. According to the method, a GNSS receiver pulse per second 1PPS signal is input to a de-bouncing and constraint preprocessing circuit so as to generate 1PPS anti-shake signals, thereby preventing multiple pulses per second in one second; the 1PPS anti-shake signals are counted by utilizing a first counter so as to obtain a practical frequency value of a system clock signal, and the practical frequency value is input into a fixed-point divider to obtain a cumulative step length of a second counter through formula operation; frequency division is carried out on the system clock signal through the second counter so as to generate a sampling work clock, the bit number of the second counter remains unchanged and the cumulative step length delta of the second counter is changed to change the frequency of a sampling work clock signal; phase compensation is carried out on the sampling work clock, and when each 1PPS anti-shake signal arrives, the sampling work clock is forcibly pulled up to ensure that the sampling work clock is aligned with the 1PPS anti-shake signals; and delay compensation is carried out on the sampling work clock. The method is capable of well solving the problem that accumulative errors of low-frequency sampling work clocks cause calculation results of real-time systems to be asynchronous with practical results.

Owner:北京知识产权运营管理有限公司

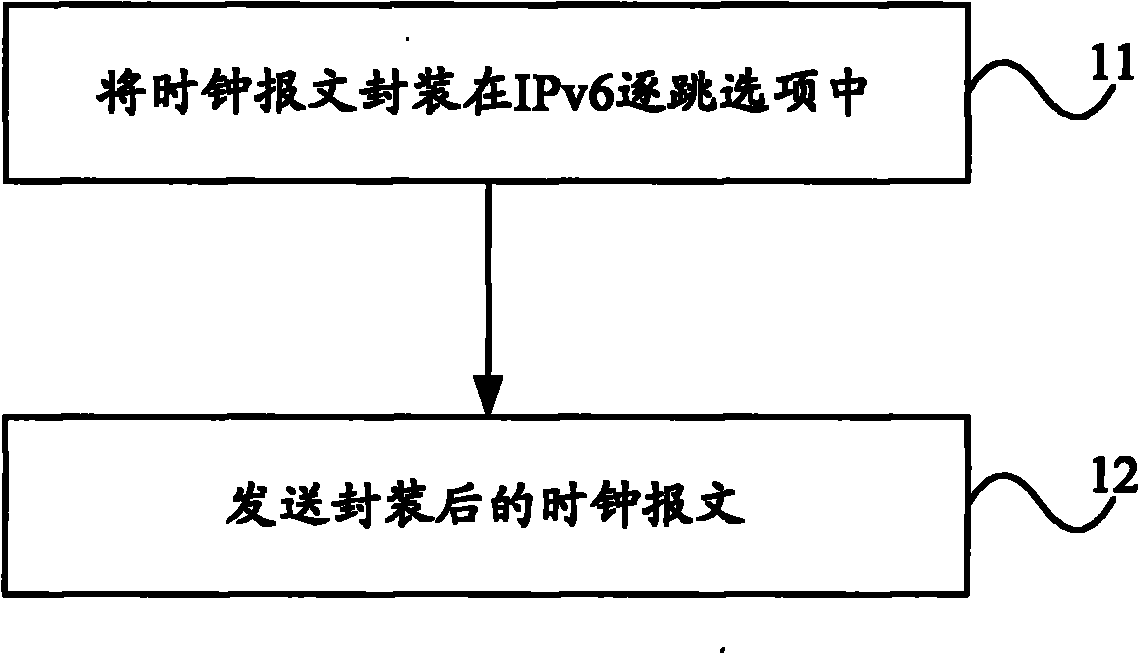

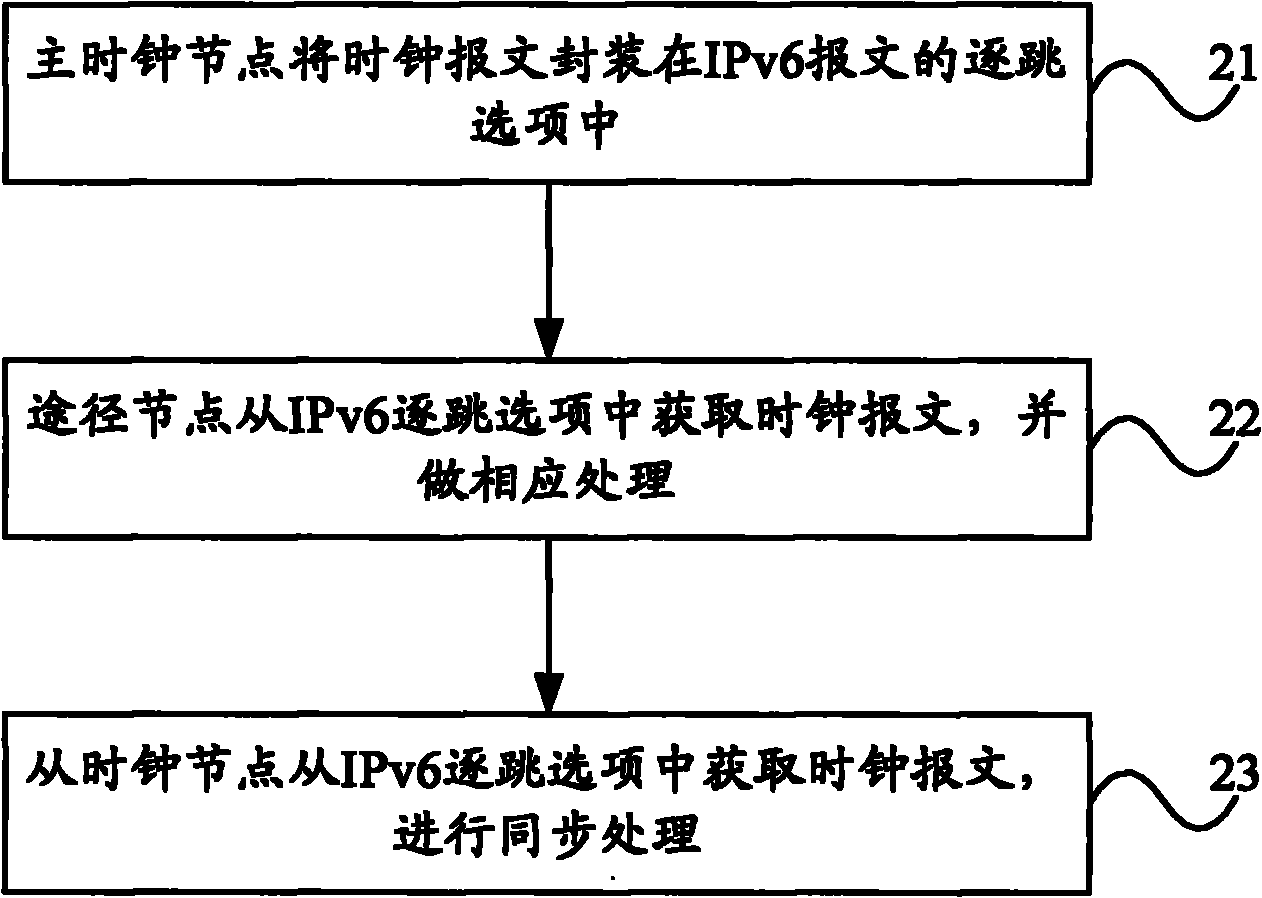

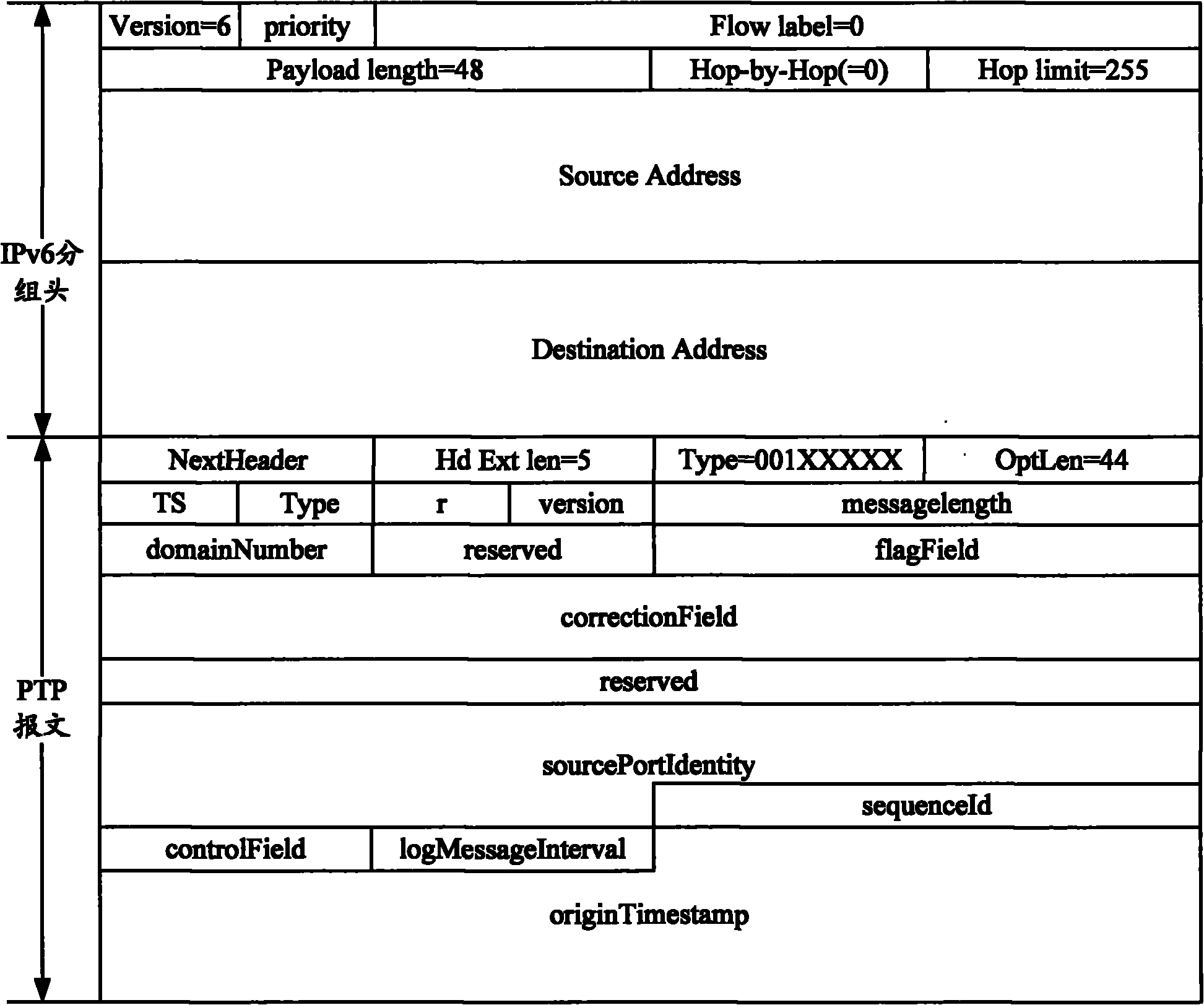

Method, device and system for processing clock message

InactiveCN102377663AImprove clock accuracyTime-division multiplexData switching networksComputer hardwareIPv6

The invention provides a method, a device and a system for processing a clock message. The method comprises: packaging the clock message in an IPv6 (internet protocol version 6) hop-by-hop option; and sending the packaged clock message. According to the technical scheme provided by the invention embodiment, the clock precision of synchronization can be improved according to the clock message.

Owner:HUAWEI TECH CO LTD

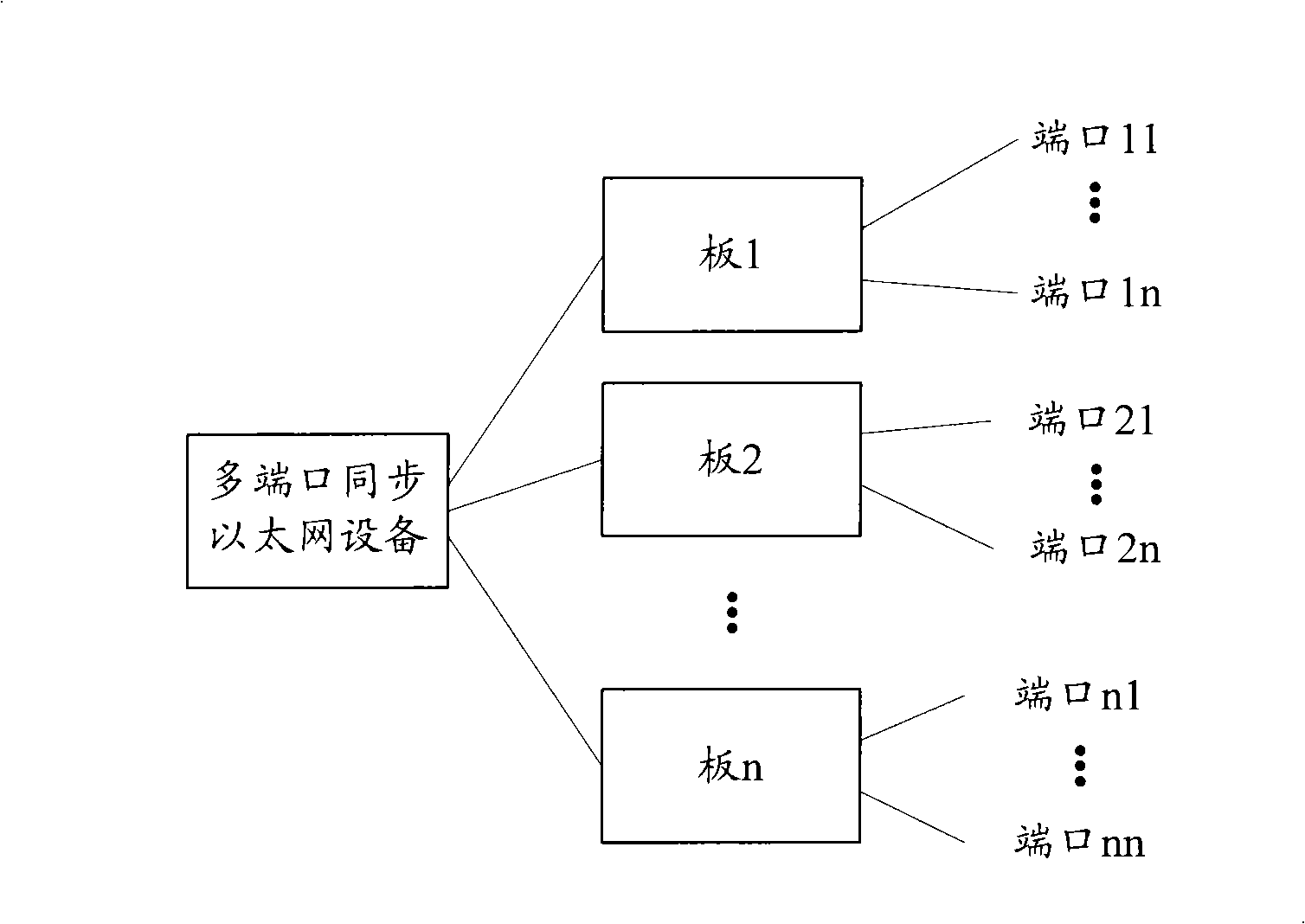

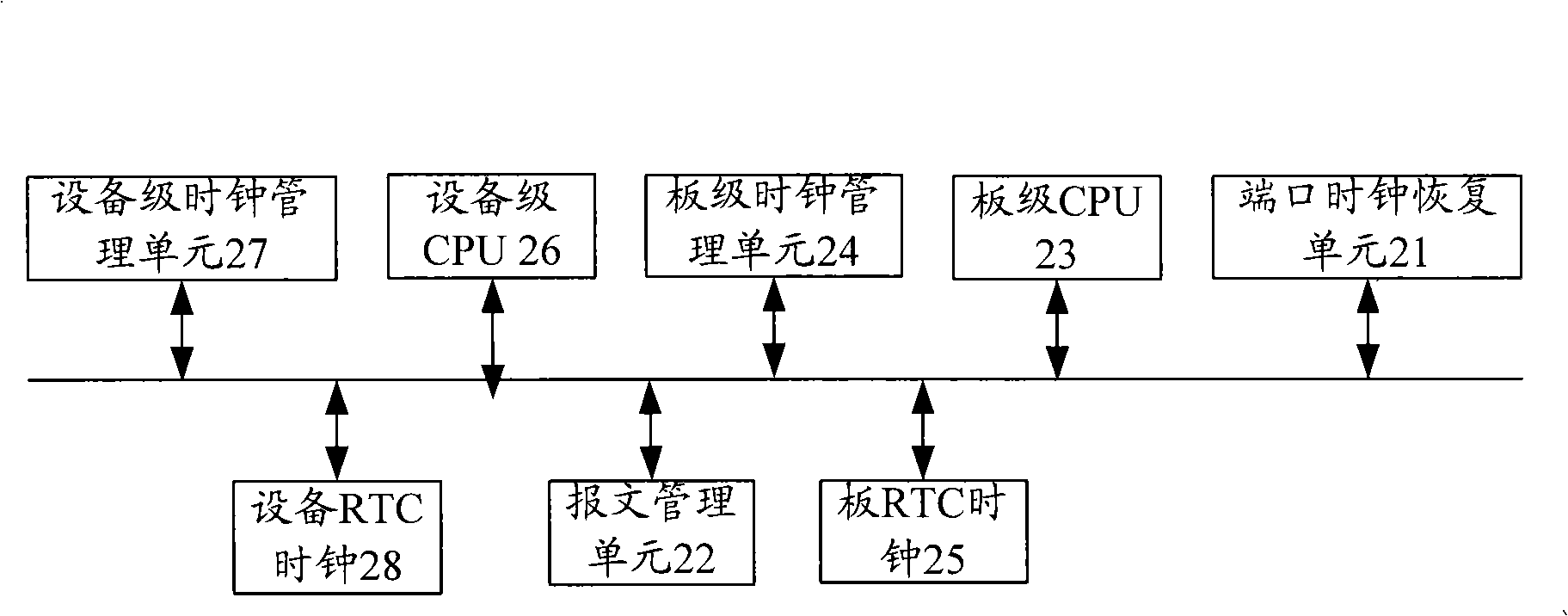

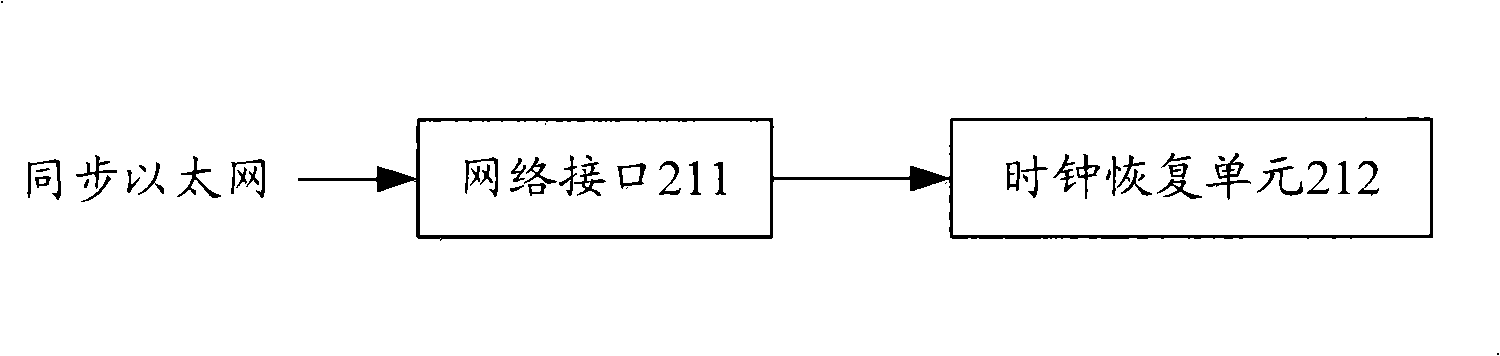

Clock synchronization method and system of multiport synchronization Ethernet equipment

ActiveCN101296070AHigh precisionThe precision level determines that the clock precision is highData switching by path configurationSynchronising arrangementReal-time clockEthernet

The invention discloses a clock synchronization method for a multiport synchronization Ethernet device, which comprises the following steps: slave ports and master ports are determined according to the clock resumed from each port and real time clock (RTC) of boards is used for synchronizing the RTC of each master port on the boards after using the clock of the slave ports to synchronize the clock of the boards; slave boards and master boards are determined according to the RTC of each board and the clock of the slave boards is used for synchronizing the RTC of the device and the RTC of the device is transmitted to the boards; the boards synchronize the RTC of the boards according to the RTC of the device and the RTC of the boards after the synchronization is used for synchronizing the clock of each port on the boards. Meanwhile, the invention discloses a clock synchronization system of the multiport synchronization Ethernet device, which comprises a port clock resuming unit, a board level CPU, a board level clock management unit, a device level CPU and a device level clock management unit. The utilization of the invention can realize the synchronization of all clocks of the multiport synchronization Ethernet device.

Owner:ZTE CORP

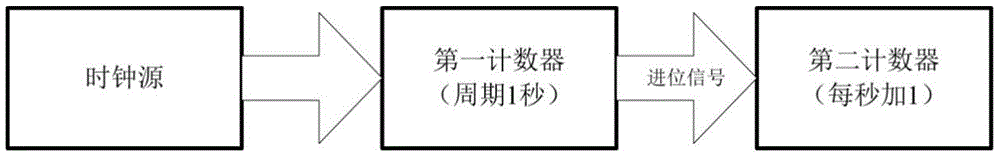

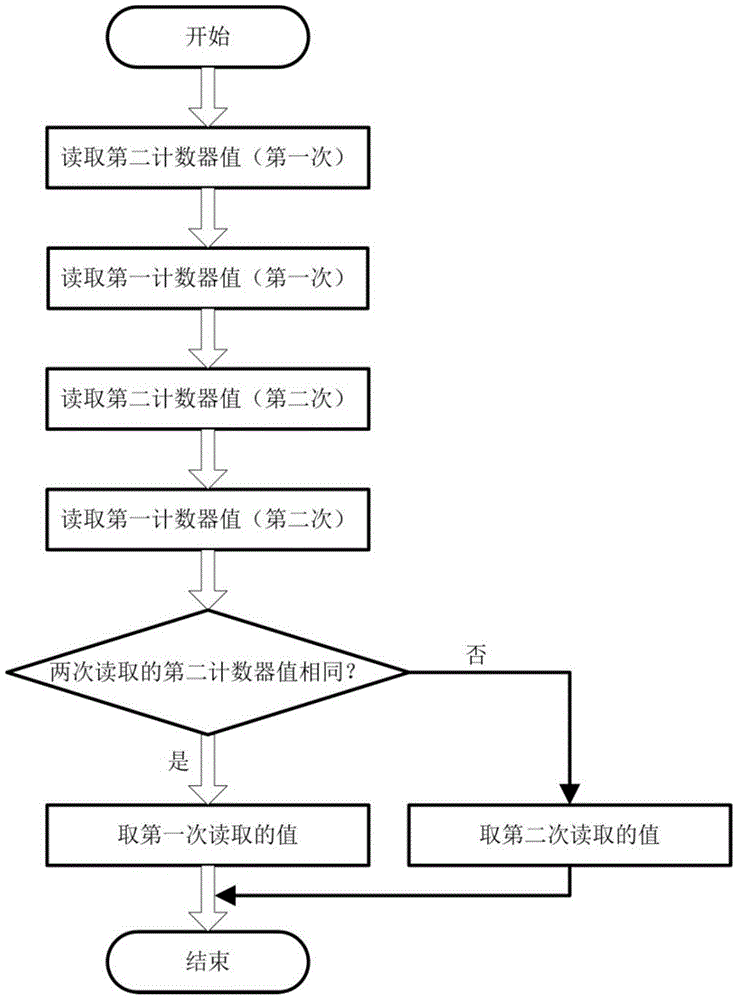

Clock device based on timestamp and counters and achieving method thereof

InactiveCN105717979AImprove real-time performanceAvoid Reading ErrorsGenerating/distributing signalsTimestampNanosecond

The invention discloses a clock device based on a timestamp and counters and an achieving method thereof.The clock device comprises the first counter and the second counter which are sequentially connected.The first counter serves as a prescaler of the second counter, and each counting period of the first counter can produce a carry signal for the second counter to drive the second counter to add one.After each counting period is finished, the first counter automatically reloads and begins the next counting period.The clock device has the advantages that the pure hardware clock can achieve very high clock precision (millisecond, microsecond and nanosecond), and the system time reading method can prevent reading errors caused by critical problems so that reading can be more reliable and high in timeliness; the timestamp is set to be in year 2,000, calculation can be simplified, and the time expression range can be enlarged; the RTC function can be achieved on a hardware platform without RTC.

Owner:STATE GRID INTELLIGENCE TECH CO LTD

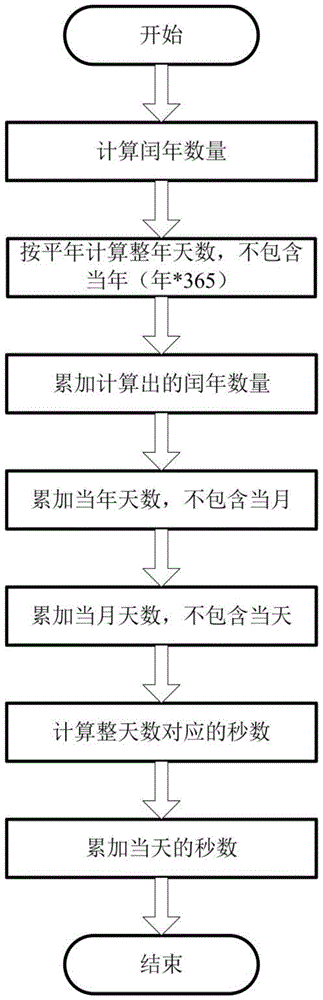

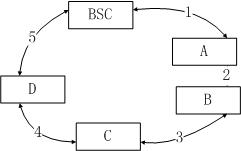

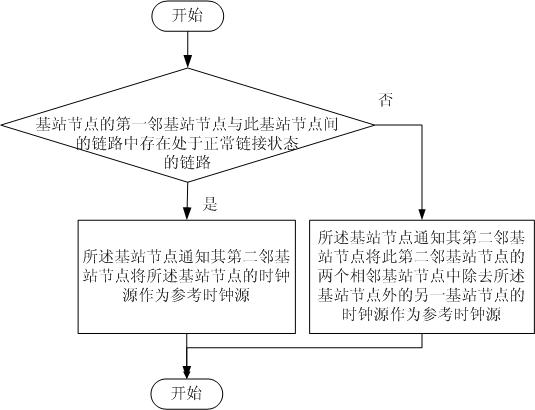

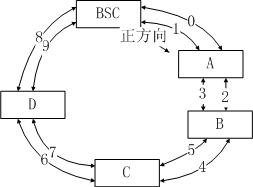

Method and system for maintaining network link clock

ActiveCN102014481AImprove clock accuracyImprove connectivitySynchronisation arrangementSelf-healingConnection type

The invention discloses a method and a system for maintaining a network link clock. The method comprises the following steps that: when a link in a normal link state exists in a link between a first neighboring base station node of a base station node and the base station node, the base station node informs a second neighboring base station node of taking a clock source of the base station node as a reference clock source; and when a link in a normal link state does not exist in the link between the first neighboring base station node of the base station node and the base station node, the base station node informs the second neighboring base station node of taking a clock source of the other base station node except the base station node in two neighboring base station nodes of the second neighboring base station node as the reference clock source. When a link network is switched among a ring link network, a cascade link network and a point-to-point link network according to the on-off connection type of the link, the clock accuracy of each base station node is still maintained and the self-healing protective capability of the link network is enhanced.

Owner:ZTE CORP

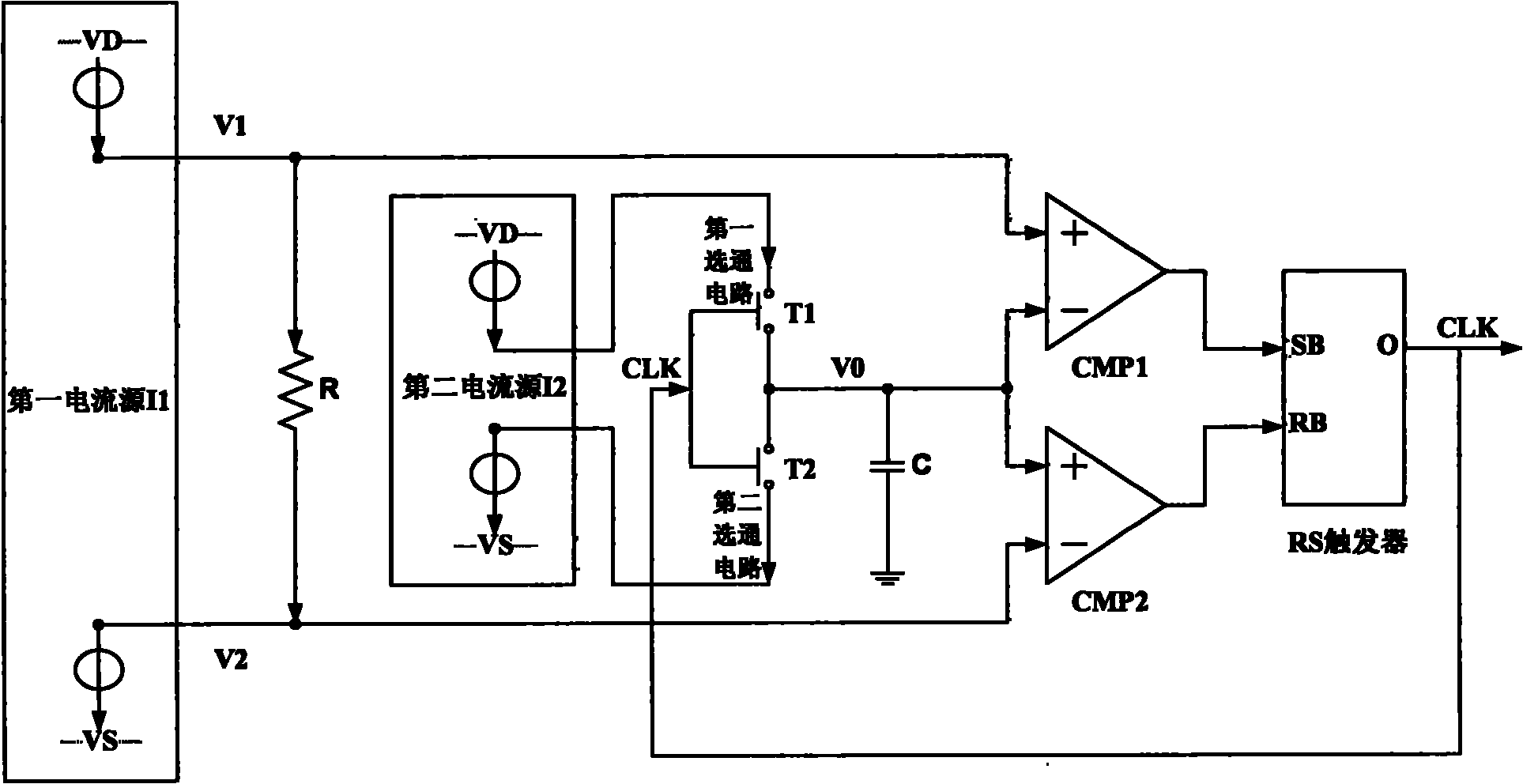

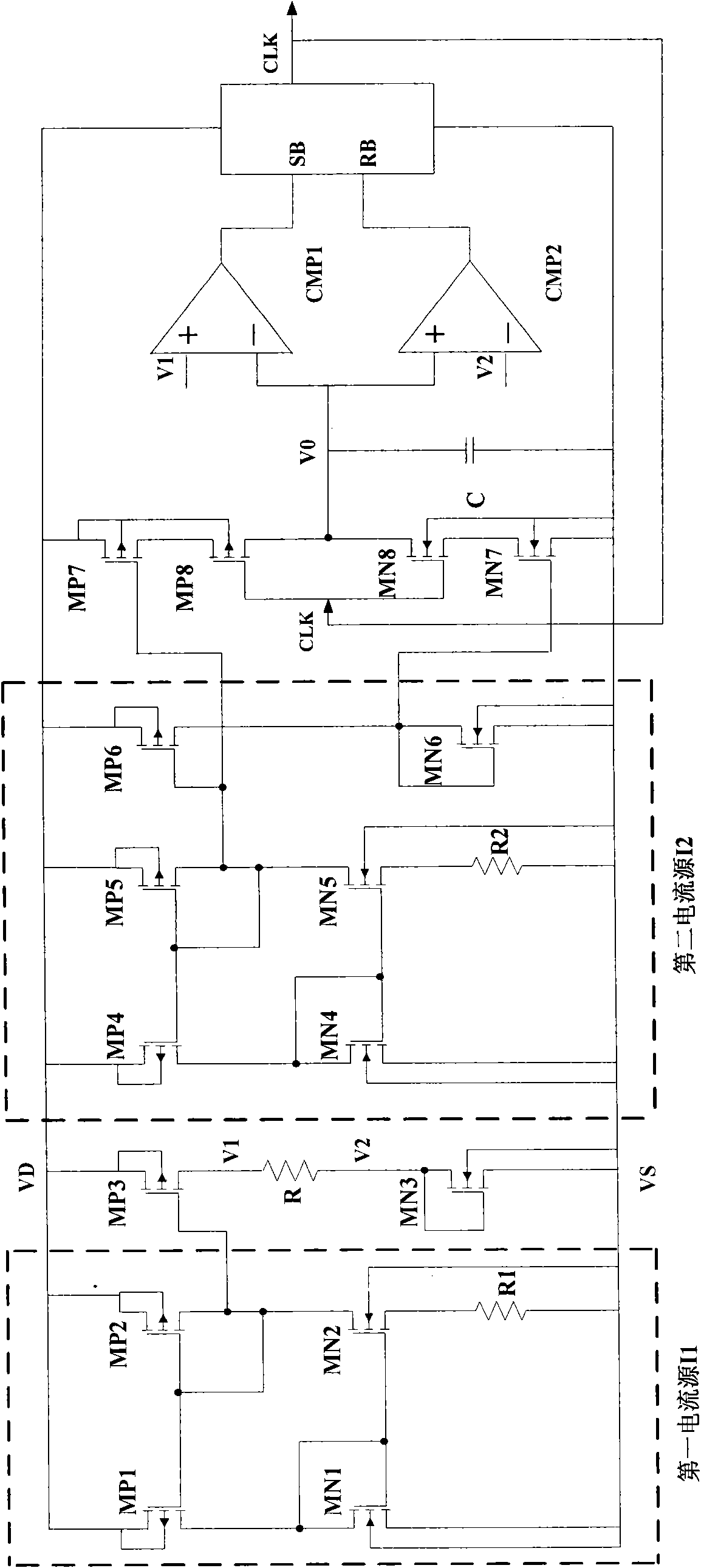

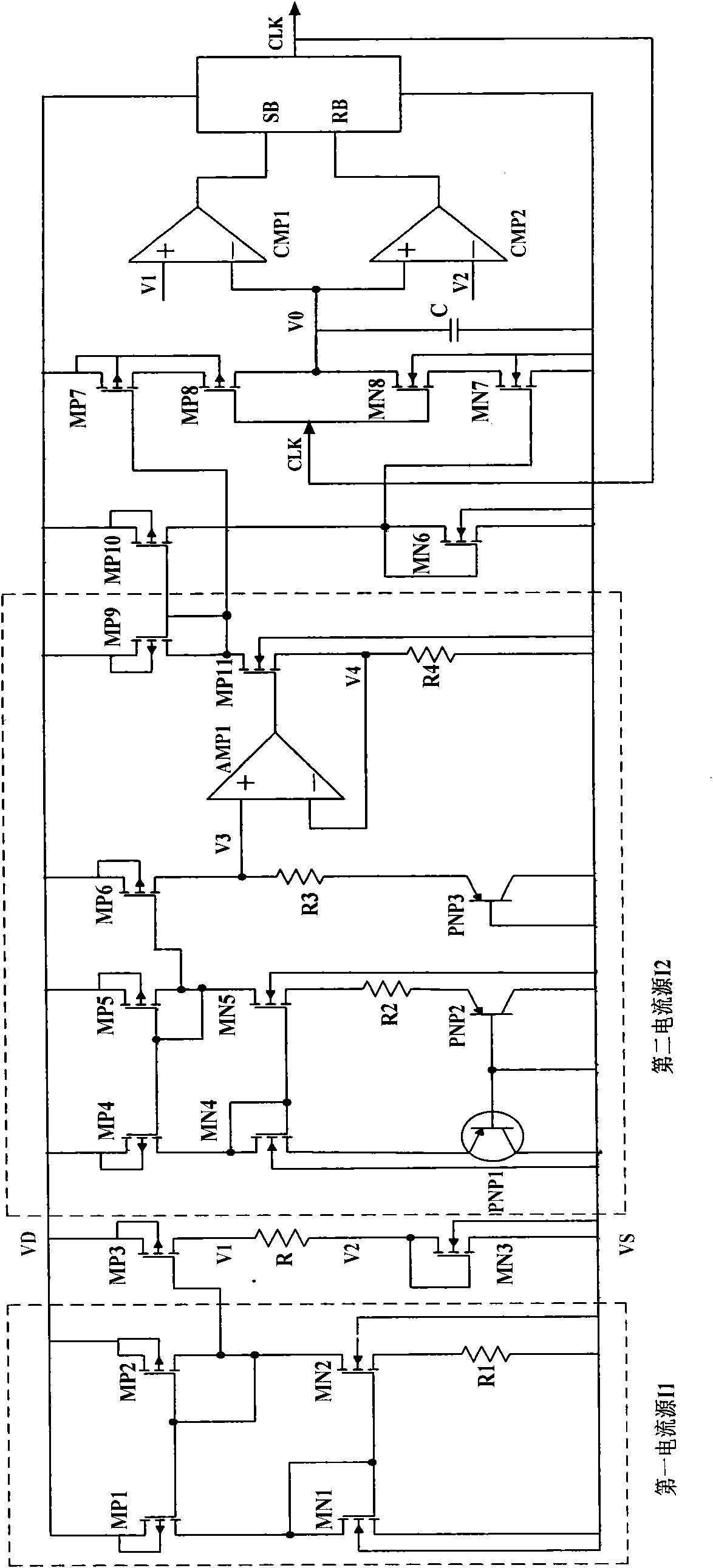

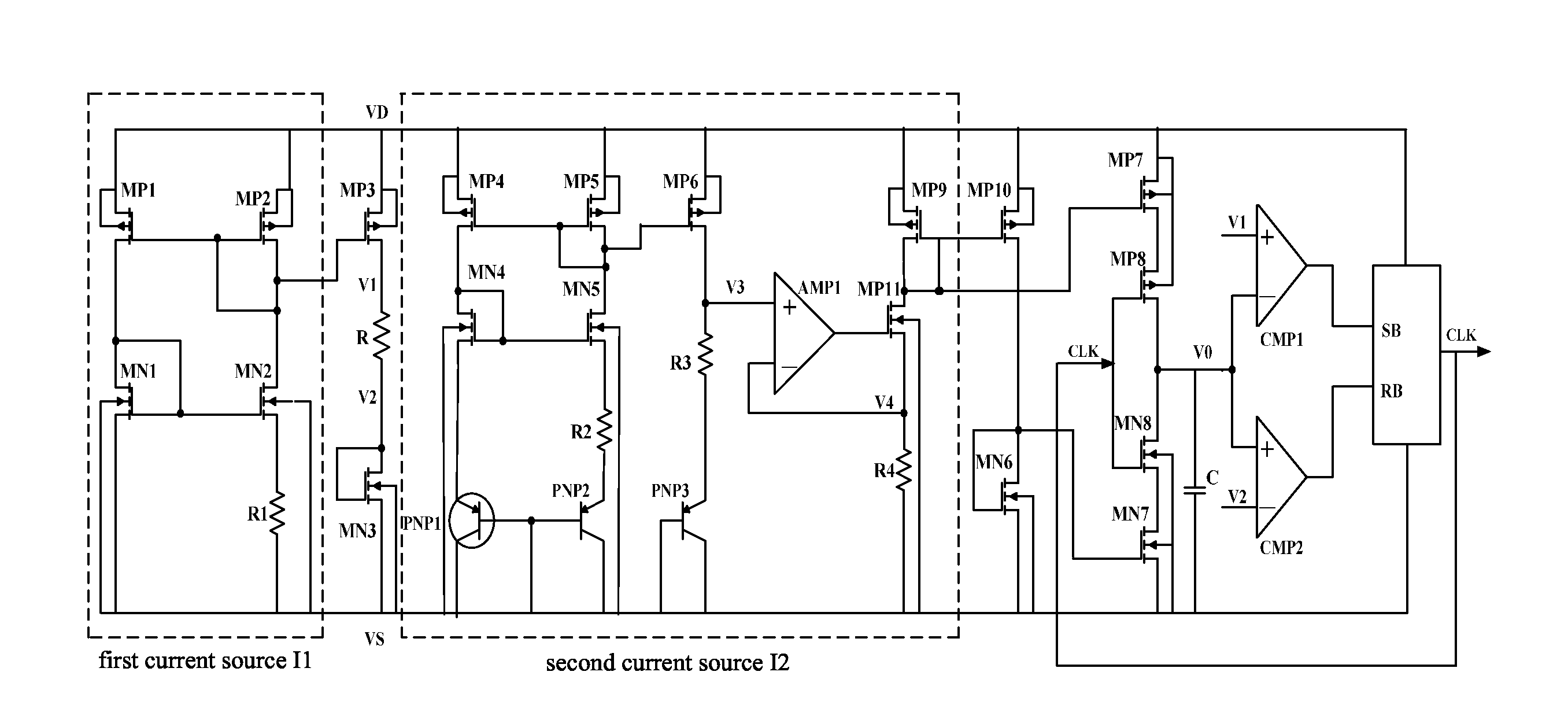

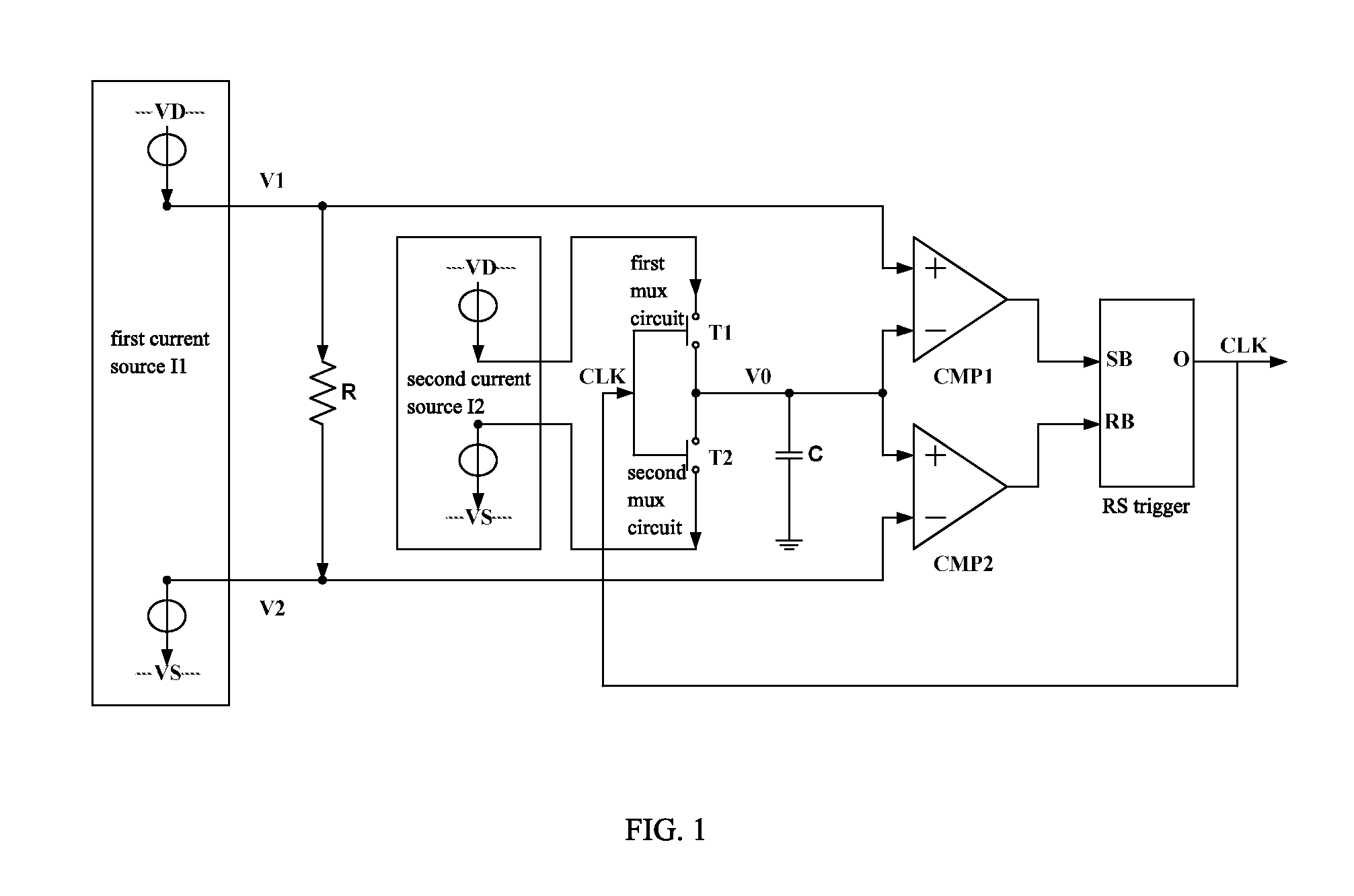

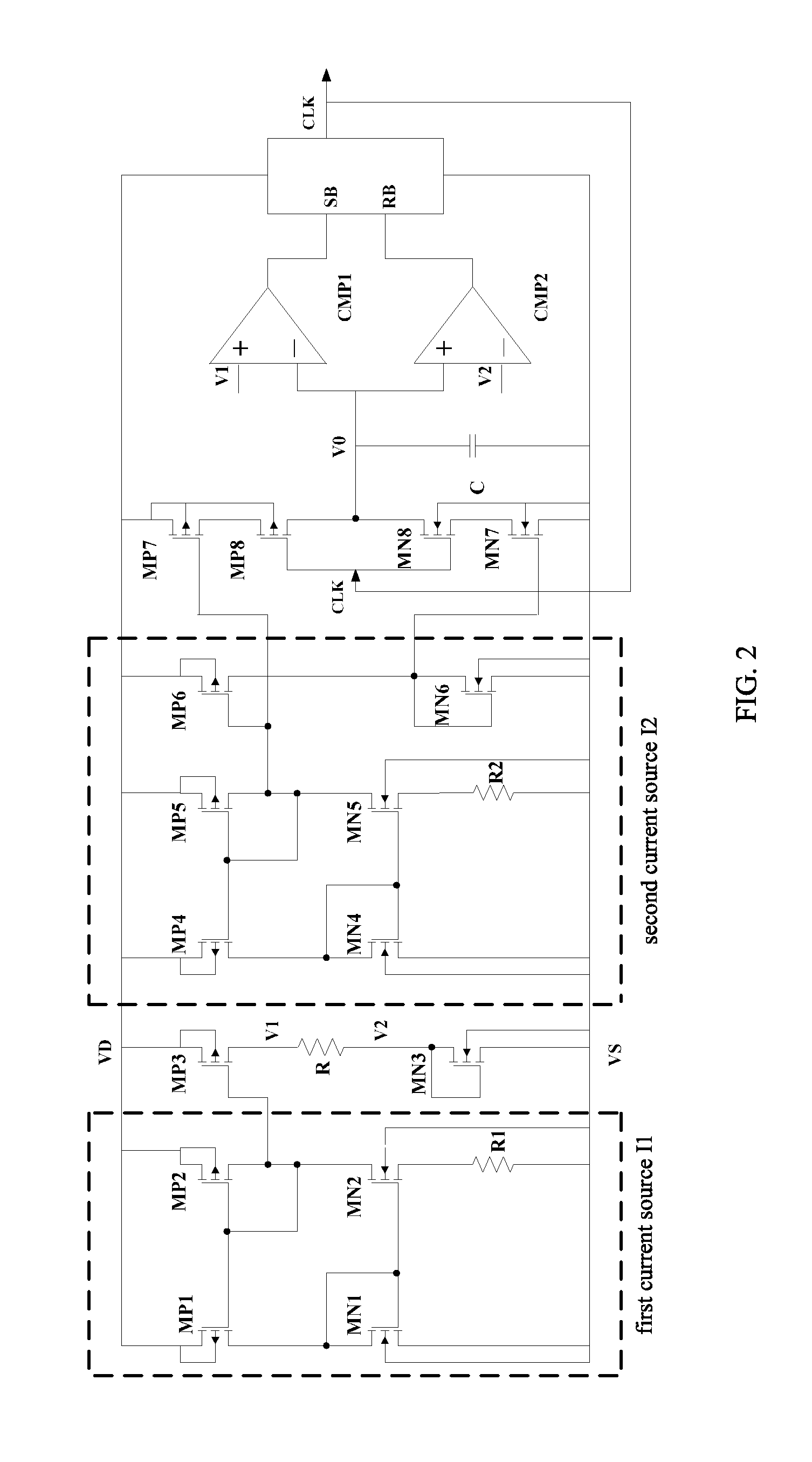

Clock generating circuit

InactiveCN101997521ASimple structureSmall process deviationElectric pulse generator circuitsCapacitancePower flow

The invention discloses a clock generating circuit. The clock generating circuit comprises a first current source, a resistor connected with the first current source, a second current source, a first gating circuit connected with the second current source, a second gating circuit connected with the second current source, a capacitor connected with the first gating circuit and the second gating circuit, a first comparator connected with the first current source and the capacitor, a second comparator connected with the first current source and the capacitor, and a remote sensing (RS) trigger connected with the first comparator and the second comparator, wherein the RS trigger outputs a clock signal to an input control terminal of the first gating circuit and an input control terminal of thesecond gating circuit; when the first gating circuit is gated, the second current source charges the capacitor; and when the second gating circuit is gated, the second current source discharges the capacitor. The clock generating circuit has a simple structure, low process variation and relatively low cost and improves the clock precision to the maximum degree.

Owner:CHENGDU MINGXINGXINGTONG TECH CO LTD

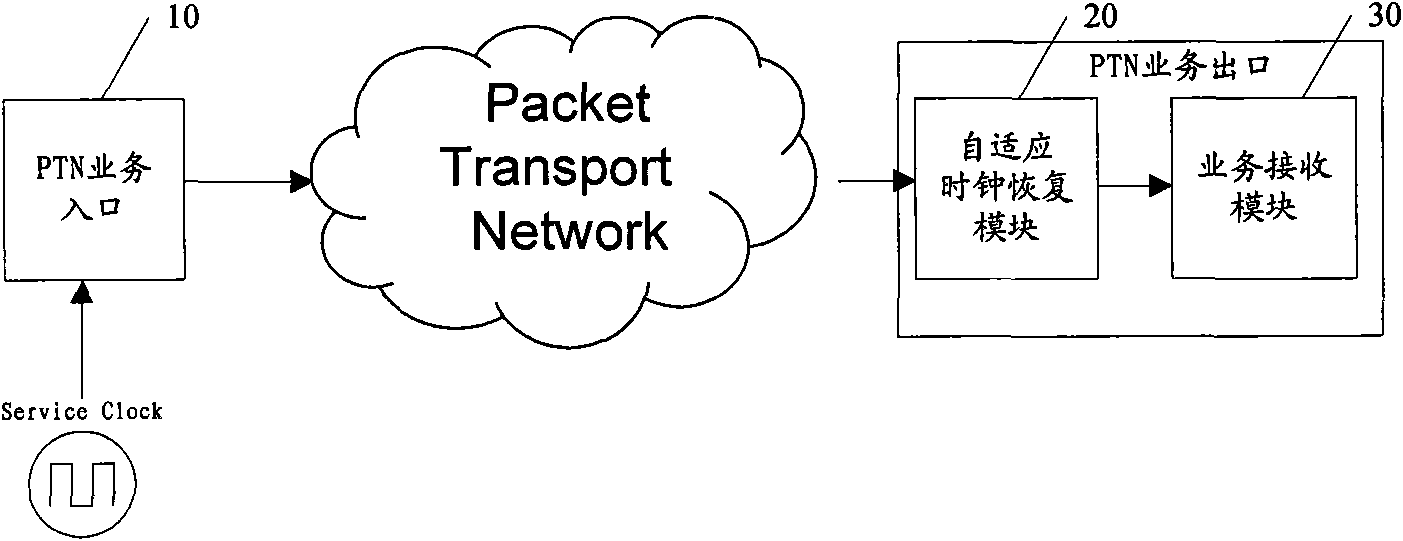

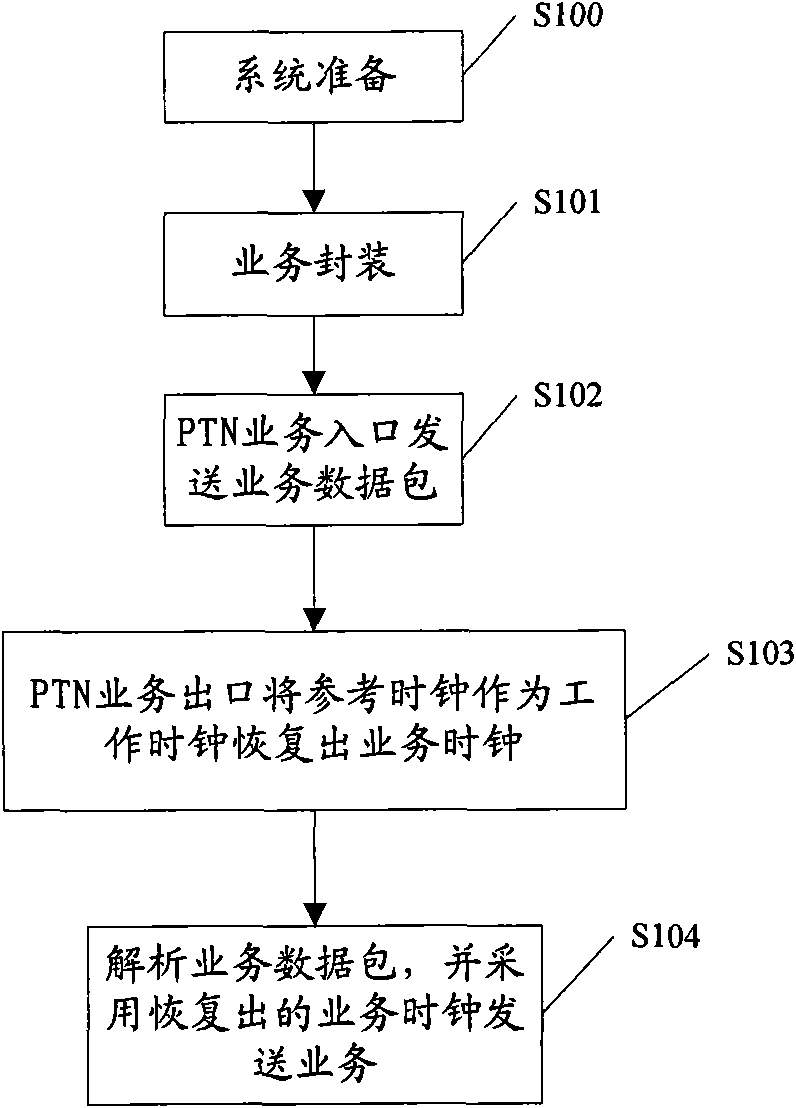

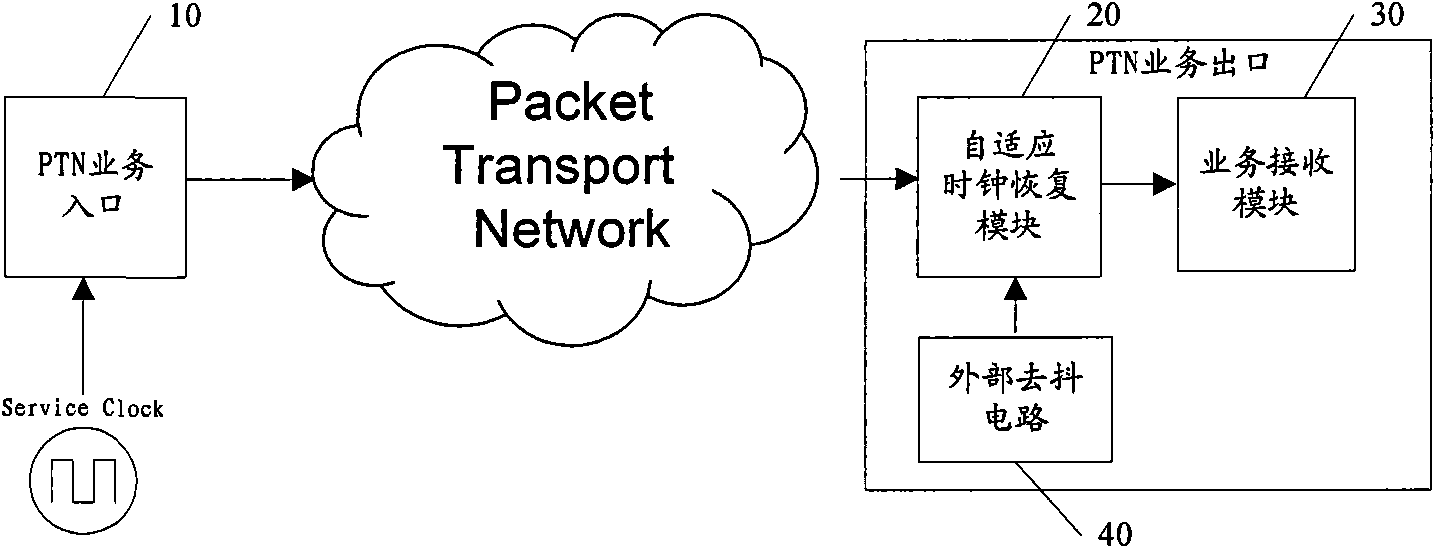

Method and system for recovering self-adapted service clock based on PTN

ActiveCN101651535AImprove network performanceReduce jitterData switching networksSynchronising arrangementClock recoverySelf adaptive

The invention discloses a method and a system for recovering a self-adapted service clock based on PTN. The method comprises the following steps: a PTN service inlet sends a service data packet by using a source clock so that the service data packet is transmitted to a PTN service outlet through a packet transport network; the PTN service outlet receives the service data packet; the PTN service outlet recovers the service clock from the service data packet by using a reference clock as a working clock; and the PTN service outlet analyzes the service data packet into corresponding service and transmits the corresponding service by using the service clock. The method and the system for recovering the self-adapted service clock based on the PTN effectively reduce the shake of the service clock and obviously enhance the network property of the PTN network.

Owner:ZTE CORP

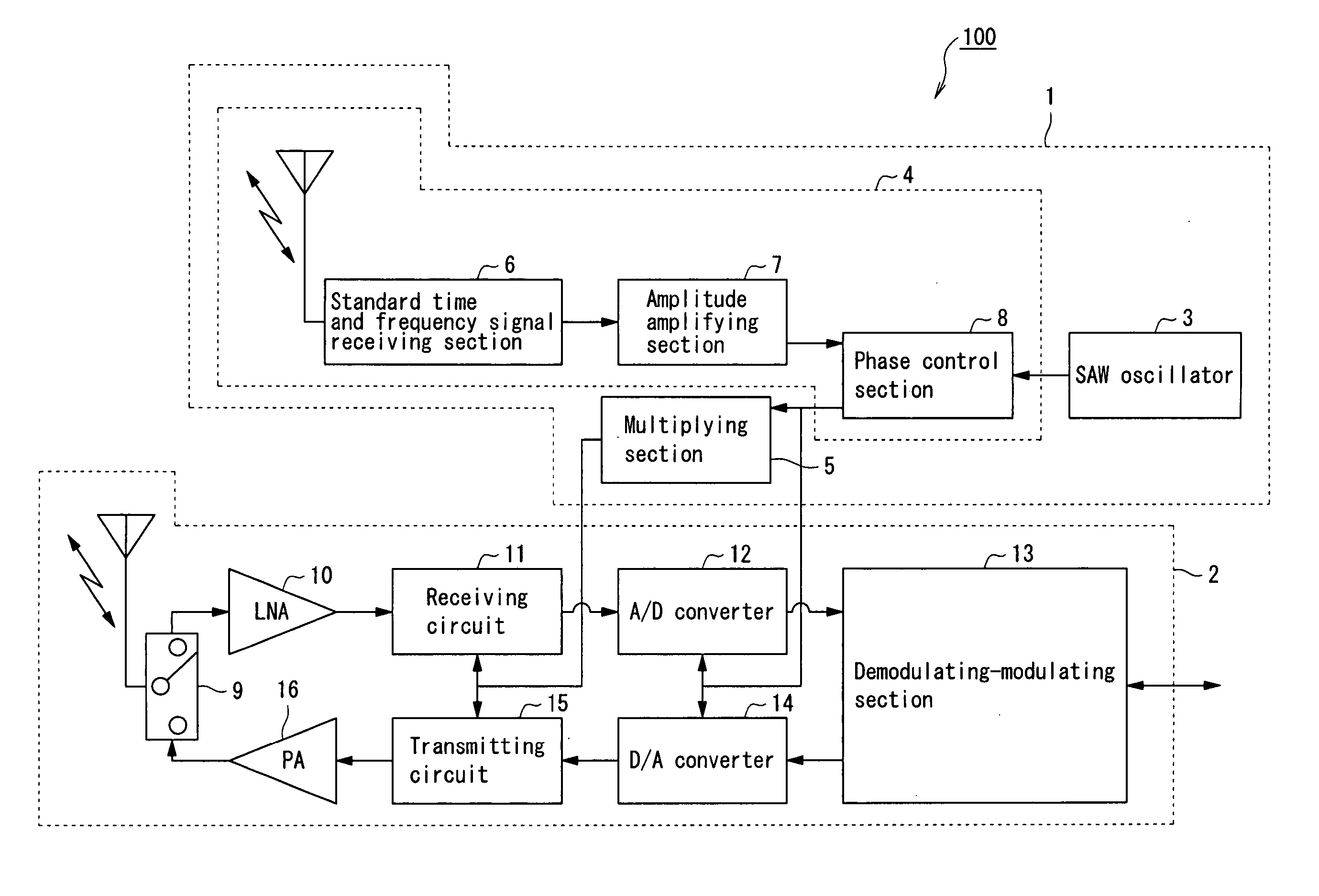

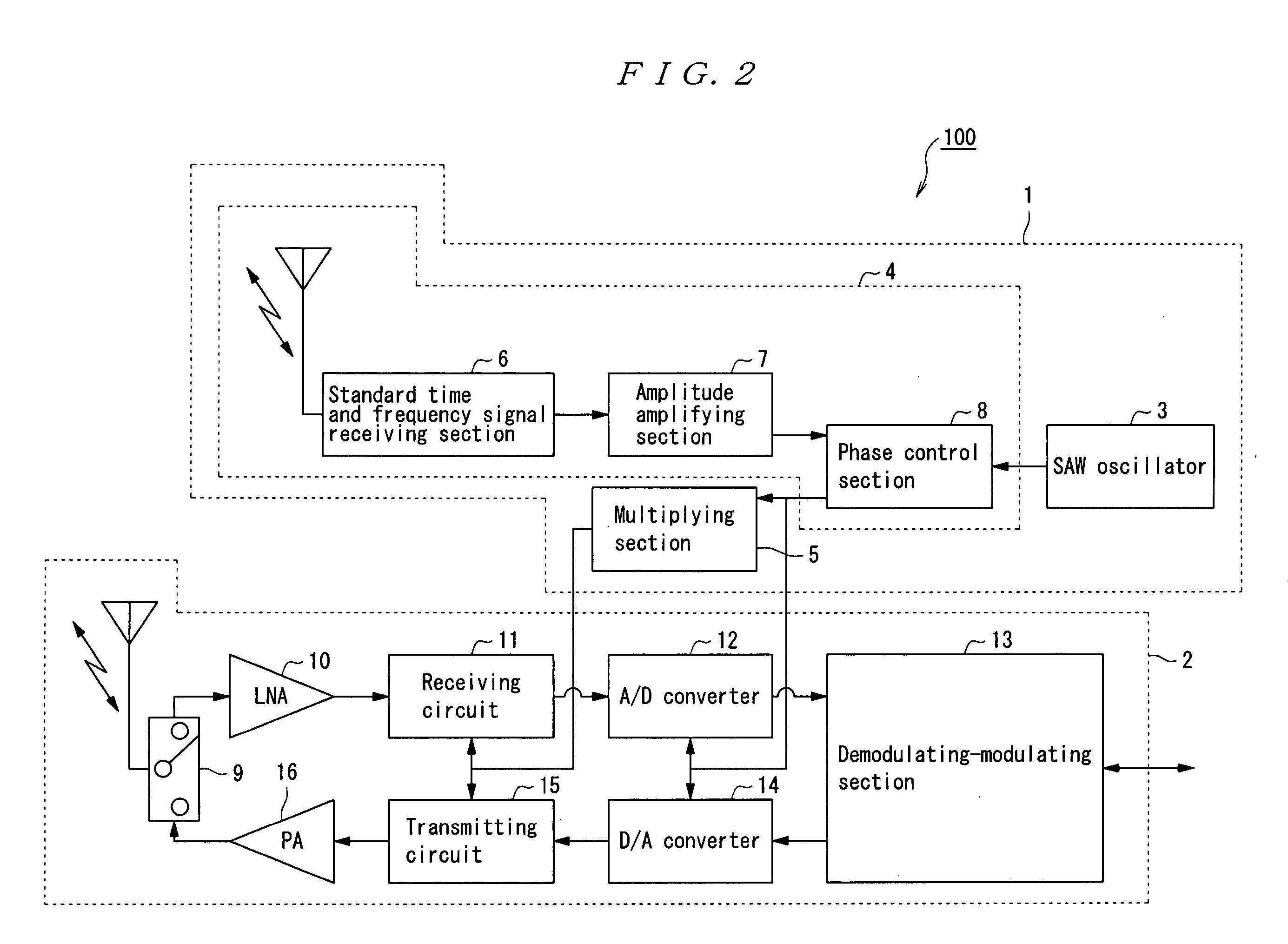

Clock signal correcting circuit and communicating apparatus

InactiveUS20050084047A1Improve clock accuracyAccurate synchronizationPulse automatic controlSetting time indicationCarrier signalPhase control

To improve the accuracy of a clock signal. The phase of a clock signal output from an SAW oscillator 3 is corrected by a phase control section 8 so that a signal synchronizing with the carrier wave of a standard time and frequency signal, that is, a carrier wave signal phase-synchronizes with a clock signal. Therefore, when a standard time and frequency signal can be received, it is possible to correct a clock signal in accordance with a carrier wave signal which can be generated from the standard time and frequency signal anytime. Therefore, even if operational environments (for example, temperatures) of the SAW oscillator 3 are changed and the phase of a clock signal output from the SAW oscillator 3 is fluctuated due to the change, it is possible to synchronize the fluctuated clock signal with a standard time and frequency signal, that is, the carrier wave of a radio wave for providing a very accurate frequency standard and time service signal and as a result, it is possible to improve the accuracy of the clock signal in accordance with the correction.

Owner:SEIKO EPSON CORP

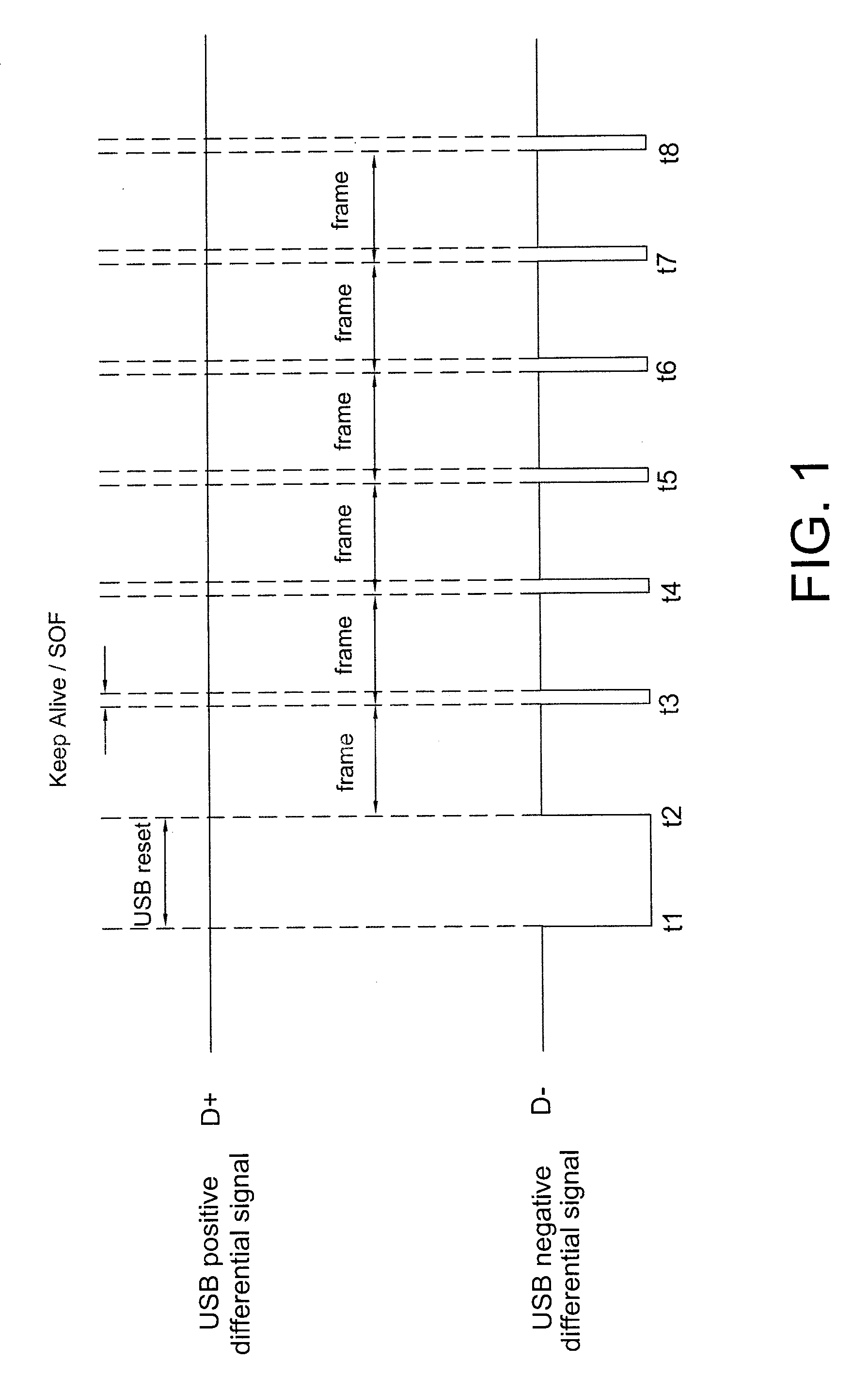

Method for automatically adjusting clock frequency and clock frequency adjusting circuit

InactiveUS20090284298A1Improve clock accuracySmall sizeElectric pulse generatorGenerating/distributing signalsClock rateFrame time

A method for automatically adjusting the clock frequency for a USB interface including the steps of: generating a clock signal with an adjustable frequency; receiving a USB differential signal; counting the clock signal based on each frame time of the USB differential signal and obtaining a count value; and adjusting the frequency of the clock signal when the count value exceeds a predetermined count range. The present invention further provides a clock frequency adjusting circuit.

Owner:PIXART IMAGING INC

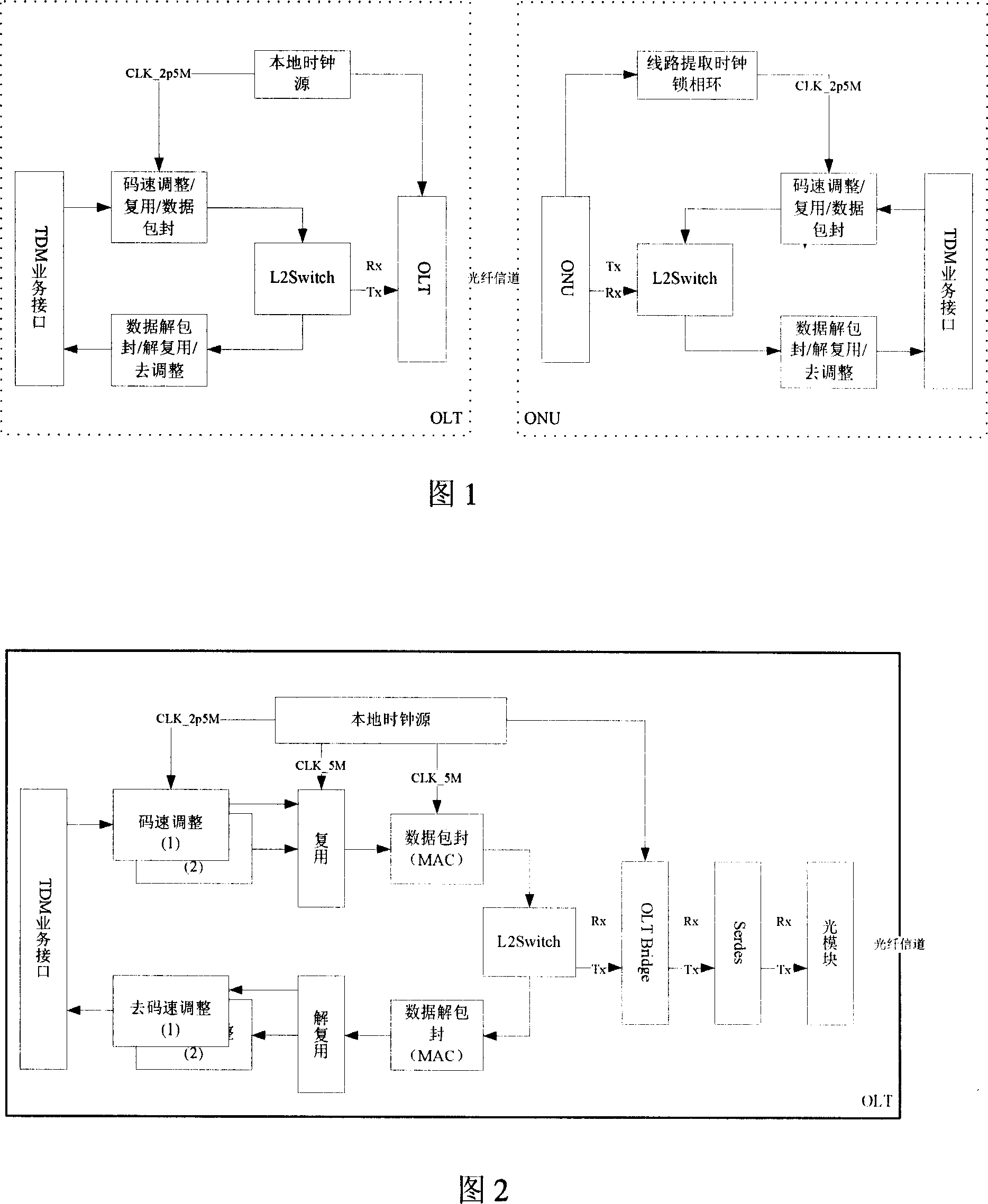

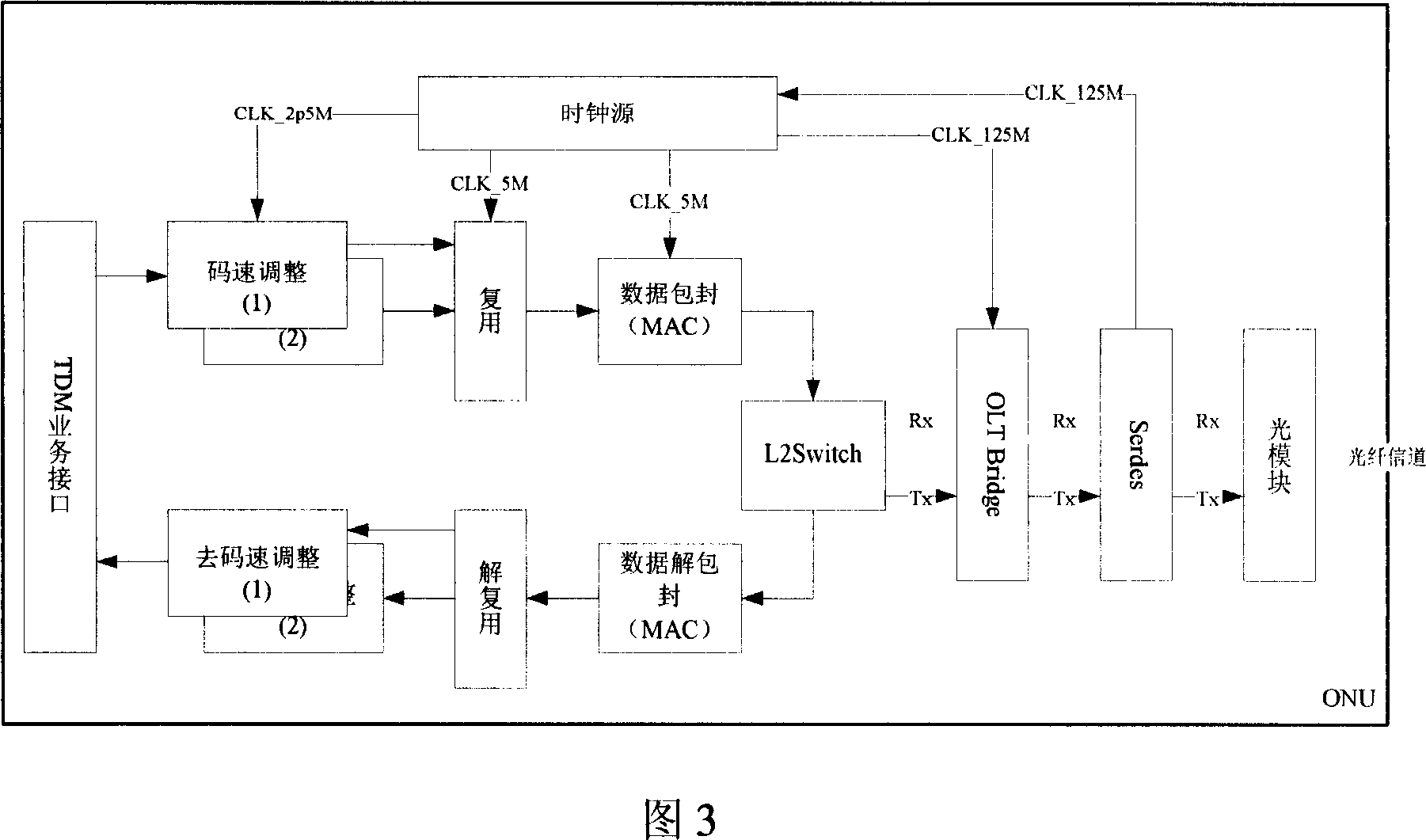

A passive optical network system for realization of TDM service based on Ethernet

ActiveCN1972160AReduce complexityImprove clock accuracyTime-division multiplexElectromagnetic transmissionBusiness dataReal-time computing

This invention provides one light network system without source based on Ethernet of TDM business, which comprises fiber branch connection light path terminal and light internet unit, wherein, the terminal and unit are set with TDM business adapter; the said terminal TDM business adapter adopts light network send clock to seal the TDM business data or analysis; the said light network unit TDM business adapter by use of light network receive clock for analysis or sealing.

Owner:广州市高科通信技术股份有限公司

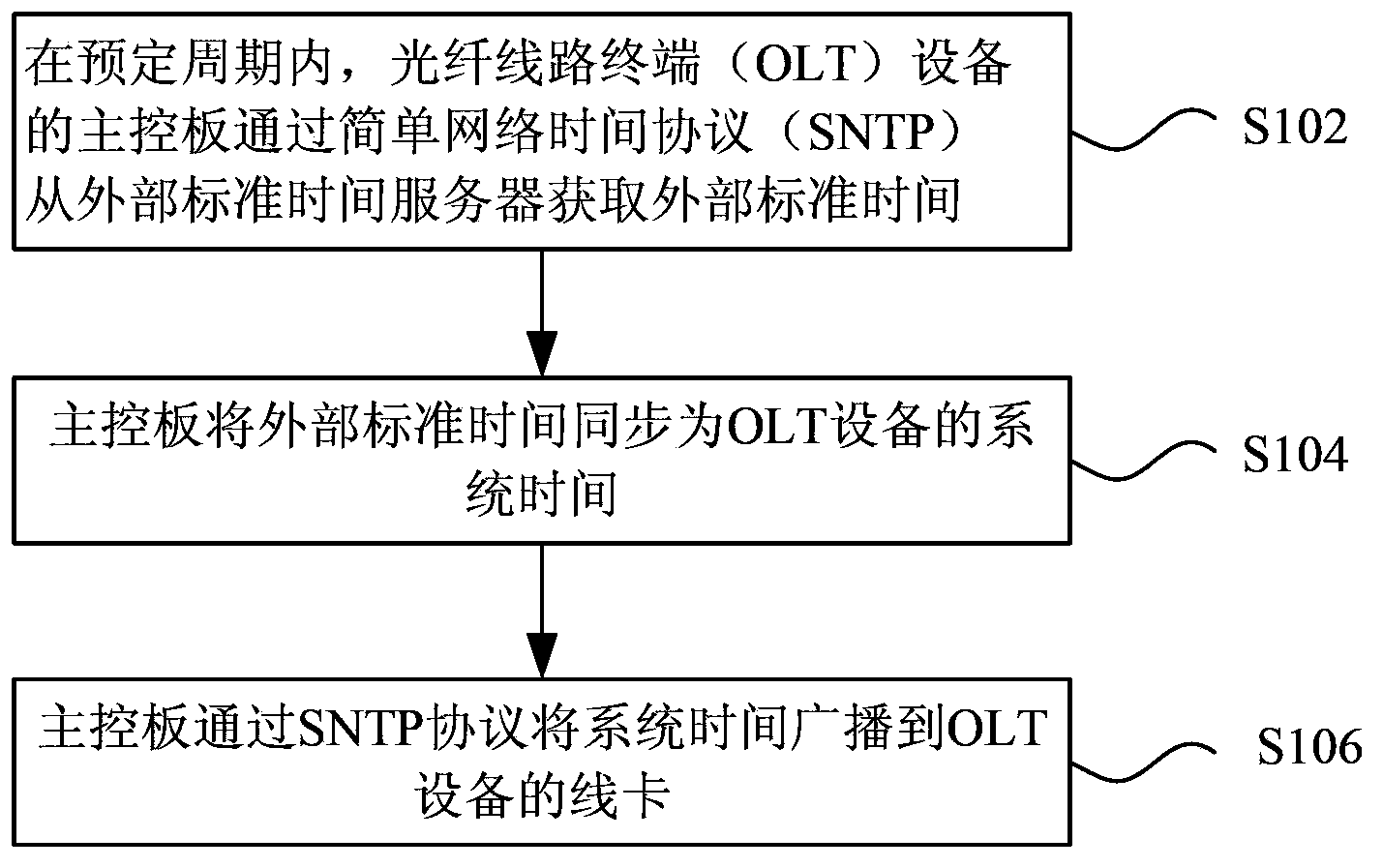

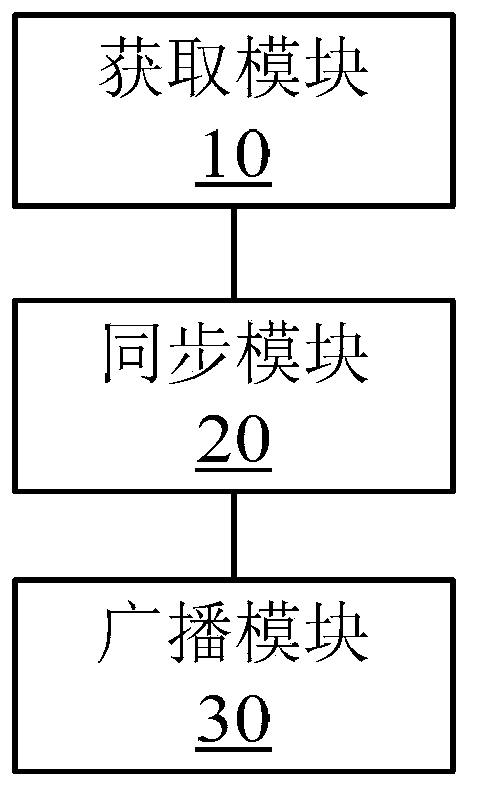

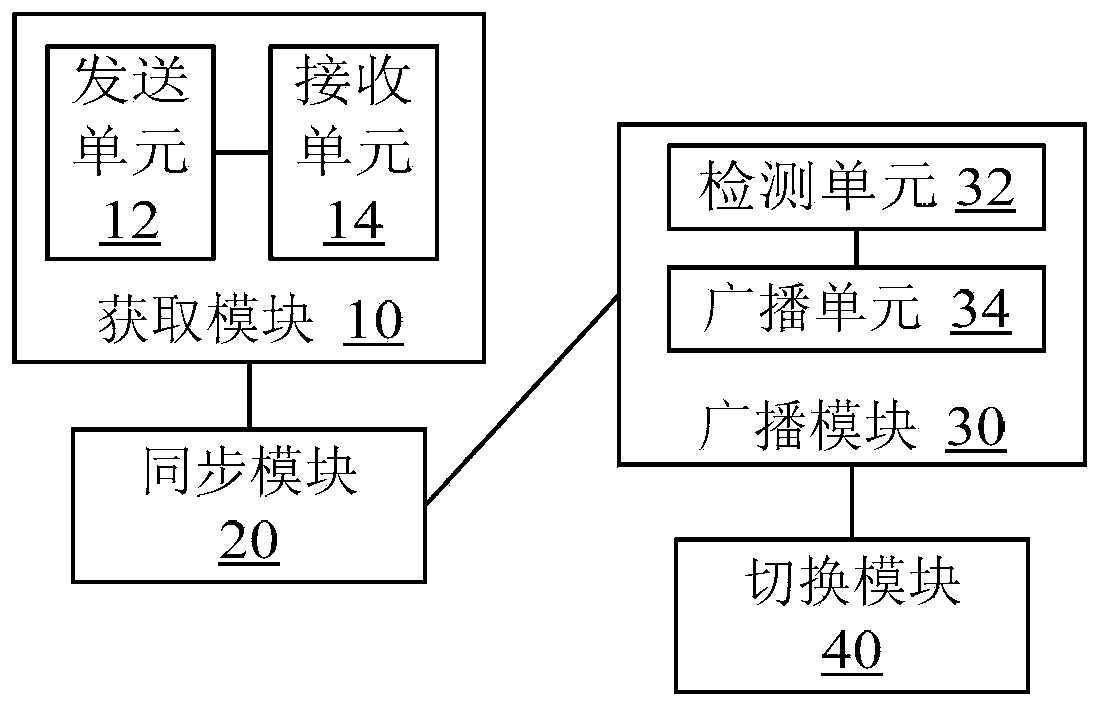

Time synchronization method, device and system for optical fiber line termination equipment

InactiveCN104219037ASolve the problem of poor precision and inflexibilityGuaranteed reliabilitySynchronising arrangementLine cardOptical line termination

The present invention discloses time synchronization method, device and system for optical fiber line termination equipment, wherein the method comprises: in a predetermined period, a main control panel of optical fiber line termination (OLT) equipment acquires an external standard time from an external standard time server via a simple network time protocol (SNTP); the main control panel synchronizes the external standard time into a system time of the OLT equipment; and the main control panel broadcasts the system time to a line card of the OLT equipment via the SNTP protocol. The present invention achieves the effects for improving clock accuracy and ensuring reliability of services having higher requirements to time accuracy.

Owner:TOPVISION TECH CO LTD

Signal regeneration device, optical receiver, and signal processing method

InactiveUS7853152B2Improve clock accuracyImprove receiver sensitivityEqualisersPhase-modulated carrier systemsDifferential phaseSignal regeneration

A signal regeneration device which makes an extracted clock signal highly accurate while maintaining superior receiving sensitivity. To this end, a device of the present invention is configured to have a branch section for branching an input electrical signal which has been demodulated from a differential phase-shift modulated state; a first filter for equalizing a waveform of one of the demodulated electrical signals branched by the branch section; a clock recovery section for recovering a clock signal from the demodulated electrical signal whose waveform has been equalized by the first filter; and a data regeneration section for regenerating a data signal from a remaining one of the demodulated electrical signals branched by the branch section and from a clock signal recovered by the clock recovery section.

Owner:FUJITSU LTD

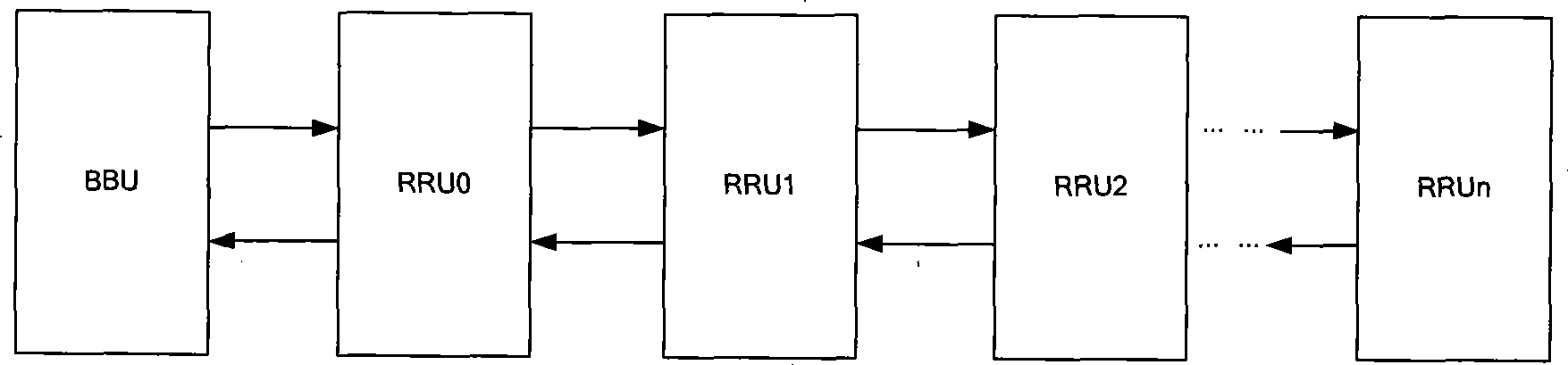

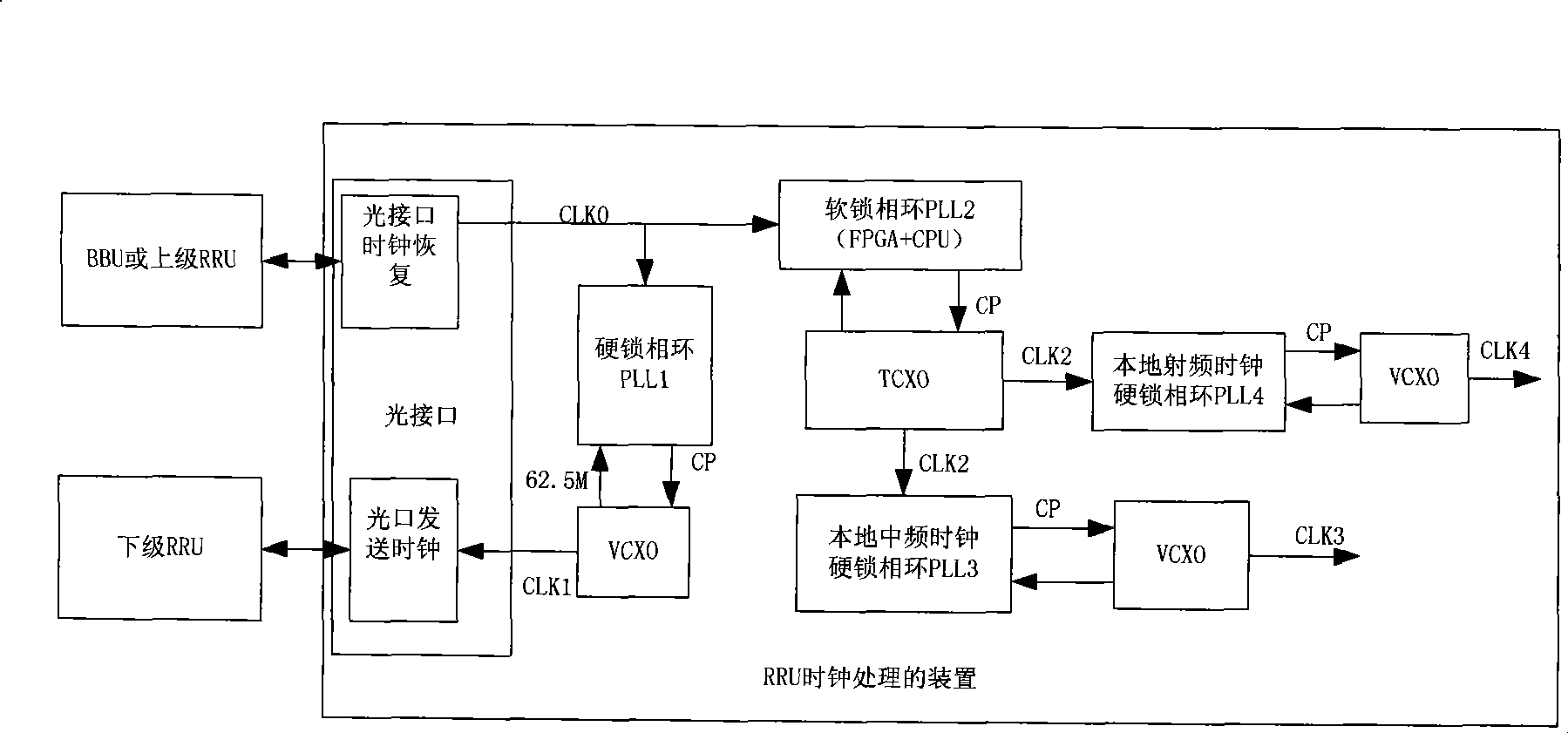

Method and apparatus for processing clock suitable for multilevel cascade of radio frequency zooming module

InactiveCN101437320AReduce the degree of deteriorationImprove clock accuracyNetwork planningPhase noiseClock recovery

The invention discloses a clock processing method suitable for multistage cascaded radio remote unit, which comprises: (a) an optical interface clock recovers a clock signal CLK0 acquired in data received from a baseband module or an upper-stage radio remote unit according to the radio remote unit; and (b) a hard phase-locked loop PLL1 takes the acquired clock signal CLK0 as a reference clock and outputs a clock signal CLK1 as a clock signal of an optical interface transmission clock of the radio remote unit, and the optical interface transmission clock transmits the received clock signal to the next radio remote unit; and a soft phase-locked loop PLL2 inputs the acquired clock signal CLK0 as a reference clock and outputs a clock signal CLK2 as a local reference clock according to a soft phase-locked algorithm. The method and the device can acquire optimization of indexes of clock accuracy and phase noise.

Owner:ZTE CORP

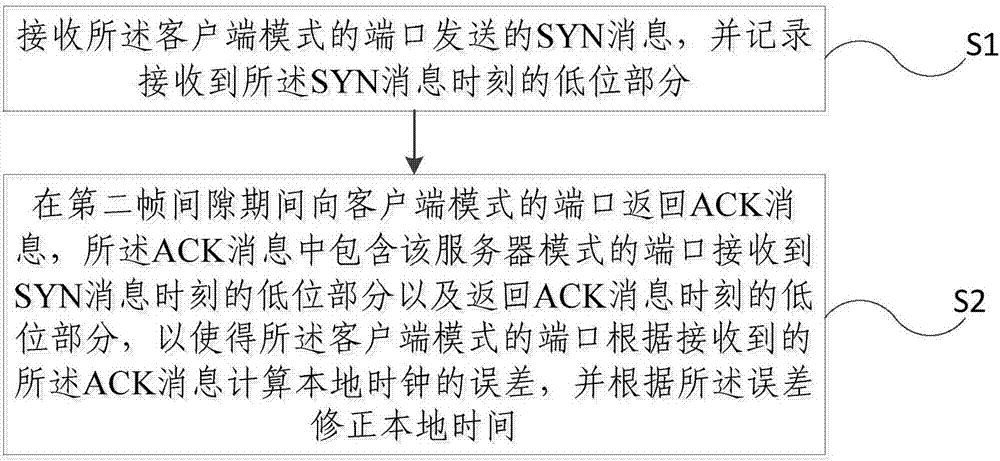

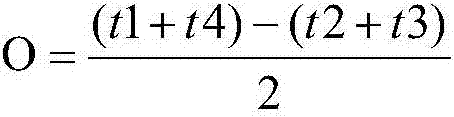

Time synchronization method

ActiveCN107888315AShort cycleBandwidth impactError prevention/detection by using return channelSynchronisation error correctionCrystal oscillatorMicrosecond

The invention provides a time synchronization method. The method includes the following steps: sending an SYN message to a server mode port during a first frame gap and recording a lower part of a sending moment to ensure that the server mode port records the lower part of the moment at which the SYN message is received, and returning an ACK message during a second frame gap, wherein the ACK message includes the lower part of the moment at which the SYN message is received and the lower part of the moment at which the ACK message is returned; receiving the ACK message returned by the server mode port, acquiring the lower part of the moment at which the server mode port receives the SYN message and the lower part of the moment at which the server mode port returns the ACK message accordingto the ACK message, and recording the lower part of the moment at which the ACK message is received; and calculating the error of a local clock and correcting the time of the local clock according tothe lower parts of all moments. According to the time synchronization method provided by the invention, the frame gaps are used as transmission carriers of time synchronization information, and thus the equipment can still achieve the microsecond-level time synchronization accuracy in the case of using only standard clock crystal oscillators.

Owner:TSINGHUA UNIV

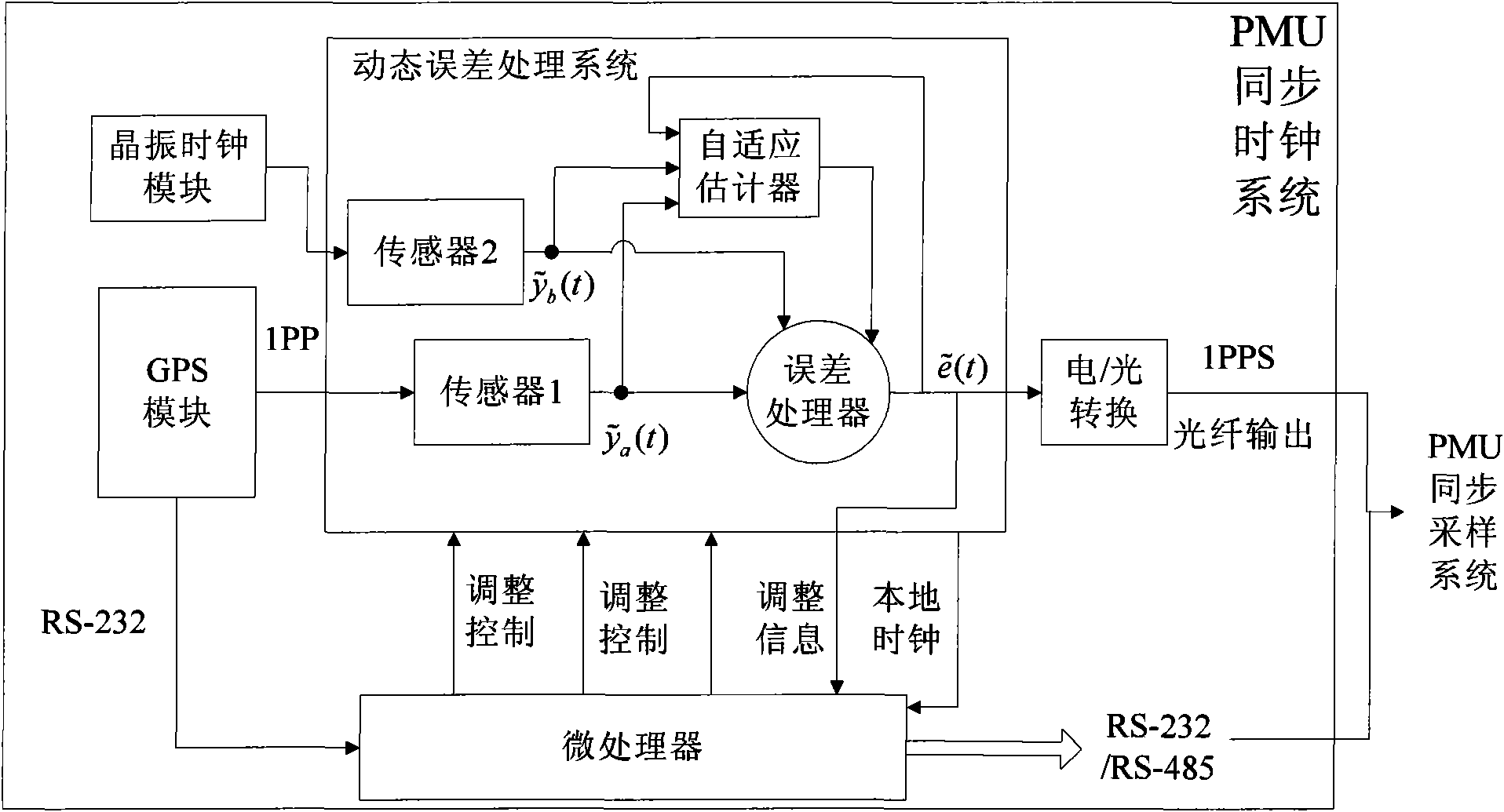

PMU synchronized clock system added by dynamic compensation

InactiveCN101551640AImprove clock accuracyGuaranteed reliabilitySynchronous motors for clocksVoltage-current phase angleSatellitePhase angle

The invention relates to a PMU synchronized clock system added by dynamic compensation belonging to the electric power system monitoring and controlling technology field, which comprises a GPS module, a crystal oscillator clock module, a microprocessor and a dynamic error processing system. Wherein, the GPS module sends the outputted data frame to the microprocessor, and sends second pulse signal to the dynamic error processing system; the crystal oscillator clock module sends the outputted second pulse signal to the dynamic error processing system; the dynamic error processing system performs judging and error processing to the second pulse signals; the microprocessor receives the RS-232 data frame from the GPS module, processes the serial outputted time message in real time and sends it to the PMU sampling system, receives the signal from the dynamic error processing system at the same time, and adjusting the signal correspondingly. The invention improves the clock precision, and can work normally and guarantee the phase angle measuring measurement error in the predetermined range even under the satellite losing lock or satellite experiment jumping condition, thereby, guarantees the system reliability.

Owner:SHANGHAI JIAO TONG UNIV

Clock Generation Circuit

InactiveUS20120133410A1Simple structureHigh-precision clock frequencyElectric pulse generator detailsGenerating/distributing signalsElectricityComparator

A clock generation circuit, includes a first current source, a resistor connected to the first current source, a second current source, a first demux circuit connected to the second current source, a second demux circuit connected to the second current source, a capacitor connected to the first demux circuit and the second demux circuit, a first comparator connected to the first current source and the capacitor, a second comparator connected to the first current source and the capacitor, and a RS trigger connected both to the first comparator and the second comparator. The present invention has simple structure, small process variation, and lower cost, and is able to improve the accuracy of the clock with maximum possibility.

Owner:IPGOAL MICROELECTRONICS (SICHUAN) CO LTD

A method to improve the precision of built-in real-time clock of energy meter mcu

ActiveCN103499803BCompensation value is accurateImprove clock accuracyElectrical measurementsReal-time clockCurve fitting

The invention discloses a method for improving the precision of a built-in real-time clock of an electric energy meter MCU. Based on the practical crystal oscillator frequency, fine compensation can be achieved. An electric energy meter comprises the MCU, a crystal oscillator and a power management unit. The method for improving the precision of the built-in real-time clock of the electric energy meter MCU includes the following steps of compensation amount calculation and clock calibration. Compensation amount calculation is performed according to the following processes that firstly, frequency deviations of the practical crystal oscillator under different temperatures are measured; secondly, a temperature-frequency deviation curve sketch is drawn, and the turn temperature T0 is found out; thirdly, the measured frequency deviations of the two sides of T0 undergo curve fitting, and a corresponding buckling constant is obtained; fourthly, a temperature-frequency deviation function table is formed according to a function of the third process, the frequency deviation value of the current temperature can be obtained through the temperature-frequency deviation function table according to the practical environmental temperature, and the frequency deviation value serves as the compensation amount for calibrating the clock under the practical environmental temperature. According to the method for improving the precision of the built-in real-time clock of the electric energy meter MCU, an accurate compensation value can be obtained according to errors of the practical crystal oscillator, and therefore the precision of the clock is improved.

Owner:YANGZHOU WANTAI ELECTRIC TECH CO LTD

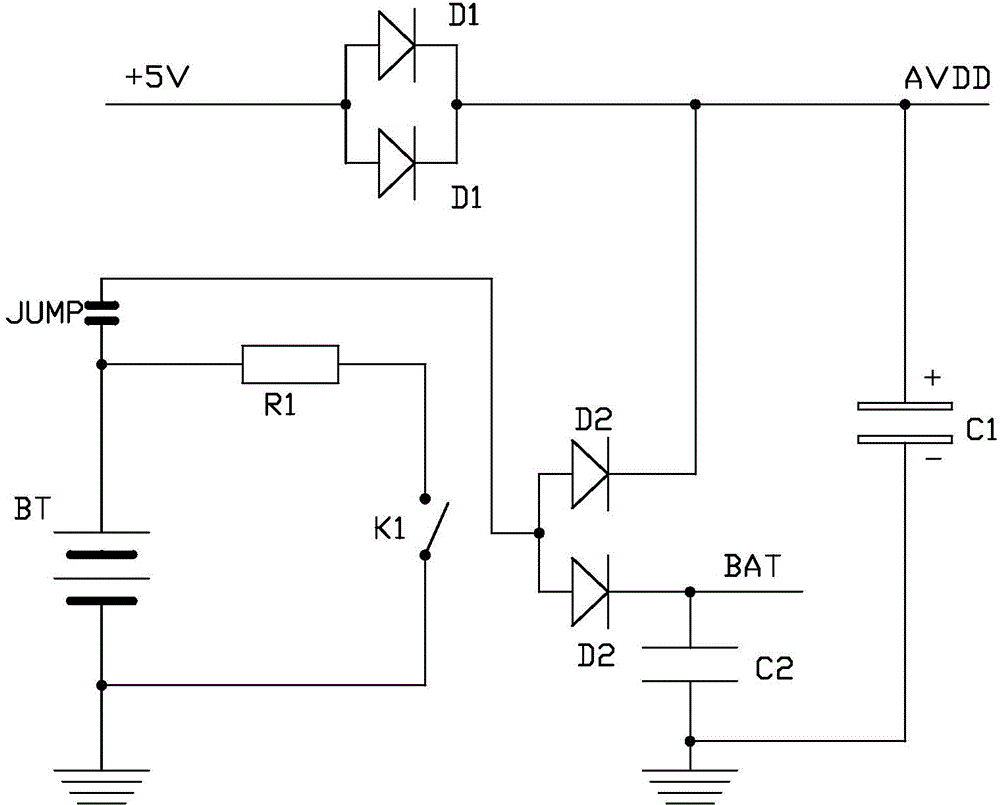

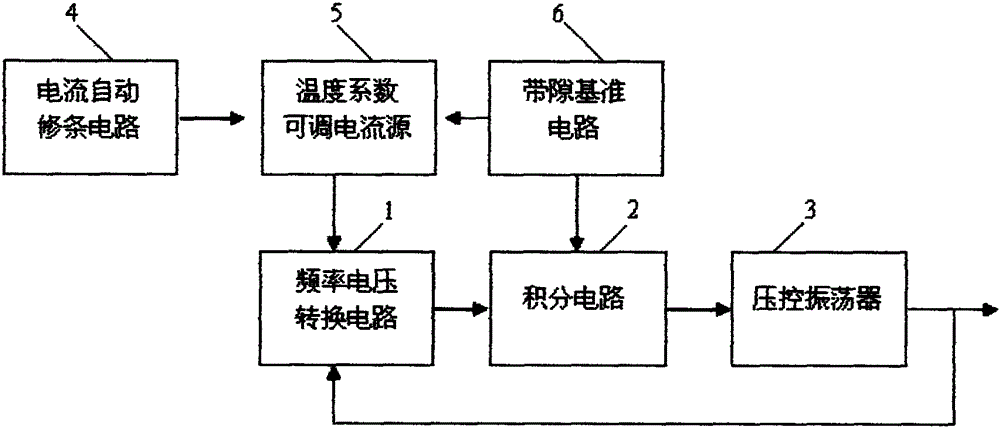

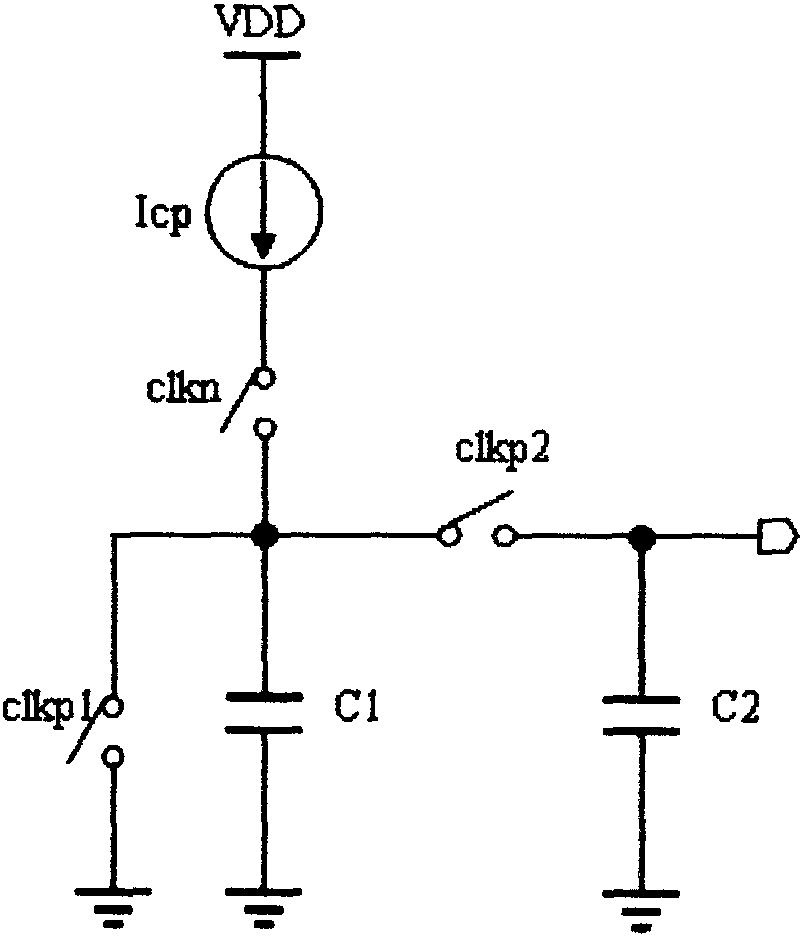

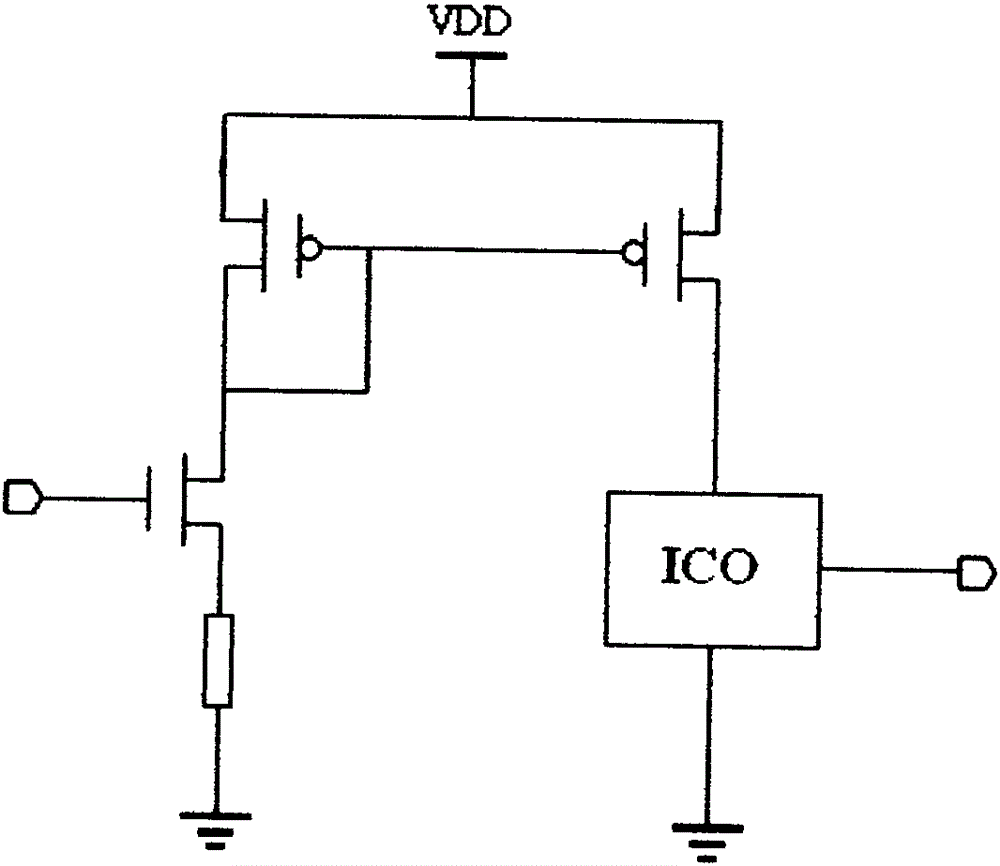

High precision on-chip clock oscillator based on cmos technology

ActiveCN102882471BImprove Noise PerformanceImprove temperature stabilityOscillations generatorsLoop controlElectronic systems

The invention discloses a complementary metal oxide semiconductor (CMOS)-process-based high-accuracy on-chip clock oscillator, which comprises a frequency voltage conversion circuit, an integral circuit, a voltage-controlled oscillator, an automatic current trimming circuit, an adjustable temperature coefficient current source and a band gap reference circuit, wherein the frequency voltage conversion circuit, the integral circuit and the voltage-controlled oscillator are sequentially connected into a closed loop structure. The frequency voltage conversion circuit, the integral circuit and the voltage-controlled oscillator form a closed loop control oscillator circuit, so that the output frequency of the oscillator circuit is controlled by the whole closed loop without the influence of process variations of MOS transistors. Due to the adoption of the closed loop, the oscillator circuit has high noise performance. In addition, a temperature compensation current source and the automatic current trimming circuit are adopted for the whole loop, so that the oscillator circuit is ensured to have high temperature and process stability. Moreover, the oscillator circuit is simple and high in clock accuracy, and an external quartz crystal oscillator of an electronic system can be replaced.

Owner:苏州锐控微电子有限公司 +1